spinor/spinand flash之高频通信延迟采样

SPI协议

对于spinor和spinand flash,其通信总线为SPI总线。

SPI有四种工作模式,对应不同的极性和相位组合

极性,一般表示为CPOL(Clock POLarity),即SPI空闲时时钟信号SCLK的电平(0:空闲为低电平; 1:空闲为高电平)

相位,一般表示为CPHA(Clock PHAse),即SPI在SCLK第几个边沿开始采样(0:第一个边沿采样; 1:第二个边沿采样)

四种模式为:

| CPOL | CPHA | |

|---|---|---|

| mode0 | 0 | 0 |

| mode1 | 0 | 1 |

| mode2 | 1 | 0 |

| mode3 | 1 | 1 |

SPI FLASH通信

spinor和spinand,一般都支持mode0和mode3。即都是在下降沿送数据,上升沿采样。

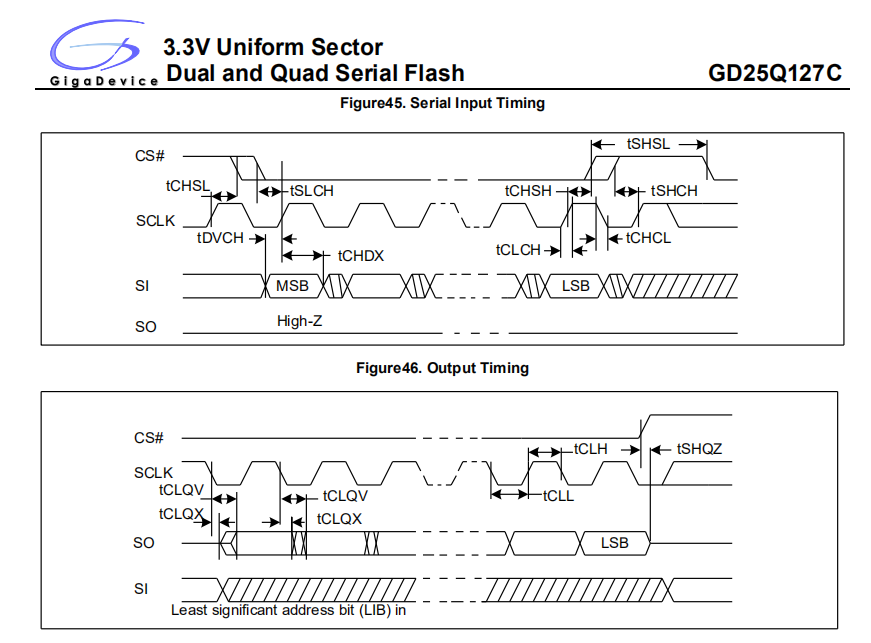

具体一点,在某次读数据的时候,主控端发出一个下降沿,flash收到后,就把数据准备好送到spi总线上,在接下来的上升沿时,主控端就对SPI的数据线进行采样,得到这个bit的数据是0还是1。

接着主控端又送出下降沿,flash收到后又送出1bit的数据,供主控在下一个上升沿的时候读取。

高频下的问题

上面描述的通信过程,一个沿触发送数据一个沿进行采样,一来一往配合默契,看起来没什么问题。

但其实这里面隐含了一个要求,就是flash必须能跟得上节奏,需要在收到主控的下降沿之后,迅速准备好数据,在下一个上升沿到来之前送到总线上。否则主控在下一个上升沿采样到的数据就是错的了。

这个在低频的时候,是没什么问题的,例如在5M的clock下,下降沿到上升沿,时间大概是100ns,这个时间足够flash准备好数据并送上总线了,轻轻松松。

但在更高的时钟频率下,flash就有压力了,在100M的clock下,下降沿到上升沿,时间大概是5ns。如果是104M, 133M等,那时间就更短了。

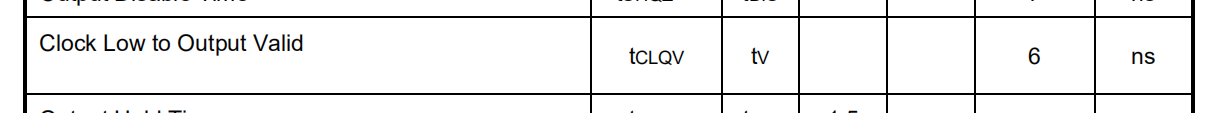

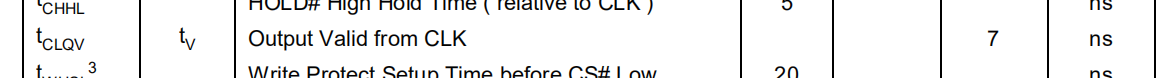

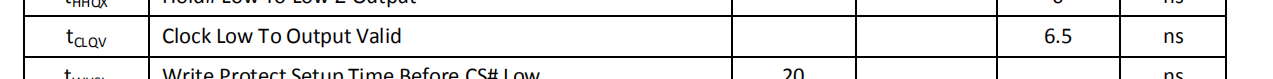

在这种时钟频率下,flash来得及送数据吗? 很遗憾,来不及,请看规格书

flash规格书标注的 Clock Low to Output Valid, 即从收到时钟下降沿到送出的数据有效,这个耗时就已经超过5ns了。

多找两家看看

看起来都差不多,100M下面,谁也满足不了这个5ns的时间要求。

如何解决

那既然flash无法准时送出数据,那主控在下一个上升沿就必然采样不到正确的数据了,怎么办?降低时钟频率吗

降低时钟频率当然可以解决问题,但还有另外的办法,那就是延迟采样。

主控知道在高频下,flash无法及时送出数据来,那没关系,我就晚一点再采样,等flash的数据到位之后再采样即可。

例如有些主控的SPI控制器可以配置,延迟半个周期采样或延迟一个周期采样,在100M的clock下,一个周期10ns。

那么不延迟的话,flash只有5ns的时间可以准备数据以及送数据,如果延迟半个周期采样,则有10ns,延迟1个周期,则有15ns。

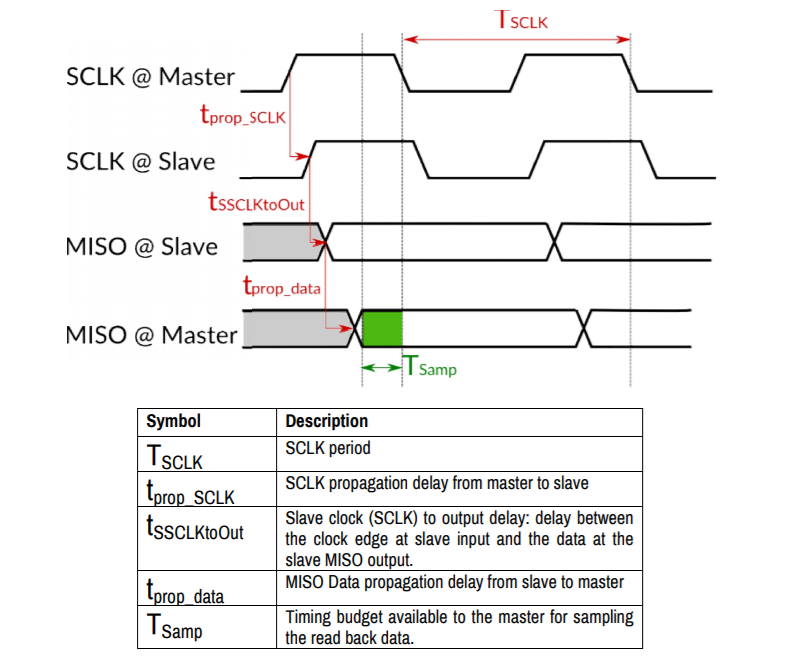

具体应该延迟多少,就得看实际情况了,因为我们刚刚只关注了flash标注的 Clock Low to Output Valid 的值,其实实际的延迟,还会受其他因素影响,例如从主控发出下降沿,到flash实际收到下降沿的延迟。flash发出数据,到主控实际能采样到数据的延迟,如果走线较长的话,这些也是不可忽略的。

例如这篇文章https://www.byteparadigm.com/files/documents/Using-SPI-Protocol-at-100MHz.pdf 的举例,就算上了信号传播的延迟,从里面截一张图大家看下,更多信息可以看原文,就不搬运了

本文链接,https://www.cnblogs.com/zqb-all/p/12153583.html

公众号: https://sourl.cn/A4yGae

浙公网安备 33010602011771号

浙公网安备 33010602011771号