简介

Quartus II design 是最高级和复杂的,用于system-on-a-programmable-chip (SOPC)的设计环境。 Quartus II design 提供完善的 timing closure 和 LogicLock™ 基于块的设计流程。Quartus II design是唯一一个包括以timing closure 和 基于块的设计流为基本特征的programmable logic device (PLD)的软件。 Quartus II 设计软件改进了性能、提升了功能性、解决了潜在的设计延迟等,在工业领域率先提供FPGA与mask-programmed devices开发的统一工作流程。

新建项目

1.新建一个文件夹,用你将要建的工程的名字命名,记住命名一定要相同,用英文命名

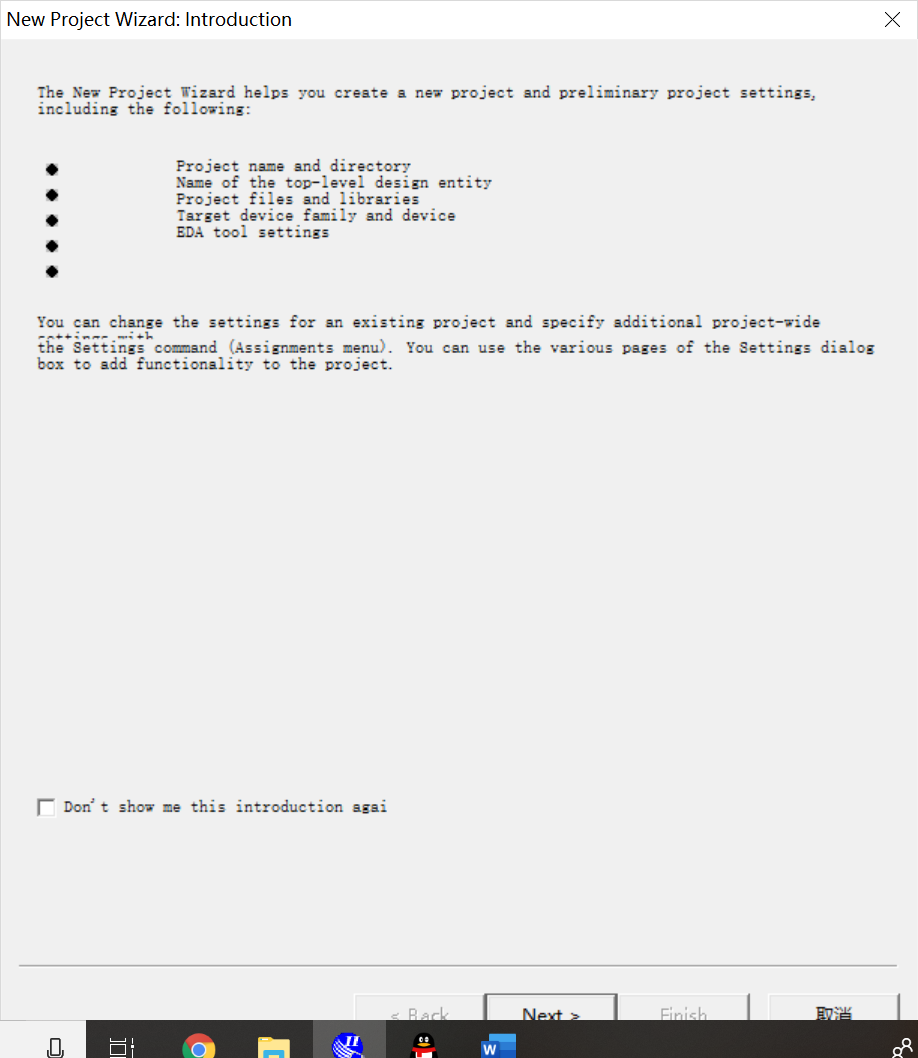

2.打开quartus,点击File->New Project Wizard

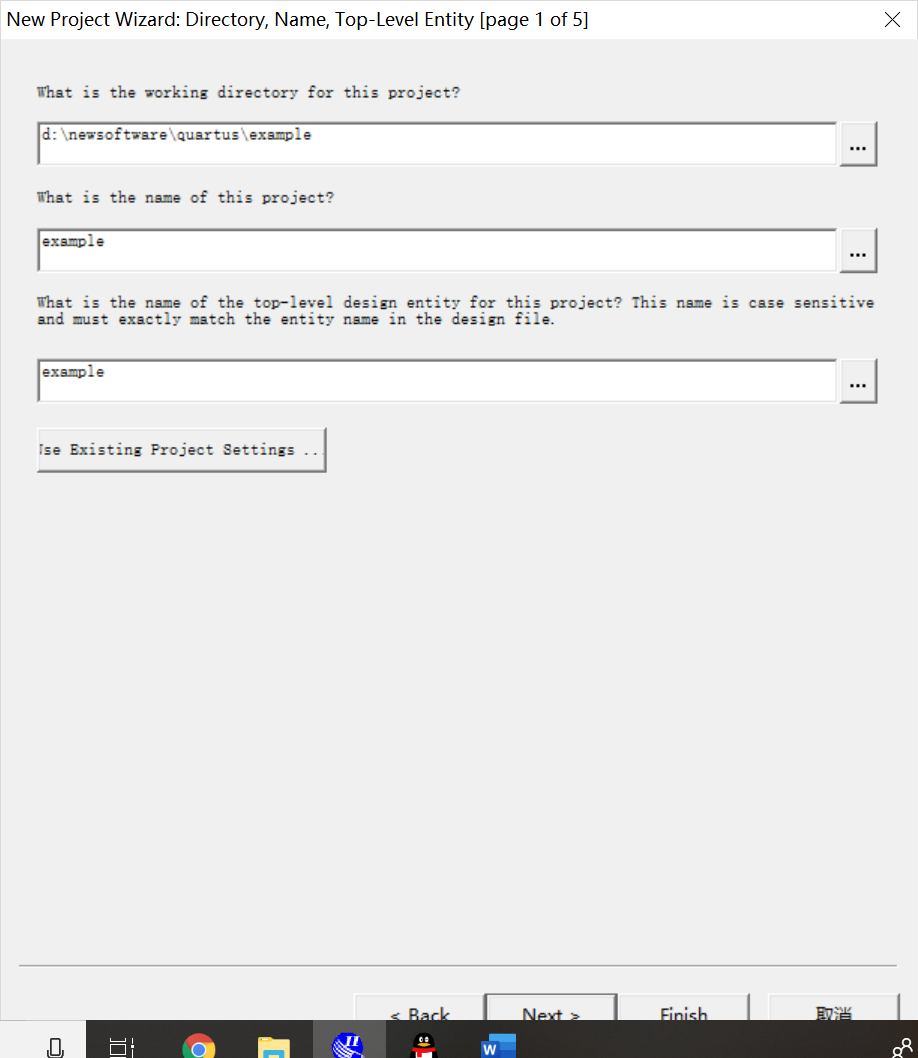

点击next->选择刚才建的文件夹的位置保存工程,工程的名字要与文件名一致->点击next

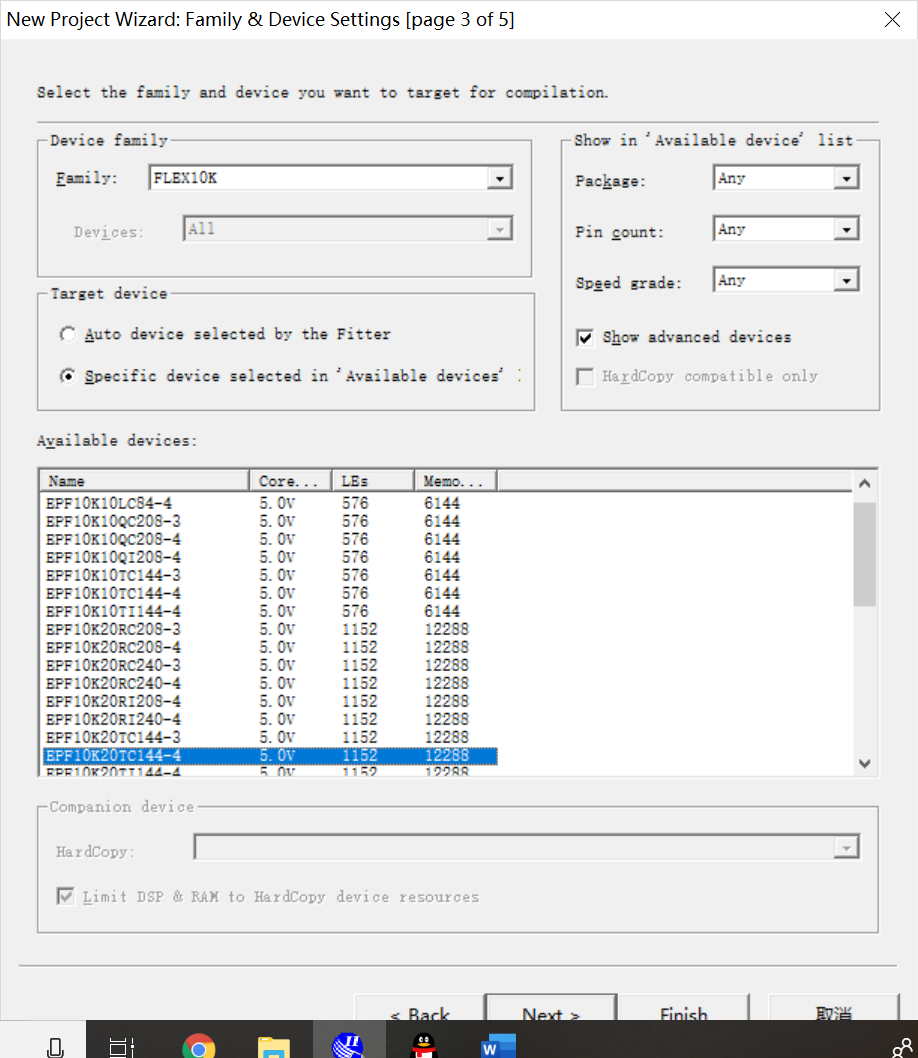

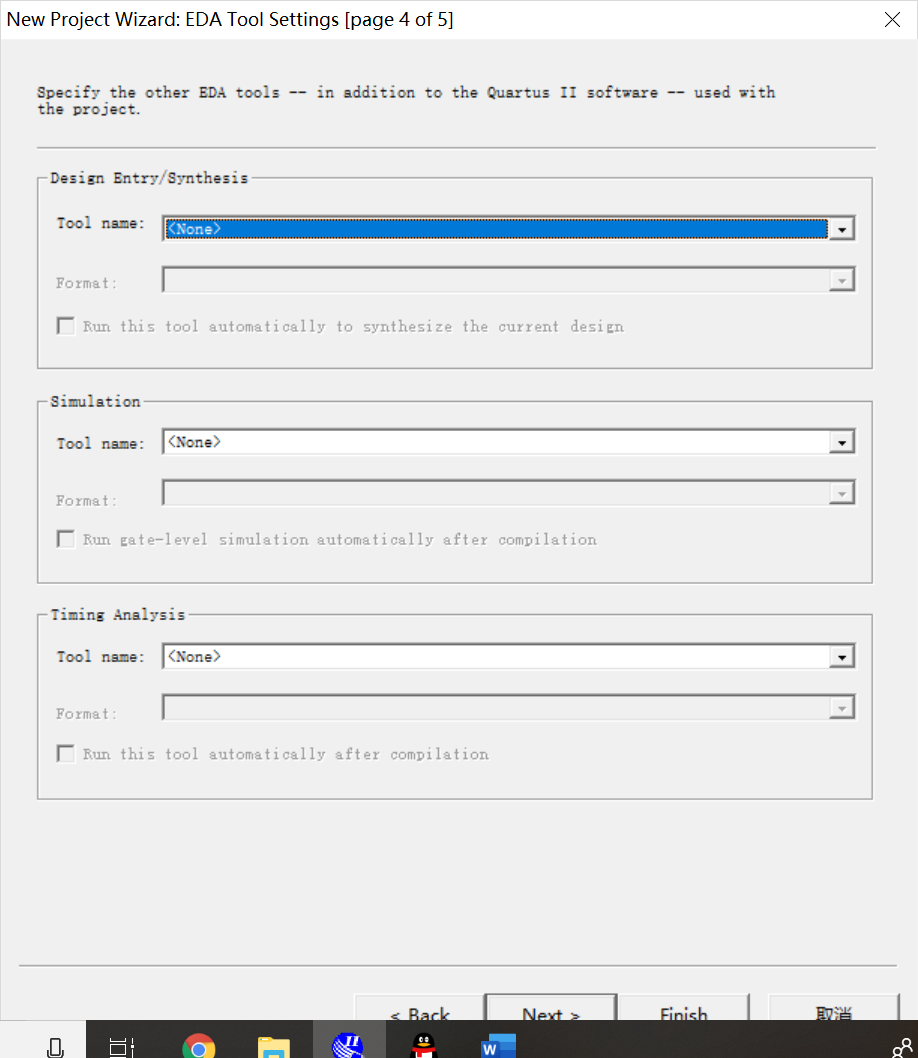

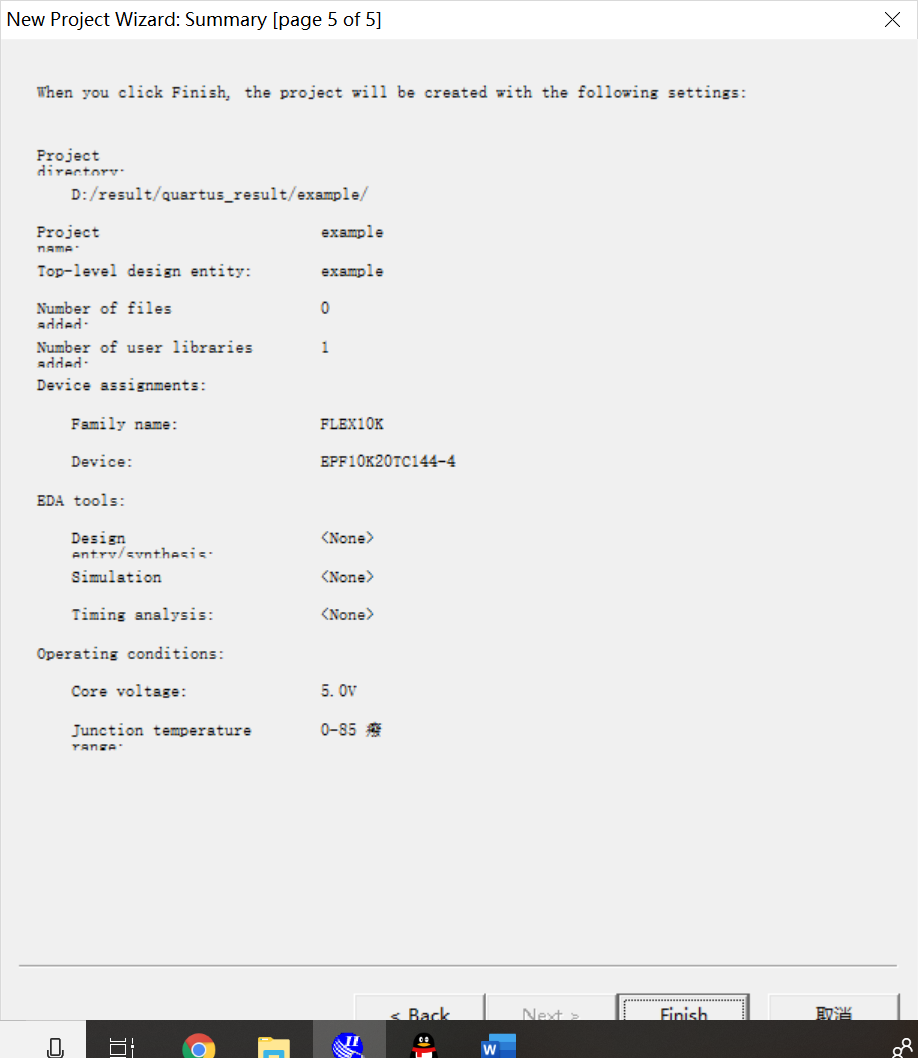

如果有要添加的文件添加即可->选择元器件的型号等参数->next->确认工程信息,Finish

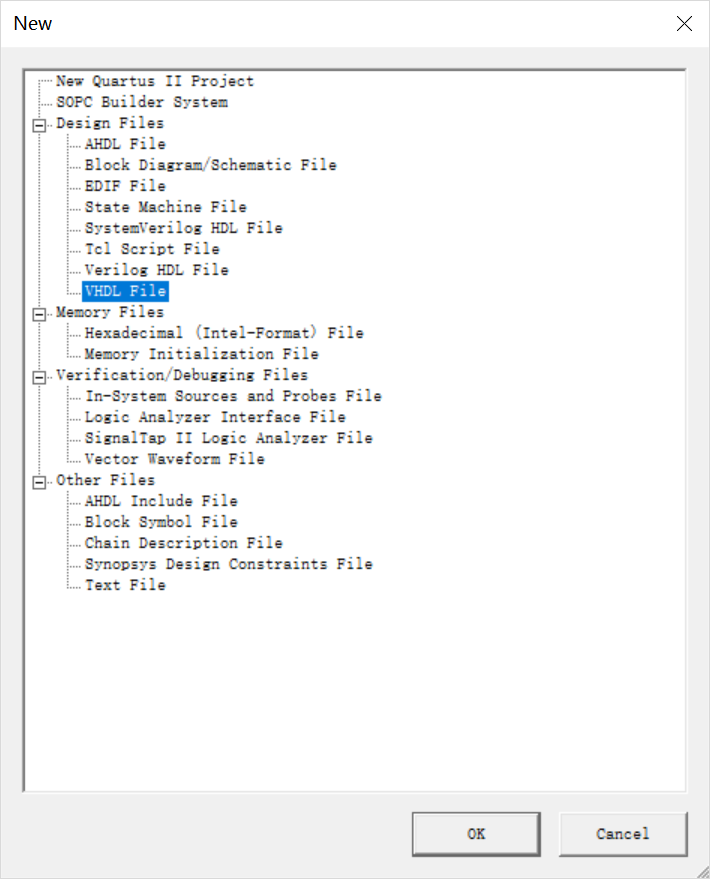

3.点击File->New->VHDL File->OK

编写VHDL语句,如下图为一个4-1的多路复用器的结构描述

保存编译

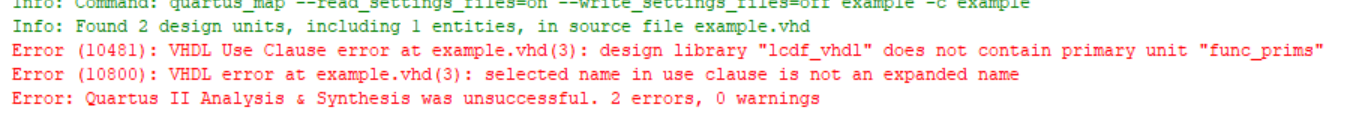

出现错误

lcdf_vhdl库包含了func_prims包,该包用VHDL语言描述了基本的逻辑门、锁存器和触发器,我们通过all调用该包中的所有内容

添加这个包有三种方法

(1)在创建工程时添加

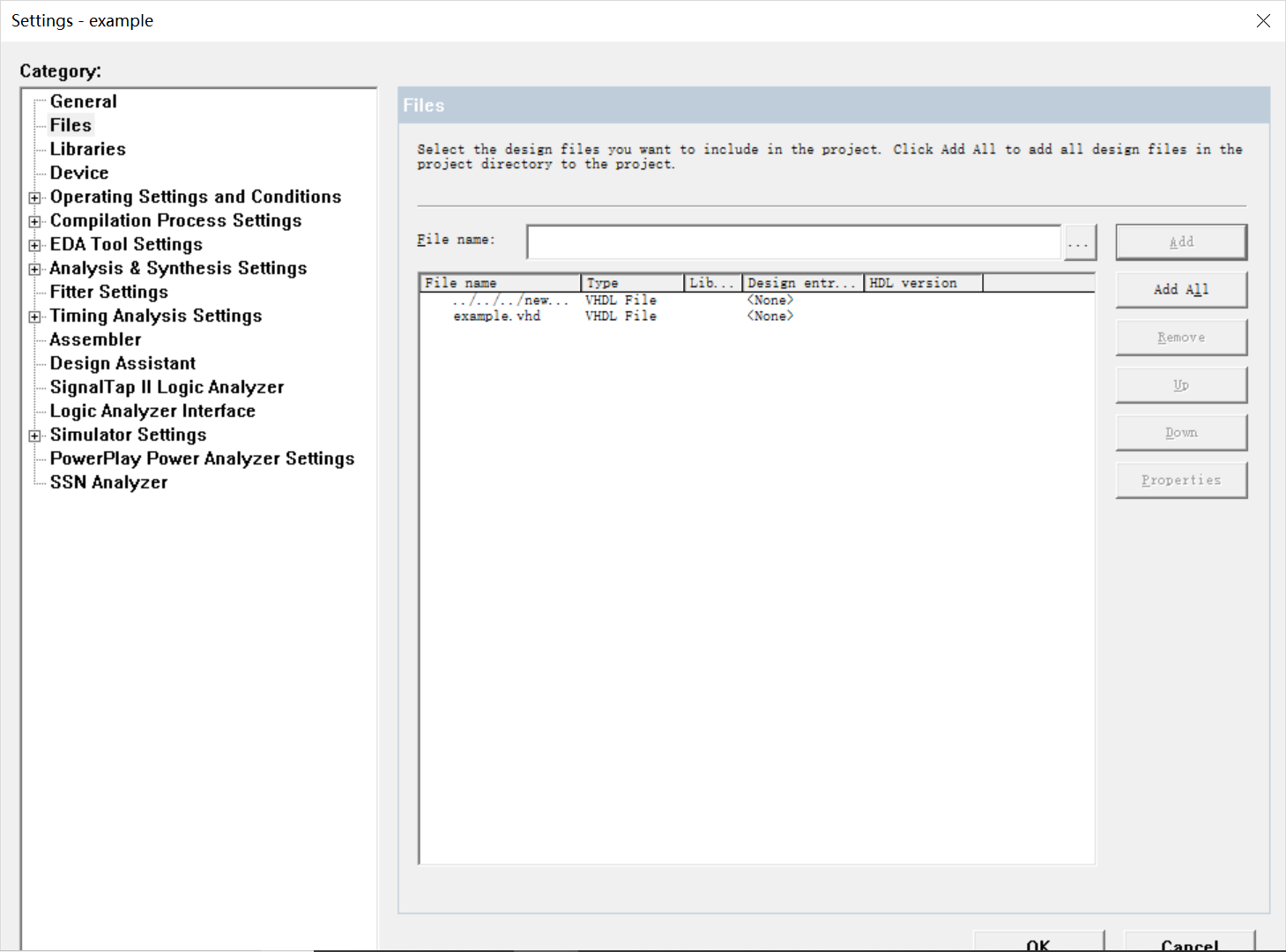

(2)编译前添加

左键点击Files->add/remove file in project->File->添加即可

(3)assighments->settings->File->添加即可

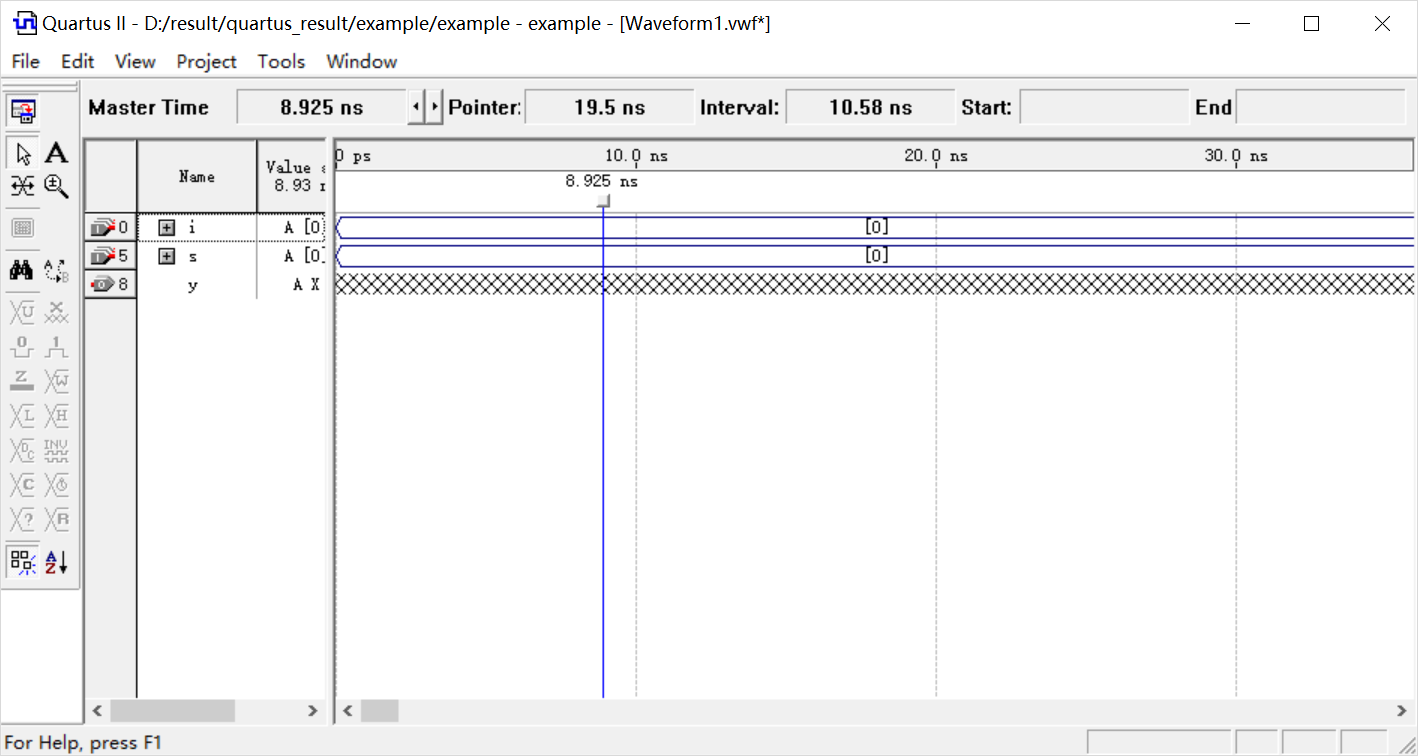

绘制波形图

点击File->New->Vector Waveform File

在空白处点击左键

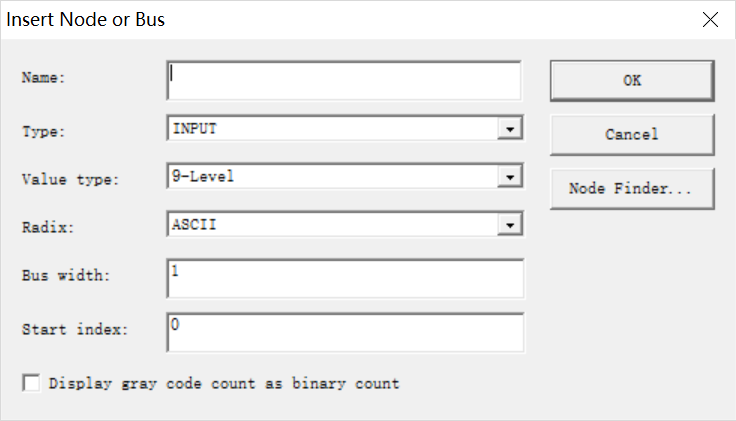

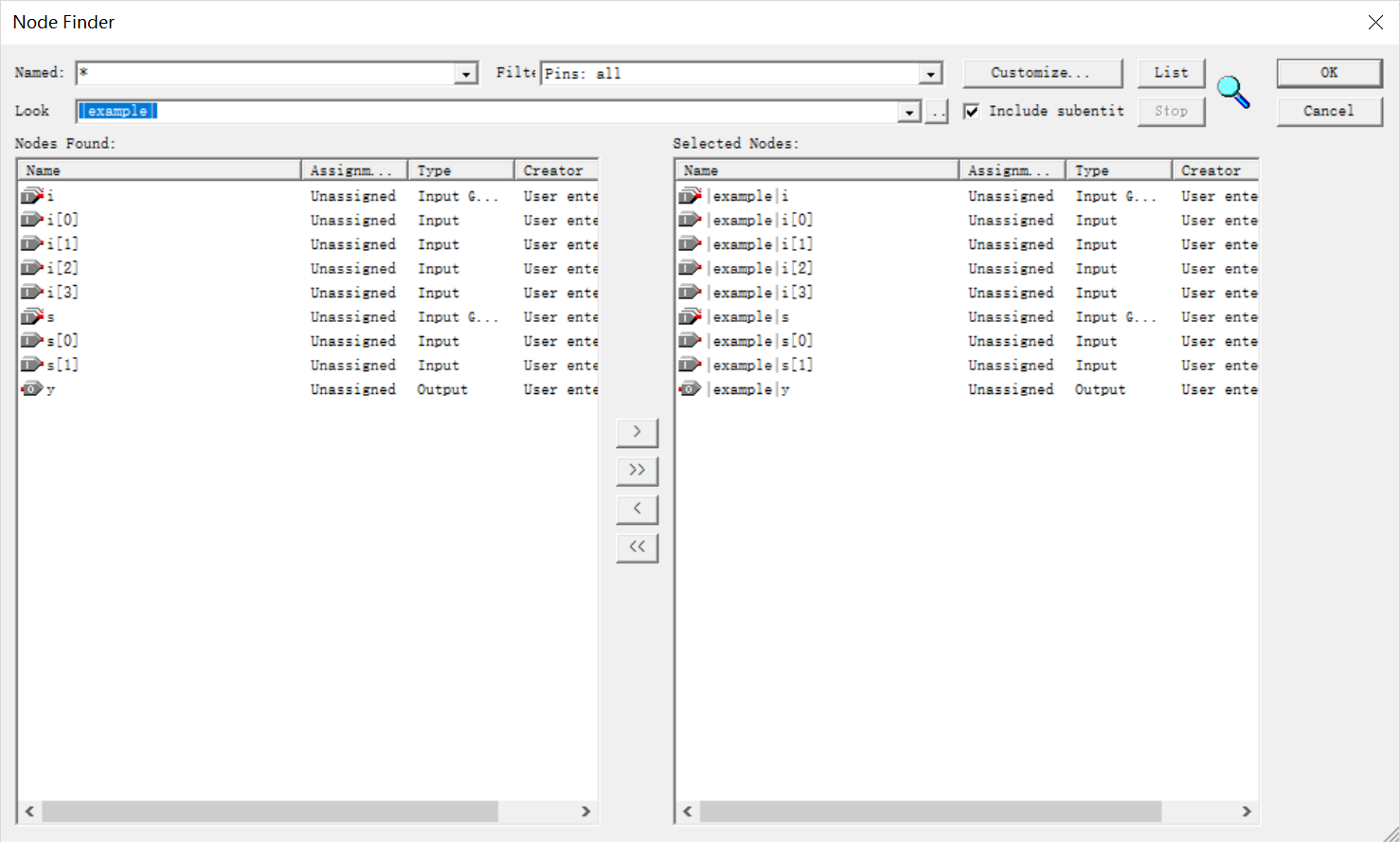

点击Insert->Insert Node or Bus->Node Finder

选择Pin:all->list->">>"->OK->OK

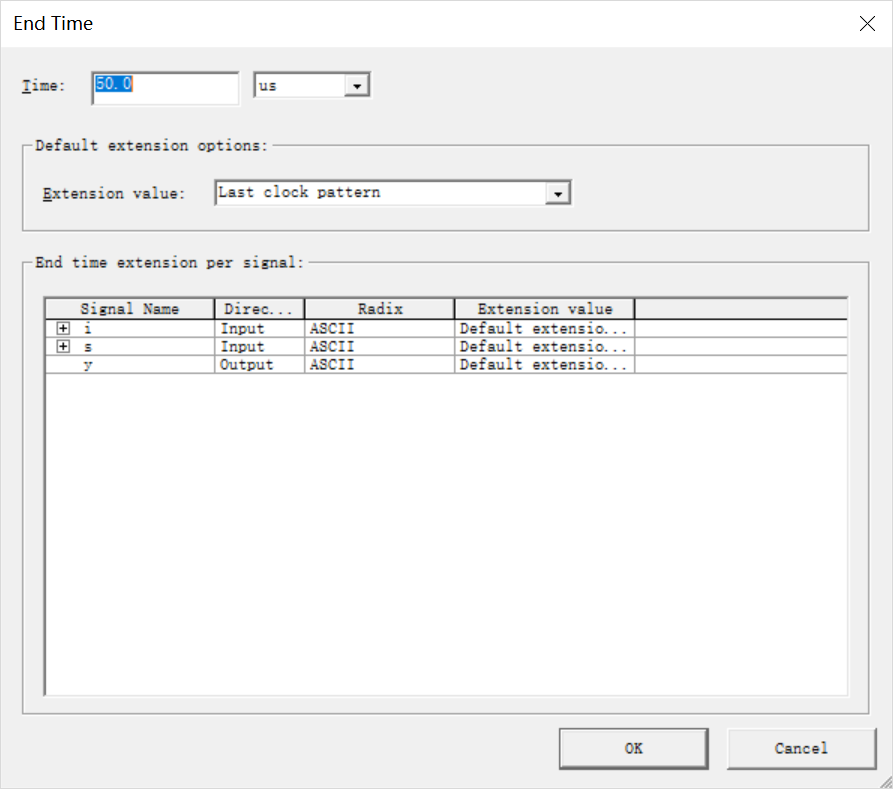

Edit->End Time设置截止时间

设置节点波形

(中间应该还有几步)

保存

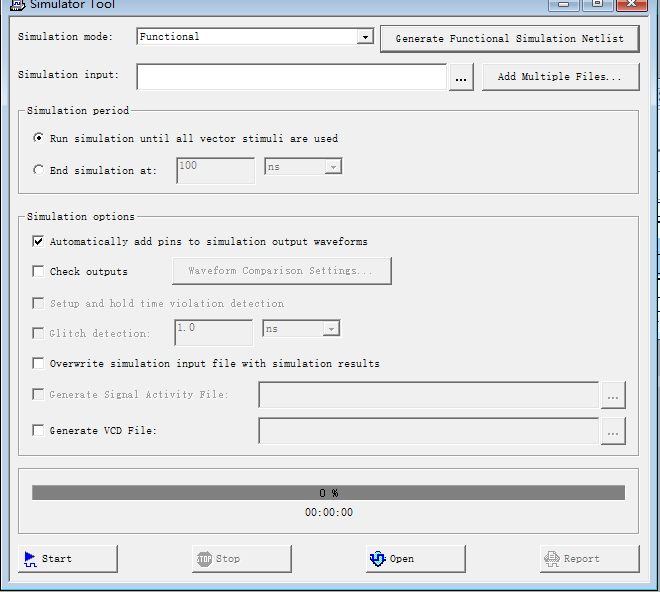

功能仿真

Processing->Simulate Tool

Simulation mode设置成Functional,点击Generate Functional Simulate Netlist->Start开始仿真->点击report得到波形

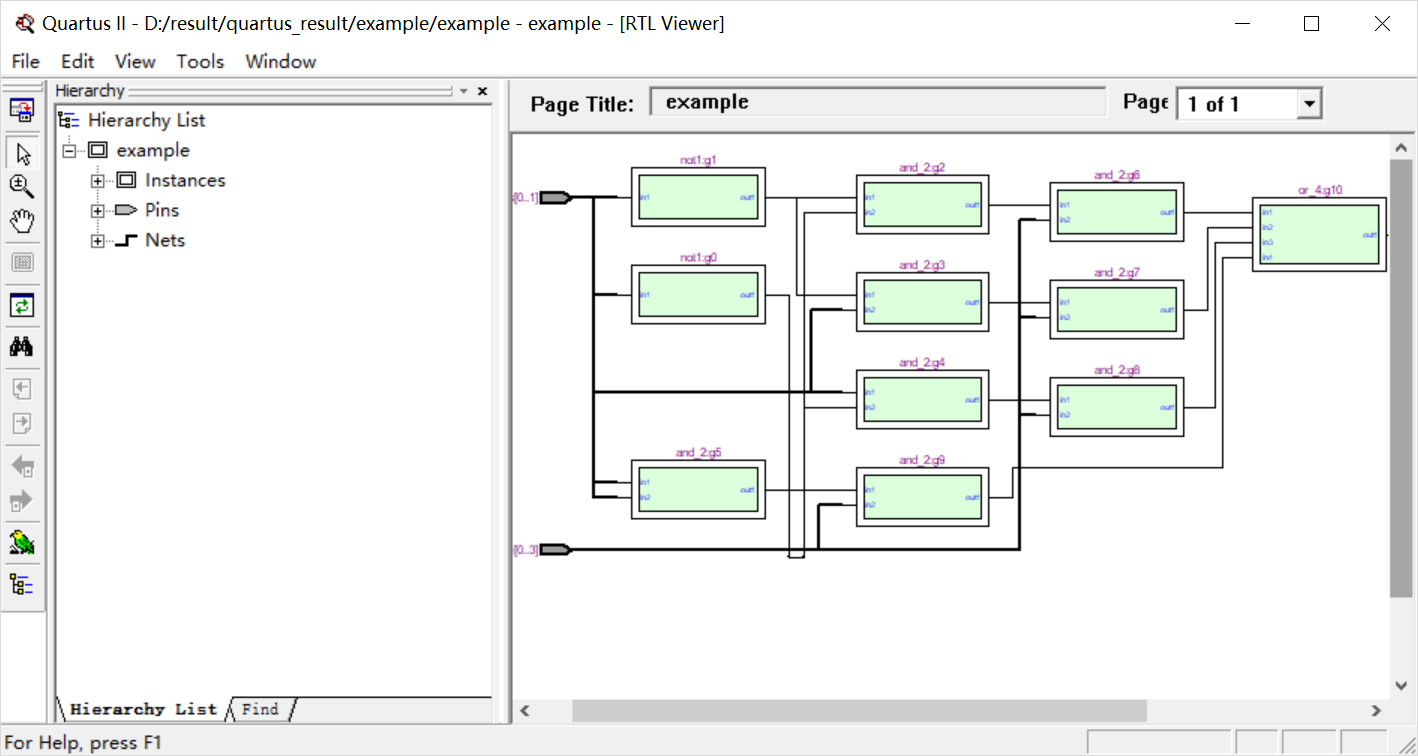

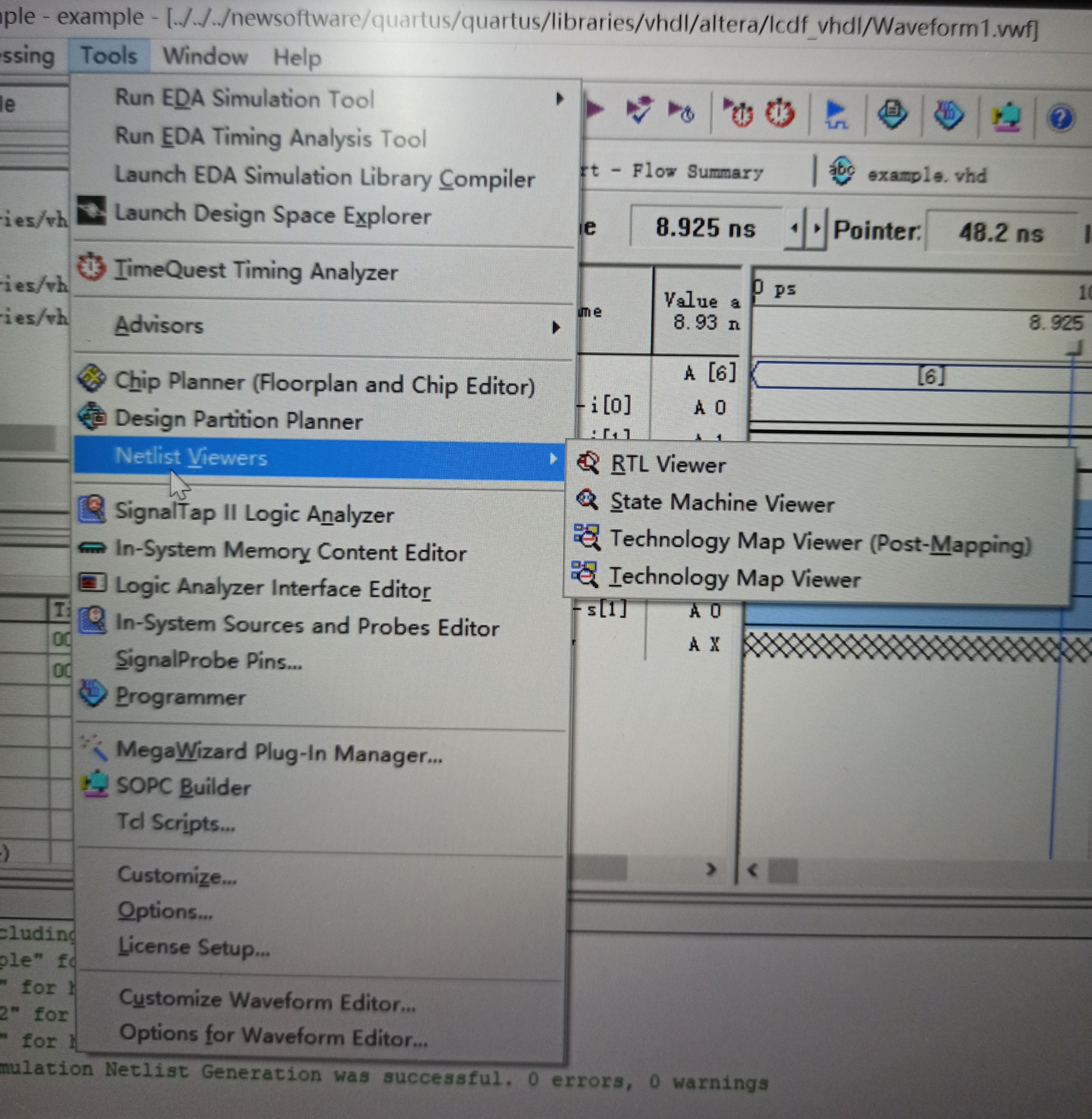

生成电路图

Tools->Nerlist Viewers->RTL Viewer

当当当当,睡觉