SPI由于接口相对简单(只需要4根线),用途算是比较广泛,主要应用在 EEPROM,FLASH,实时时钟,AD转换器,还有数字信号处理器和数字信号解码器之间.即一个SPI的Master通过SPI与一个从设备,即上述的那些Flash,ADC等,进行通讯.而主从设备之间通过SPI进行通讯,首先要保证两者之间时钟SCLK要一致,互相要商量好了,要匹配,否则,就没法正常通讯了,即保证时序上的一致才可正常讯.而这里的SPI中的时钟和相位,指的就是SCLk时钟的特性,即保证主从设备两者的时钟的特性一致了,以保证两者可以正常实现SPI通讯.

时钟的极性Polarity和相位Phase,和一些英文简写标识如下:

- CKPOL(Clock Polarity)=CPOL=POL=Polarity=(时钟)极性

- CKPHA(Clock Phase)=CPHA=PHA=Phase=(时钟)相位

- SCK=SCLK=SPI的时钟

- Edge=边沿,即时钟电平变化的时刻,即上升沿(rising edge)或者下降沿(falling edge)

一个时钟周期内,有两个edge,分别称为前沿(第一个边沿)和后沿(第二个边沿):

- Leading edge=前沿=第一个边沿,对于开始电压是1,那么就是1变成0的时候,对于开始电压是0,那么就是0变成1的时候;

- Trailing edge=后沿=第二个边沿,对于开始电压是1,那么就是0变成1的时候(即在第一次1变成0之后,才可能有后面的0变成1),对于开始电压是0,那么就是1变成0的时候;

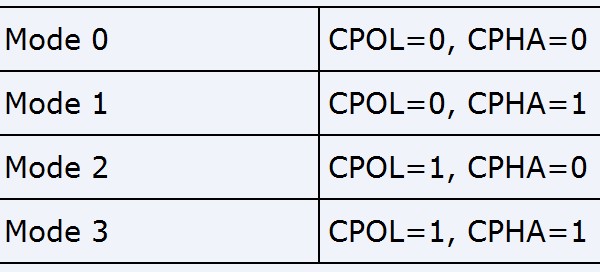

CPOL和CPHA,分别都可以是0或时1,对应的四种组合就是:

下面详细介绍.

CPOL极性

先说什么是SCLK时钟的空闲时刻,其就是当SCLK在发送8个bit比特数据之前和之后的状态,于此对应的,SCLK在发送数据的时候,就是正常的工作的时候,是有效active的时刻.其英文精简解释为:Clock Polarity = IDLE state of SCK.

SPI的CPOL,表示当SCLK空闲idle的时候,其电平的值是低电平0还是高电平1:

- CPOL=0,时钟空闲idle时候的电平是低电平,所以当SCLK有效的时候,就是高电平,就是所谓的active-high;

- CPOL=1,时钟空闲idle时候的电平是高电平,所以当SCLK有效的时候,就是低电平,就是所谓的active-low;

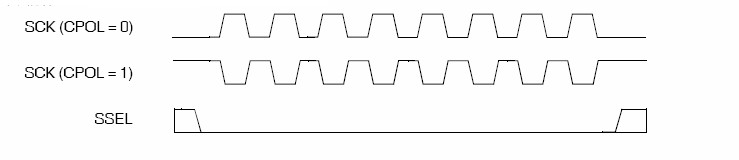

如上图所示,(CPOL=0)的SCK波形,它有(传输)8个脉冲,而在脉冲传输前和完成后都保持在低电平状态.此时的状态就是时钟的空闲状态或无效状态,因为此时没有脉冲,也就不会有数据传输.同理得出,(CPOL=)1的图,时钟的空闲状态或无效状态时SCK是保持高电平的.

CPHA相位

首先说明,capture strobe=latch=read=sample,均示数据采样,数据有效的时刻.相位,对应数据采样是前沿还是后沿,0标识第一个边沿(前沿),1标识第二个边沿(后沿).

对于:

CPHA=0,表示第一个边沿:

对于CPOL=0,idle时候的是低电平,第一个边沿就是从低变到高,所以是上升沿;

对于CPOL=1,idle时候的是高电平,第一个边沿就是从高变到低,所以是下降沿;

CPHA=1,表示第二个边沿:

对于CPOL=0,idle时候的是低电平,第二个边沿就是从高变到低,所以是下降沿;

对于CPOL=1,idle时候的是高电平,第一个边沿就是从低变到高,所以是上升沿;

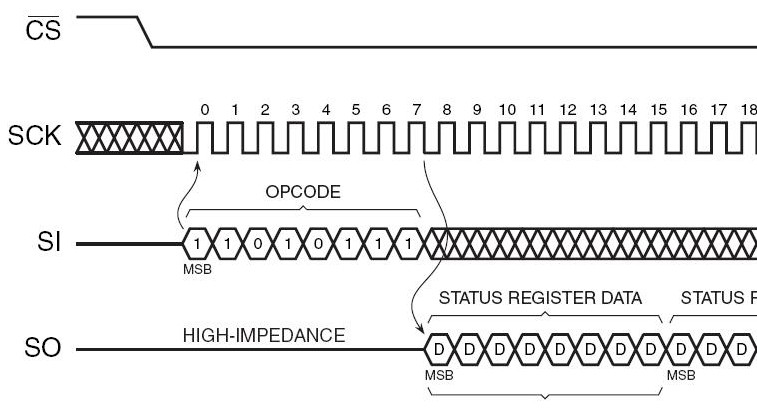

我们看上面的图,发现数据SI是对应SCK的第一个时钟沿,再仔细看,数据是在SCK的第一个时钟边沿保持稳定[数据被采样捕获],在下一个边沿改变[SCK的下降沿数据改变]因此我们得出结论:该系列FLASH是[数据在第一个时钟沿被采样捕获]或[数据在SPCK起始边沿捕获,在SPCK下一个边沿改变]

如何判断CPOL和CPHA?

如果起始的SCLK的电平是0,那么CPOL=0,如果是1,那么CPOL=1,然后看数据采样时刻,即时序图数据线上的数据那个矩形区域的中间所对应的位置,对应到上面SCLK时钟的位置,对应着是第一个边沿或是第二个边沿,即CPHA是0或1.(对应的是上升沿还是还是下降沿,要根据对应的CPOL的值,才能确定).

最后来看一下S3C2440的SPI的CPOL和CPHA,结合前面讲的理论知识,下面的图就很好理解啦!

本文转自:http://blog.csdn.net/ce123_zhouwei/article/details/6923293

浙公网安备 33010602011771号

浙公网安备 33010602011771号