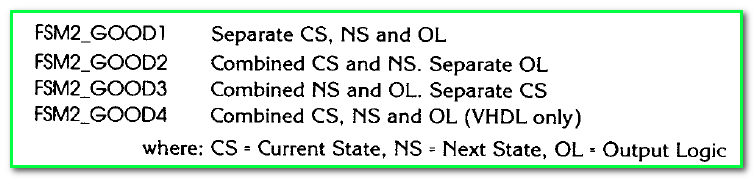

在状态机设计时,可以将状态机分为三个部分,

从上图可知OL没有和CS放在一起的,除了第四种,但是第四种中的CS处理中用了变量赋值的方法,信号值的变化在一个Process内完成,因此,可以放在一起。其他的三种由于采用的时信号赋值的方式。

如果在一个process里面既要完成状态变换,又要完成输出结果,这样会产生额外的latch。

进一步的解释可以是:

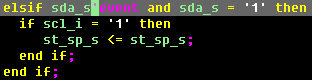

如图

该结构可以产生一个D触发器。

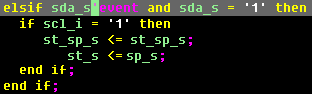

如图,却可以产生两个D触发器。

但是,我们在做状态机的跳转时只需要一个触发器就可以了,其他的可以在状态转换完成后用组合逻辑进行输出逻辑的运算。即在边沿触发的结构中白瞎了一个D触发器。

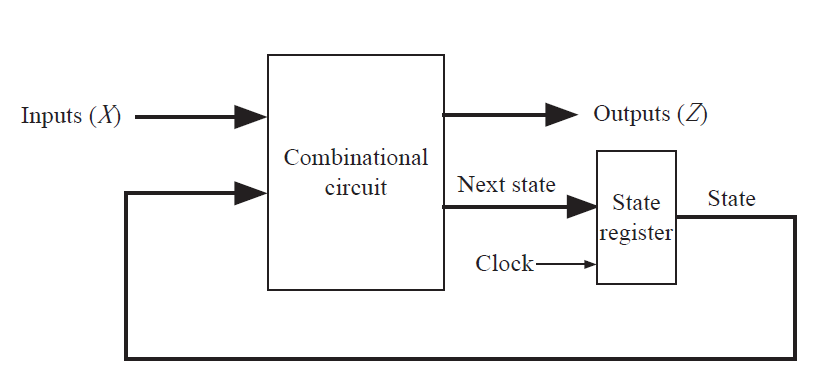

接着,如图所示

组合逻辑给出了下一个状态,而状态寄存器用于将该状态锁住,并等待下下个状态。

也就是说,组合逻辑既可以用于处理输入信号,也可以用于输出信号,还可以提供下一个状态的值。但状态机最好就是不要产生输出信号。