IIC特点

- 主从通信

- 高速IIC总线一般可达400kbps以上,用于低速设备通信

- 传输距离短,一般设计PCB板时,外设嵌入pcb

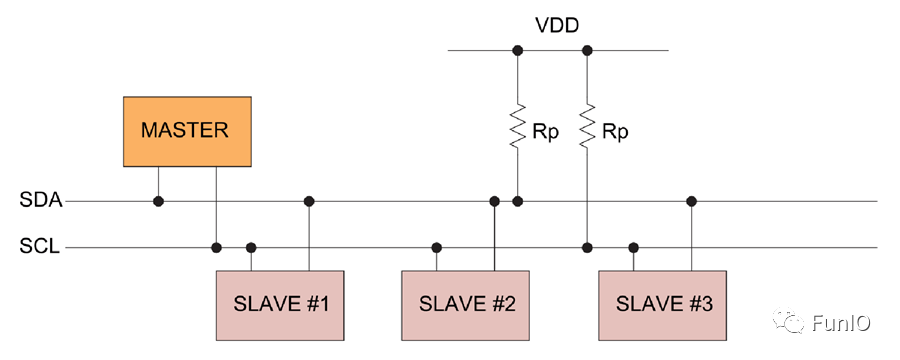

- 半双工通信,同一时间只能单项通信,任意时刻只能有一个主机

- IIC总线上可连接128个设备,但0x00地址不使用,因此127个设备,但实际设计情况,建议不超过8个,因为总线电容不能超过400pF

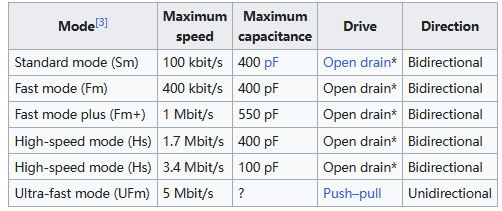

- 速率和模式:I2C支持不同的通信速率,通常有

- 标准模式(100 kbit/s)

- 快速模式(400 kbit/s)

- 快速plus模式(1Mbit/s)

- 高速模式(3.4 Mbit/s)

- 超高速模式(5 Mbit/s)

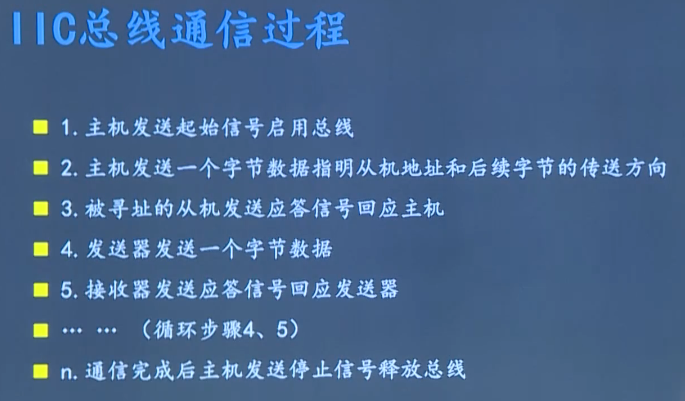

IIC通信流程

四个信号

归纳上方流程,发现有四个信号:

- 起始信号-第一步

- 发送信号-第二、四步

- 应答信号-第三、五步

- 终止信号-最后一步

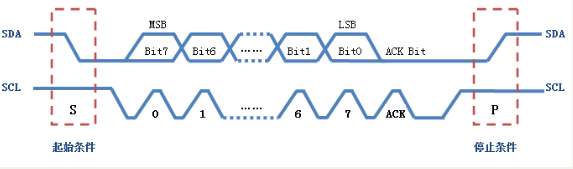

4种信号都是使用SCL(时钟线)和SDA(数据线)的电平状态,来表示和传输

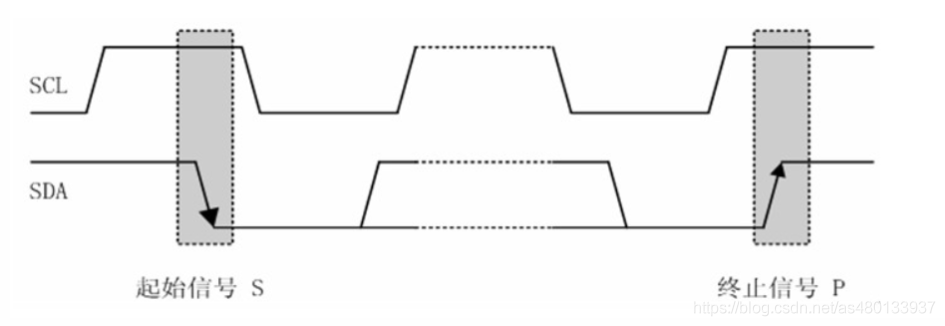

起始信号S&&停止信号P

SCL和SDA在空闲状态下,都是高电平

起始信号

SCL为高电平时,SDA为高电平向低电平跳变,广播IIC总线上的所有设备,开始传输数据

停止信号

SCL 为高电平时,SDA 由低电平向高电平跳变,广播IIC总线上的所有设备,这一次数据传输已经结束,可以开始下一次传输。

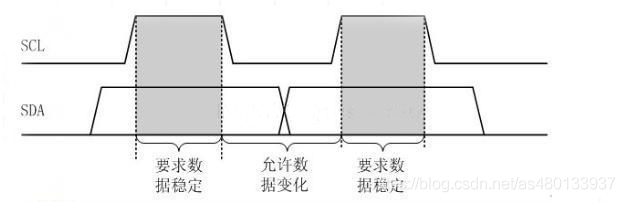

发送信号&&接收信号

读写状态

如何定义0和1?

- SCL为低电平,SDA为写状态,设备可以改变SDA的高低电平状态

- SCL为高电平,SDA为读状态,设备可以读取SDA的高低电平状态,此时SDA的状态要求稳定、

真实数据

数据传输

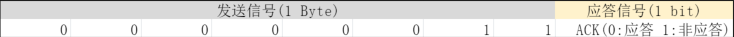

1. 发送信号

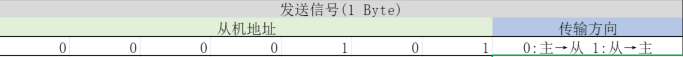

寻址数据

IIC通信流程第二步,主机广播想要通信的从机地址,IIC总线上所有设备接受到这个地址后,与自己的地址作比较,若相同,则应答

note:传输方向决定第四、五步的发送器和接受器

eg: 假设 传输方向 0:主\(\to\)从

第四步发送器:主机发送器

第五步接收器:从机接收器

第4+2n步和第5+2n步重复以上两个步骤,方向不可更改

信息数据

IIC通信流程第四步: 发送1Byte的信息

2. 应答信号

- 0: 应答

- 1: 非应答,即异常终止

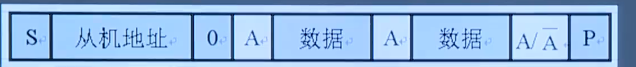

IIC的常见使用方式

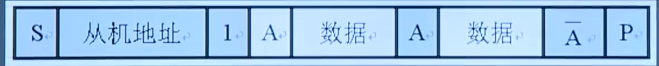

1. 主机给从机发数据

值得注意的是IIC通信终止方式:

- 主机终止:主机发送P

- 从机终止:主机发送数据后,从机不应答,主机发送P

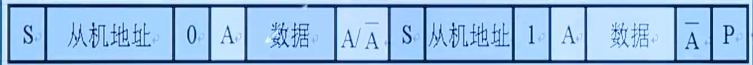

2. 从机给主机发数据

- 主机终止:从机发送数据后,主机不应答,从机也就不再发送数据,主机发送P

3. 主从机交互式发数据

note: S和P之间为一次传输,在此期间,其它设备无法抢占总线,同时主机可以再次发送寻址信号,改变传输方向。

芯片设计

电气特性

总线高低电平定义

一般总线上认为,低于 \(0.3 Vdd\) 为低电平,高于 \(0.7Vdd\) 为高电平。

对于电源电压固定为5(1±10%)v的器件,其逻辑电平规定如下:

- Vilmax=1.5v(最大输入低电平)

- Vihmax=3v(最大输入高电平)

对于能够适应电源电压范围较宽的器件(如cmos类),其逻辑电平规定如下:

- Vilmax=0.3vdd(最大输入低电平)

- Vihmax=0.7vdd(最大输入高电平)

传输速度模式

上拉电阻

由于I2C接口采用Open Drain机制,器件本身只能输出低电平,无法主动输出高电平,只能通过外部上拉电阻RP将信号线拉至高电平。因此I2C总线上的上拉电阻是必须的,所以在SCL总线和SDA总线上,加上"上拉电阻",I2C的上拉电阻可以是1.5K,2.2K,4.7K。

上拉电阻放置建议

应安置在OD输出端附近。当I2C总线上主从器件(Master & Slave)两端均为OD输出时,电阻放置在信号路径的中间位置。当主设备端是软件模拟时序,而从设备是OD输出时,应将电阻安置在靠近从设备的位置

上拉电阻的分析,为什么要有一个合适的上拉电阻?

-

上拉电阻过小,总线上电流增大,端口输出低电平增大。

-

上拉电阻过大,上升沿时间增大,方波可能会变成三角波

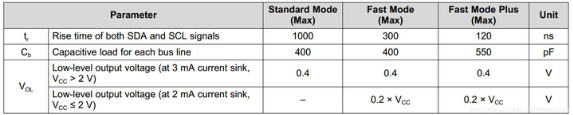

上拉电阻的计算公式

最大电阻

符号定义: 上升沿时间 tr 、负载电容 Cb 、标准上升沿时间 0.8473 有关。

最小电阻

符号定义: 电源 \(Vdd\) 电压、GPIO 的最大输出电压 \(V_{OL}\)、 GPIO的自己最大电流 \(I_{OL}\) (3mA)有关

电源电压限制了上拉电阻的最小值 ;负载电容(总线电容)限制了上拉电阻的最大值

负载电容: IIC总线挂的设备越多,电容也就越大。

关于计算Rp的基本参数如下表所示:

1、标准模式:0~100KHz,上升沿时间 tr = 1us

2、快速模式:100~400KHz,上升沿时间 tr = 0.3us

3、快速plus模式:up to 3.4MHz,上升沿时间 tr = 0.12us

实例计算

在实际的应用中,决定电阻的所有变量中,总线的负载电容很难精确地计算,只能大致的估计范围。

因此通常在应用中,一般是根据估计和经验选择一个临时上拉电阻,然后根据波形的测试效果去选择合适的电阻。

在一些系统中,假设10k,4.7k,2k电阻都能满足要求,那么就要在速度和功耗中按照设计需求进行取舍,上拉电阻越大意味着功耗越低,同时要牺牲部分上升时间。上拉电阻小意味着功耗高,同时意味着总线的扩展能力更强,

由此公式,假设 Vdd 是 3.3V 供电,Cb 总线电容是200pF(虽然协议规定负载电容最大 400pF,实际上超过 200pF 波形就很不好,我们以 200pF 来计算)

标准模式-100kbit/s

快速模式-400kbit/s

举例说明下I2C总线基本参数是Cb=200pF,VDD=3.3V,计算Rp值。

根据以上计算,Rp应选择966.667Ω–1.77KΩ之间的即可,具体阻值根据实际情况来确定。

快速模式plus-1Mbit/s

由于电源电压限制了上拉电阻的最小值 ;负载电容(总线电容)限制了上拉电阻的最大值,所以三种模式下的\(Rp(min)\)一样

一般芯片驱动电流为\(3mA\),所以上拉电阻\(\frac{3V}{R_p} < 3mA\),即\(R_p>1K\)

推荐:不同速率采用的电阻一般有以下几种:1.5K、2.2K、4.7K,总线速率越高,总线上拉电阻要越小。一般应用采用4.7K,如果挂多个设备,为保证通信速率,选择2.2k。

功耗问题

上拉电阻与总线的电容形成了RC,高速时将直接影响通讯,所以功耗与速度,二者只可得其一。

电阻越小,功耗越高。

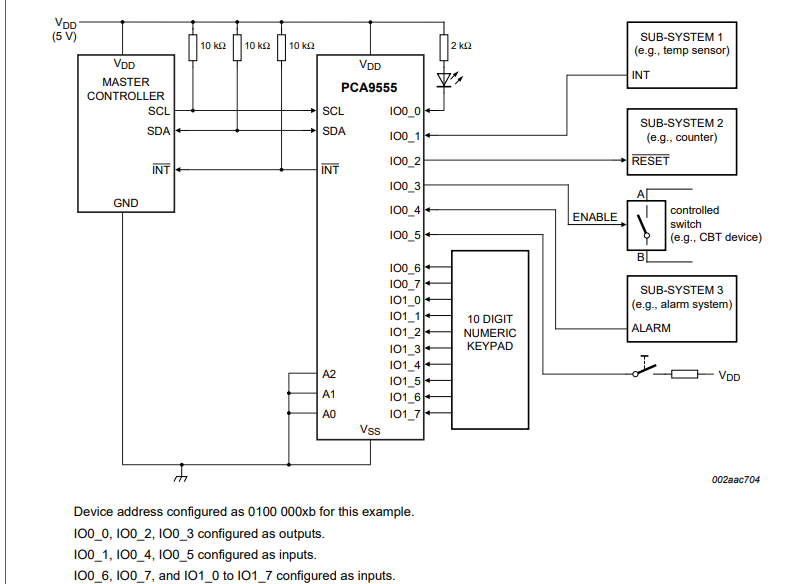

1. IIC扩展IO芯片

芯片: PCA9555PW

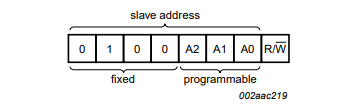

IIC的地址引脚

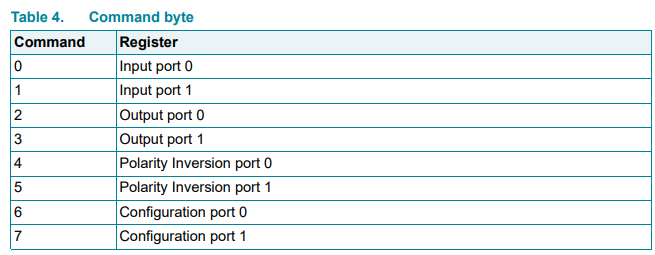

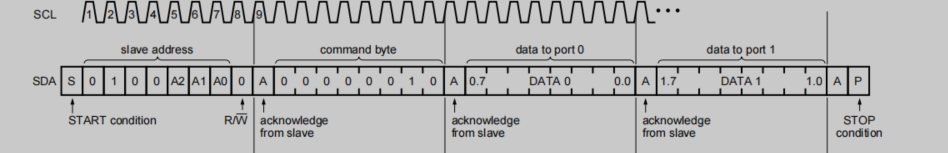

指令形式

[s] [从机地址+方向] [command byte] [内容] [p]

值得注意的是

意思是,command=2,如果内容中第一个字节发送给output port 1,那么下一个字节将发送给output port 0 ,也就是说下一个字节的数据必将发给同一对寄存器(eg: output port0 && output port1)中的另一个。

command=

cmmond=2

2. IIC连接显示屏

3. IIC连接存储器(EEPROM)

4. IIC连接实时时钟(RTC)

5. I2C/SPI至UART

芯片: SC16IS740/750/752

参考

[1] B站-创客学院视频

[3] 一文详解I2C总线 - -电子发烧友网 (elecfans.com)

[4] IIC上拉电阻的选择与计算-电子发烧友网 (elecfans.com)

[5] I²C - Wikipedia

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· TypeScript + Deepseek 打造卜卦网站:技术与玄学的结合

· 阿里巴巴 QwQ-32B真的超越了 DeepSeek R-1吗?

· 【译】Visual Studio 中新的强大生产力特性

· 10年+ .NET Coder 心语 ── 封装的思维:从隐藏、稳定开始理解其本质意义

· 【设计模式】告别冗长if-else语句:使用策略模式优化代码结构