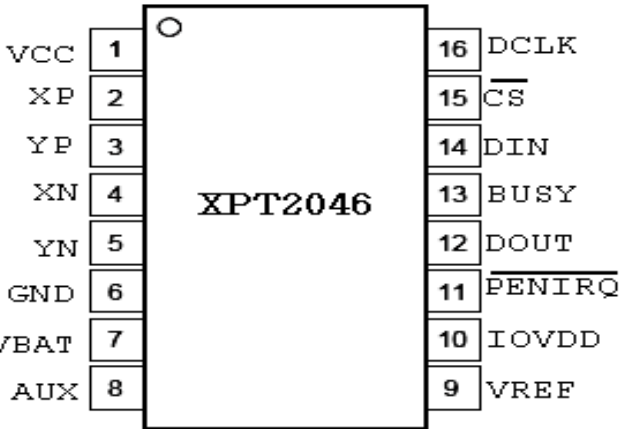

1.管脚以及封装,在此仅列举一种TSSOP-16

2.引脚说明

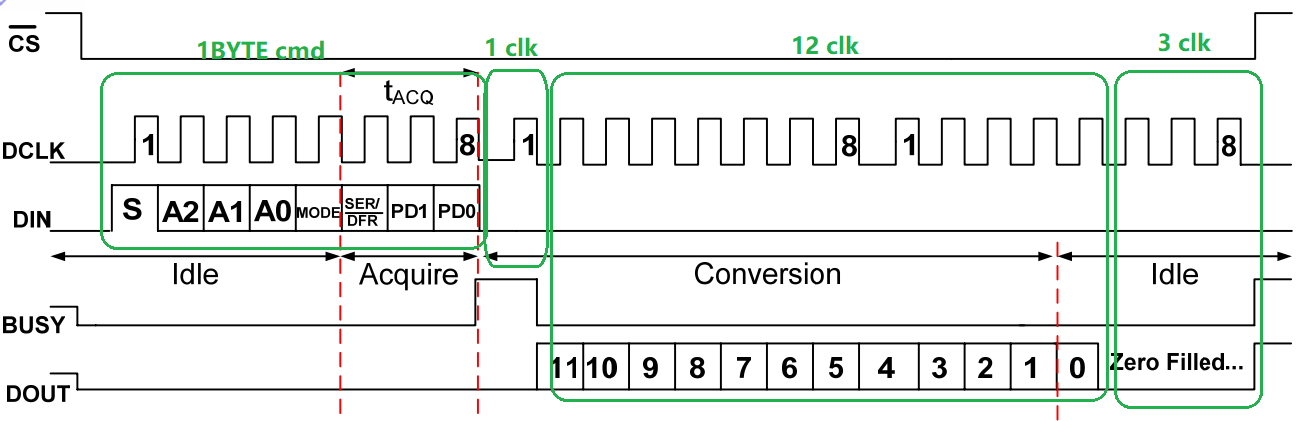

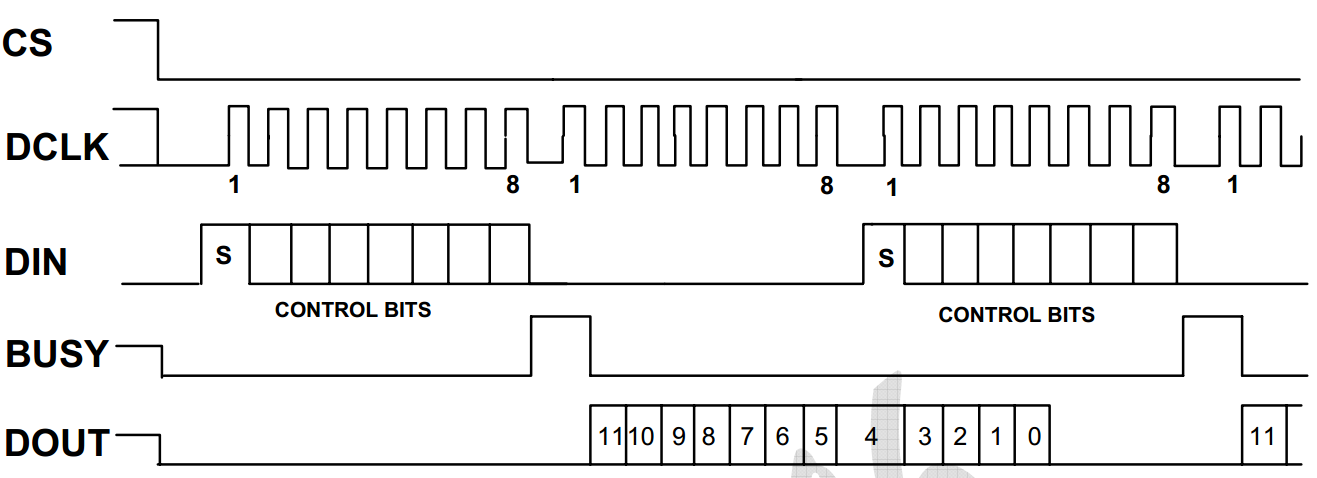

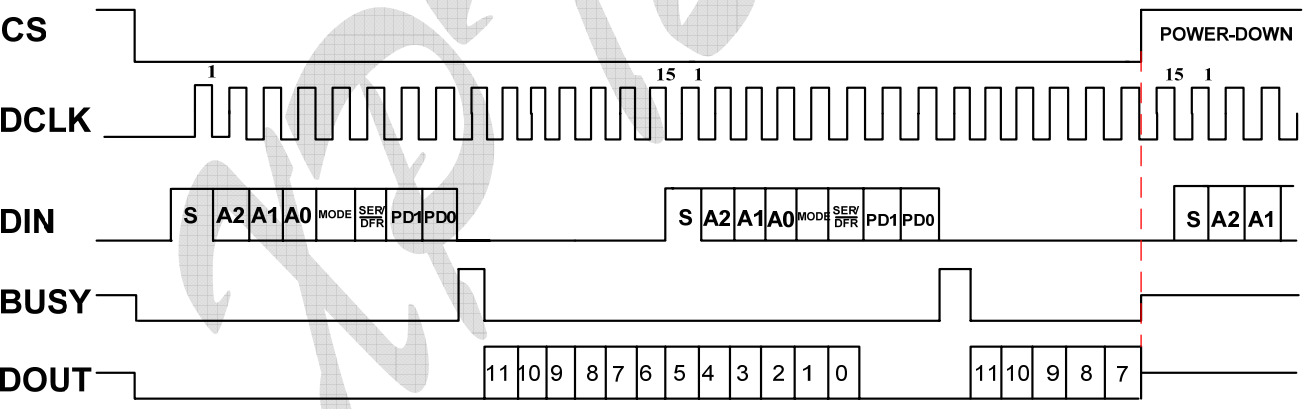

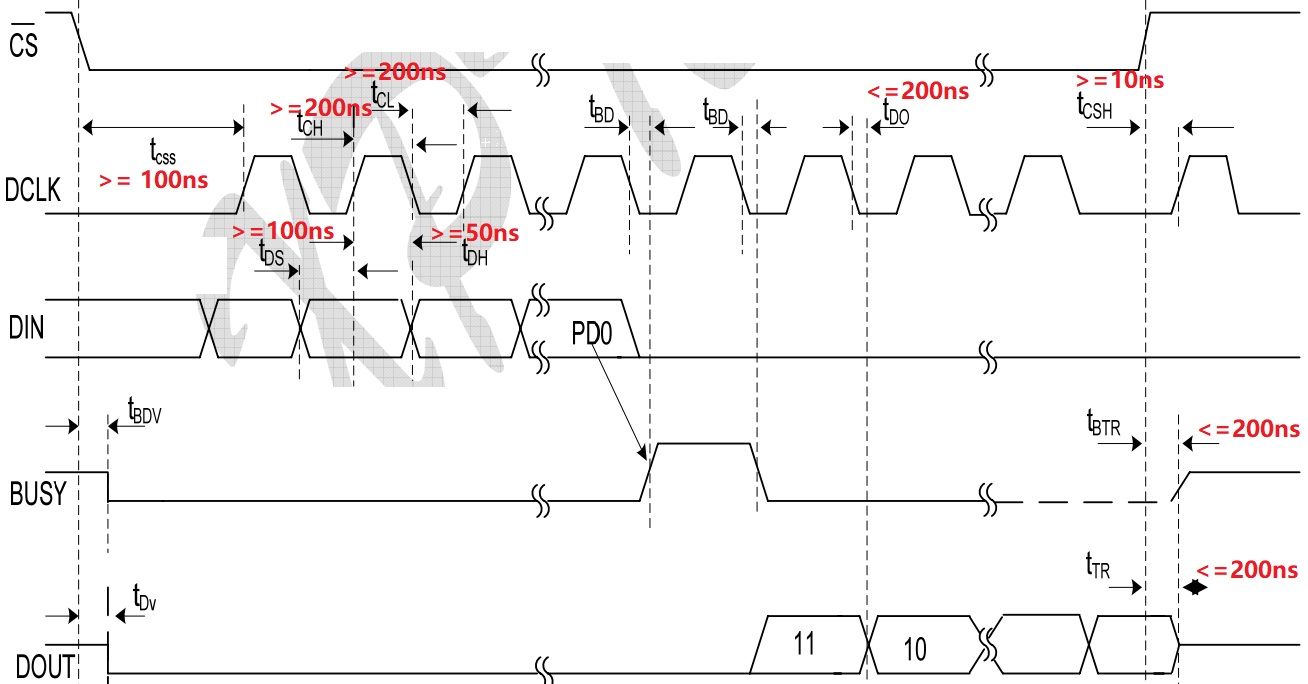

3.驱动时序

(1). 标准时序,一共24 个clk传输完成。

(2).16bit传输,如下所示,也就是说,当到第17个clk,可以启动下一次转换。

(3).15bit传输,如下所示,也就是说,当到第16个clk,可以启动下一次转换。

(4)时序参数:

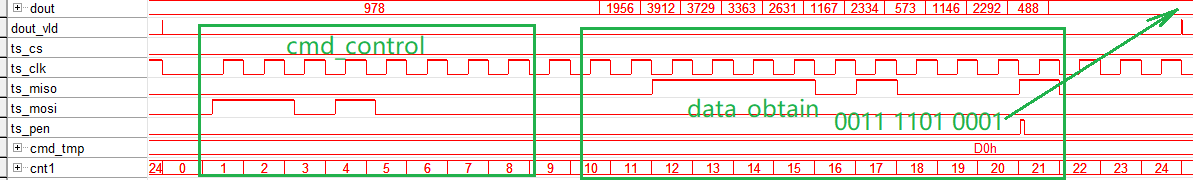

4.测试效果[]

如上图所示:首先通过MOSI发送0xD0的命令码,之后等待一个ts_clk,然后采集12bit的数据,最终通过dout和dout_vld指示出来。欢迎大家一起交流,Q群:912014800。

浙公网安备 33010602011771号

浙公网安备 33010602011771号