PS:字丑,禁止转载!!!

首先先写出大概的流程,然后是一些教材的理论知识总结,最后是进行lab2的一些流程概述。

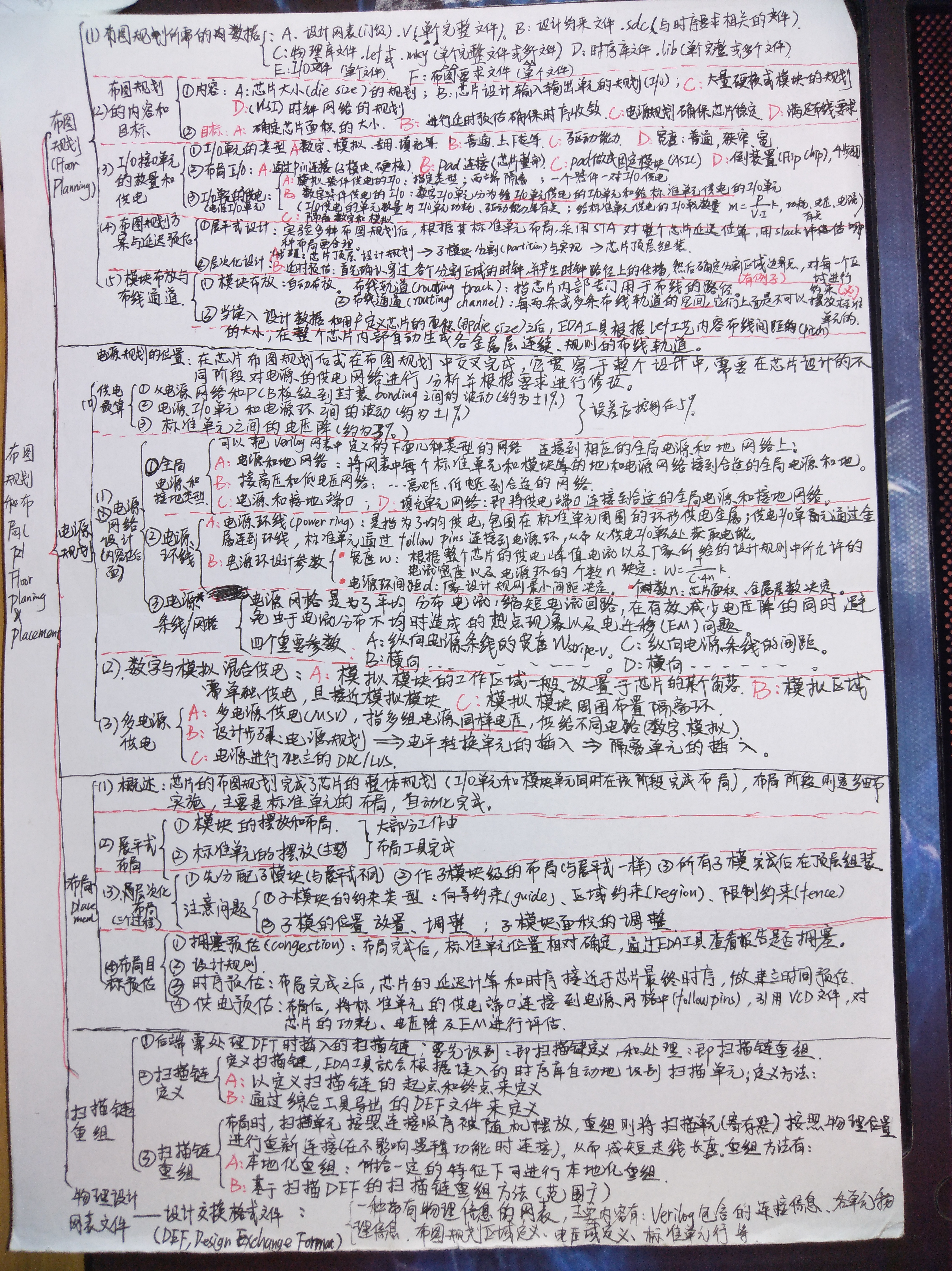

教材的理论知识总结主要是:数字集成电路物理设计学习总结——布图规划和布局

-->数据准备(设置)、加载设计并切换到floorplan模式

--> 创建拐角(Corner)和电源地(P/G)单元并定义他们pad的位置

-->创建floorplan

-->在电源/接地信号和I / O焊盘,宏和标准单元的所有电源/接地引脚之间建立“逻辑”连接

-->创建pad的电源环,保存电源环创建后的设计

-->验证当前虚拟平面放置策略选项是否具有默认设置

-->设置sliver 的尺寸,防止标准单元放置在宏单元之间的狭窄通道

-->使用“无层次结构重力”(选项)来执行 时序驱动的虚拟平台放置

-->进行宏单元布局约束

-->检查设置

-->所有宏单元周围设置10微米的硬限制边距

-->再次进行宏单元布局,锁定所有的宏,保存IO、宏单元布局规划后的设计

-->在宏单元周围创建P/G环

-->电源网络综合:对核心电源环、宏单元环、垂直以及水平环带进行约束、提交电源计划、连接所有宏单元上的电源引脚,并创建标准单元电源轨道(power rail)、保存这一阶段的设计

-->检查时序

-->写出DEF文件

-->为布局做准备而创建第二遍(布局规划)设计

上面是理论知识,下面是lab实践:

首先就进行数据设置,数据建立(设置)之后,保存为orca_setup

数据设置的过程在lab2实验中是没有详细叙述的,也就是说只给出了数据建立的结果:orca_setup

本次workshop实验需要准备/用到的数据为:

需要说明的是,圈圈的文件,在数据设置阶段就已经准备好了,其他方框的则是本次实验需要准备的。

下面就是正式过程了:

一、加载设计

启动ICC后,加载orca_setup这数据设置阶段产生的阶段设计,然后执行时序优化的控制脚本:

source scripts/opt_ctrl.tcl

然后在layout窗口中切换到design planning模式下:

File --> Task --->Design Planning

二、初始化平面图(floorplan),也是创建布局规划

1、创建拐角(Corner)和电源地(P/G)单元并定义他们pad的位置:

因为逻辑综合的网表里面没有上面的这些物理单元,我们需要自己创建,才能进行放置他们的位置,创建只要执行下面的脚本:

source –echo scripts/pad_cell_cons.tcl

pad_cell_cons.tcl脚本里面的内容主要是:

·创建Corners pad和power/group pads

·定义Corner pad 的位置

·定义signal pad 和 power pad的位置(主要是分为左边、右边、顶层和底层)

2、初始化floorplan

需要注意的是,icc2013.3以后(包括),初始化floorplan不能用initial_floorplan,而是用create_floorplan(也就是进行布局规划).

3、插入pad fillers,填充pad之间的间隙

执行命令:

source ./scripts/insert_pad_filler.tcl

这个脚本文件主要定义要插入的filler cells

4、在电源/接地信号和I / O焊盘,宏和标准单元的所有电源/接地引脚之间建立“逻辑”连接(无物理布线),也就是执行前面数据设置中没有进行的第6步:

source –echo scripts/connect_pg.tcl

5、创建pad的电源环:

create_pad_rings

6、保存电源环创建后的设计

save_mw_cel –as floorplan_init

三、将连接到IOpad的宏单元进行预布置(也就是布置好宏单元到核心区)

这里可以通过手动,也可以用脚本进行:

source –echo scripts/preplace_macros.tcl

这个脚本就是进行对三个宏单元的位置进行规划

四、执行虚拟平面放置

1、验证当前虚拟平面放置策略选项是否具有默认设置:

report_fp_placement_strategy (个人理解也就是查看各种放置默认信息)

2、设置sliver 的尺寸,防止标准单元放置在宏单元之间的狭窄通道(sliver size <10)中:

set_fp_placement_strategy -sliver_size 10

3、使用“无层次结构重力”(选项)来执行 时序驱动的虚拟平台放置(以确保“逻辑层次结构”不会影响此非层次结构或平面布局的放置):

create_fp_placement –timing_driven -no_hierarchy_gravity

上面的这个命令的效果就是把宏单元的位置放好(在核心区域上)

4、把一些宏转换成数组,电源和接地带和宏单元环的布线可以更容易。将宏单元置于尽可能接近芯片的边缘,将宏尽可能多地组合在一起、打开虚拟IPO以模仿时序优化(并防止不必要的布局优化)、限制某些RAM的合法布局方向,上面的四个操作通过执行脚本完成:(宏单元布局约束脚本)

source –echo scripts/macro_place_cons.tcl

5、检查设置:

report_fp_placement_strategy

report_fp_macro_options

6、 所有宏单元周围设置10微米的硬限制边距。 这样容易在宏单元周围创建P / G环,并避免拥塞以及宏单元周围的信号布线DRC错误:

source -echo scripts/keepout.tcl

7、再次进行宏单元布局:

create_fp_placement -timing_driven -no_hierarchy_gravity

可以进行拥塞分析

8、锁定所有的宏:

set_dont_touch_placement [all_macro_cells]

9、保存IO、宏单元布局规划后的设计:

save_mw_cel -as floorplan_placed

五、在宏单元周围创建P/G环

P/G环的创建方式(或者依据内容)主要有

·定义包含一组宏的粗略“区域”

·定义block ring layers,宽度和偏移量

·创建(提交)金属布线

通过执行脚本创建宏单元的P/G环:

source ./scripts/macro_pg_rir ngs.tcl

六、电源网络综合

1、对核心电源环、宏单元环、垂直以及水平环带进行约束

·电源带约束

·对核心的电源带约束

·为没有电源环的PLL定义宏单元环

·进行全局约束

执行脚本:

scripts / pns.tcl

2、提交电源计划:

commit_fp_rail

3、连接所有宏单元上的电源引脚,并创建标准单元电源轨道(power rail):

preroute_instances

preroute_standard_cells –fill_empty_rows \

-remove_floating_pieces

创建完之后,可以进行IR drop分析

4、保存这一阶段的设计

save_mw_cel -as floorplan_pns

七、检查时序

1、PNS在METAL4和METAL5上产生了许多电源带,这些带放在标准单元上。可以有利地防止标签单元放置在带下 - 这降低了沿带的拥塞的可能性,并且减少了对电源网络的串扰影响。 在带上应用“完整”电源网(pnet)阻塞,然后再次运行虚拟平面放置以考虑pnet设置:

set_pnet_options -complete "METAL4 METAL5"

create_fp_placement -timing_driven -no_hierarcI hy_gravity

2、通过执行实际布线进行检查时序:

route_zrt_global

3、使用“view,查看”过程生成最大延迟(建立时间)时序报告(更新时序和生成报告需要几秒钟):

v report_timing

如果有时序违规,则可以重新进行优化布线:

optimize_fp_timing –fix_design_rule

4、保存设计

save_mw_cel -as floorplan_complete

八、写出DEF文件

删除所有放置的标准单元,然后以DEF格式写出floorplan文件。这个DEF平面规划文件将被Design Compiler Topographical 使用来再次综合;然后在ICC再次读入再次综合后的网表后,再用ICC进行布局规划:

下面是删除所有放置的标准单元,然后以DEF格式写出floorplan文件:

remove_placement -object_type standard_cell

九、为布局做准备而创建第二遍(布局规划)设计

假装这个设计是从RTL代码使用DC的拓扑模式重新综合的,重新综合的过程使用上一步生成的DEF文件。这是我们得到第二遍网表ORCA_2.v以及更新后的约束文件ORCA_2.sdc。

1、使用新的ORCA网表和约束执行数据设置:

source -echo scripts/2nd_pass_setup.tcl

这个脚本进行了标准的数据设置准备。

2、读入上一个步骤写出的def文件:

read_def design_data/ORCA.def

3、新应用的电源网络合成后应用的pnet选项。这些设置不在DEF文件中定义:

set_pnet_options -complete "METAL4 METAL5"

4、将设计保存为ready_for_placement:

save_mw_cel -as ready_for_placement

ICC的设计规划实验大概流程就是这样了,其中主要跑脚本,脚本的内容才是设计规划的内容,要把脚本的内容参透才真正把这个实验的内容参透。时间问题,这里就不仔细去看了,主要学习流程.

-->数据准备(设置)、加载设计并切换到floorplan模式

--> 创建拐角(Corner)和电源地(P/G)单元并定义他们pad的位置

-->创建floorplan

-->在电源/接地信号和I / O焊盘,宏和标准单元的所有电源/接地引脚之间建立“逻辑”连接

-->创建pad的电源环,保存电源环创建后的设计

-->验证当前虚拟平面放置策略选项是否具有默认设置

-->设置sliver 的尺寸,防止标准单元放置在宏单元之间的狭窄通道

-->使用“无层次结构重力”(选项)来执行 时序驱动的虚拟平台放置

-->进行宏单元布局约束

-->检查设置

-->所有宏单元周围设置10微米的硬限制边距

-->再次进行宏单元布局,锁定所有的宏,保存IO、宏单元布局规划后的设计

-->在宏单元周围创建P/G环

-->电源网络综合:对核心电源环、宏单元环、垂直以及水平环带进行约束、提交电源计划、连接所有宏单元上的电源引脚,并创建标准单元电源轨道(power rail)、保存这一阶段的设计

-->检查时序

-->写出DEF文件

-->为布局做准备而创建第二遍(布局规划)设计

浙公网安备 33010602011771号

浙公网安备 33010602011771号