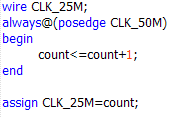

今天做了一个关于VGA的显示实验,但是由于产生的25M时钟不正确所以一直没有图像产生。刚开始的程序如下

虽然仿真的时候出现了时序,但是在下载到硬件的时候不正确。

后来改成

结果就正确了。

另外之前关于分频时用边沿触发和用电平触发的结果是不一样的。

下面是VGA实验使用到了ADV7123在DE115平台进行的实验。640*480*25M水平同步信号和场同步信号可以 根据VGA的时序图进行计算。

顶层文件://THIS IS ABOUT VGA TEST 实验结果整个屏幕是红色

module VGA(CLK_50M,VGA_R,VGA_G,VGA_B,VGA_CLK,

VGA_SYNC_N,VGA_BLANK_N,VGA_VS,VGA_HS);

input CLK_50M;//THE INPUT TIME CLOCK

output [7:0]VGA_R;//OUTPUT RED PIX

output [7:0]VGA_B;//blue pix

output[7:0]VGA_G;//GREEN PIX

output VGA_CLK;//ADC7123 TIME CLOCK

output VGA_SYNC_N; //同步信号

output VGA_BLANK_N;//消隐信号

output VGA_HS;//水平同步

output VGA_VS;//场同步

//wire CLK_25M;

//pll_25m U1(CLK_50M,CLK_25M);

reg count=0;

//reg CLK_25M;

/*always@(posedge CLK_50M)

begin

count<=count+1;

if(count)

CLK_25M<=~CLK_25M;

end*/

wire CLK_25M;

always@(posedge CLK_50M)

begin

count<=count+1;

end

assign CLK_25M=count;

VGA_CONTRAL VGA_TEST(CLK_25M,VGA_R,VGA_G,VGA_B,VGA_CLK,

VGA_SYNC_N,VGA_BLANK_N,VGA_VS,VGA_HS);

endmodule

////////////////////////////////////

module VGA_CONTRAL(CLK_25M,VGA_R,VGA_G,VGA_B,VGA_CLK,

VGA_SYNC_N,VGA_BLANK_N,VGA_VS,VGA_HS);

input CLK_25M;//THE INPUT TIME CLOCK

output [7:0]VGA_R;//OUTPUT RED PIX

output [7:0]VGA_B;//blue pix

output[7:0]VGA_G;//GREEN PIX

output VGA_CLK;//ADC7123 TIME CLOCK

output VGA_SYNC_N; //同步信号

output VGA_BLANK_N;//消隐信号

output reg VGA_HS;//水平同步

output reg VGA_VS;//场同步

//水平参数

parameter H_SYNC_CYC=95;

parameter H_SYNC_BACK=48;

parameter H_SYNC_ACT=635;

parameter H_SYNC_FRONT=15;

parameter H_SYNC_TOTAL=793;

//垂直参数

parameter V_SYNC_CYC=2;

parameter V_SYNC_BACK=33;

parameter V_SYNC_ACT=480;

parameter V_SYNC_FRONT=10;

parameter V_SYNC_TOTAL=525;

parameter H_START=H_SYNC_CYC+H_SYNC_BACK;

parameter V_START=V_SYNC_CYC+V_SYNC_BACK;

reg [9:0]HCOUNT=0;

reg [9:0]VCOUNT=0;

assign VGA_R=((HCOUNT>=H_START)&&(HCOUNT<=H_START+H_SYNC_ACT)&&

(VCOUNT>=V_START)&&(VCOUNT<V_START+V_SYNC_ACT)) ? 200:0;

assign VGA_G=((HCOUNT>=H_START)&&(HCOUNT<=H_START+H_SYNC_ACT)&&

(VCOUNT>=V_START)&&(VCOUNT<V_START+V_SYNC_ACT)) ? 0:0;

assign VGA_B=((HCOUNT>=H_START)&&(HCOUNT<=H_START+H_SYNC_ACT)&&

(VCOUNT>=V_START)&&(VCOUNT<V_START+V_SYNC_ACT)) ? 0:0;

assign VGA_CLK=CLK_25M;

assign VGA_SYNC_N=1'b0;

assign VGA_BLANK_N=VGA_HS&VGA_VS;

always@(posedge CLK_25M)

begin

if(HCOUNT<H_SYNC_TOTAL)

HCOUNT<=HCOUNT+1;

else

begin

HCOUNT<=0;

if(VCOUNT<V_SYNC_TOTAL)

VCOUNT<=VCOUNT+1;

else

VCOUNT<=0;

if(VCOUNT<=V_SYNC_CYC)

VGA_VS<=0;

else

VGA_VS<=1;

end

if(HCOUNT<=H_SYNC_CYC)

VGA_HS<=0;

else

VGA_HS<=1;

end

endmodule