通信协议-SPI

一、SPI概述

SPI是串行外设接口(Serial Peripheral Interface)的缩写,是美国摩托罗拉公司(Motorola)最先推出的一种同步串行传输规范,也是一种单片机外设芯片串行扩展接口,是一种高速、全双工、同步通信总线,所以可以在同一时间发送和接收数据,SPI没有定义速度限制,通常能达到甚至超过10M/bps。

SPI属于一主多从(一个主设备(Master),多个从设备(Slave))的总线结构,当存在多个从设备的时候,主设备通过片选信号来决定选择哪个设备。

1.1 基本结构

SPI共有4条信号线:

- MISO(Master in slave out):主设备输入从设备输出,数据由从设备发出;

- MOSI(Master out slave in):主设备输出从设备输入,数据由主设备发出;

- SCLK/SCK(Serial clock):串行时钟信号,由主设备产生;

- $\overline{SS}$/$\overline{CS}$(Slave/Chip slect):丛机选择信号,一般低电平有效,由主设备发出;

由上图也可以看出当SPI设备间通信时,数据线应该是MOSI连接MOSI,MISO连接MISO,SCLK与SCLK相连。

当只有单一SPI从设备时,如果从设备允许的话,可直接将CS/SS线固定在低电平。

对于多个从设备时,则每个从设备都需要一根CS/SS线来于主设备相连,从而达到主设备能与任一从从设备通信的目的。

1.2 优缺点

SPI总线的优点:

- SPI通信无起始位和停止位,因此数据可以连续流传输而不会中断;没有像I2C这样的复杂的从站寻址系统,数据传输速率比I2C更高(几乎快两倍)。独立的MISO和MOSI线路,可以同时发送和接收数据;

SPI总线的缺点:

- SPI使用四根线,而I2C和UART只是使用两根线,没有信号接收成功的确认(I2C拥有该功能),没有任何形式的错误检查(如UART中的奇偶校验位等);

二、主从设备通信过程

在SPI每个时钟中期内,都会进行一次全双工数据的传输,主设备通过MOSI线上发送1位时,从设备也会在读取数据之后通过MISO发送发送1位数据出去。

SPI主从设备都有一个串行移位寄存器,主设备通过向它的SPI串行移位寄存器写入一个字节来发送一次数据传输。

SPI数据通信流程可以分为以下几个步骤:

- 主设备发起信号,将$\overline{SS}$或$\overline{CS}$拉低,通信开始;

- 主设备通过发送SCLK时钟信号,告诉从设备进行读写操作。这里的SCLK时钟信号是由SPI的模式来决定高电平还是低电平有效;

- 主设备将要发送的数据写入到发送数据缓冲区(Memory),缓冲区经过移位寄存器位[7:0],串行移位寄存器通过MOSI将字节数据一位一位的传输到从设备,同时MISO接收到的数据经过移位寄存器一位一位的传输到接收缓冲区;

- 从设备也将自己的串行移位寄存器位[7:0]的数据通过MISO传输到主设备,同时通过MOSI接收主设备发送的数据,这样这两个移位寄存器中的数据被交换;

三、通信特性

3.1 设备选择

SPI是单主设备(Single Master)通信协议,只有一个主设备能发起通信,当SPI主设备想读/写从设备时,它首先拉低从设备对应的$\overline{SS}$线。

接着开始发送工作脉冲到时钟线上,在相应的脉冲时间上,主设备把信号发到MOSI实现“写”,同时可对MISO采样而实现“读”。如下图所示:

3.2 设备时钟

SPI时钟特点主要包括:时钟频率、时钟极性和时钟相位。

3.2.1 时钟频率

SPI主设备必须在通信开始之前配置并生成相应的时钟信号,当然时钟频率受限于我们SPI主设备能输出的最大频率、以及最大的SPI传输频率。

3.2.2 时钟极性

根据硬件制造商的命名规则不同,时钟极性通常写为CKP或CPOL。时钟极性和相位共同决定读取数据的方式,比如信号上升沿读取数据还是信号下降沿读取数据。

时钟极性(CPOL)定义了SCLK时钟线空闲状态时的电平:

- CPOL=0,即SCLK=0,表示SCLK时钟信号线在空闲状态时的电平为低电平,因此有效状态为高电平;

- CPOL=1,即SCLK=1,表示SCLK时钟信号线在空闲状态时的电平为高电平,因此有效状态为低电;

3.2.3 时钟相位

根据硬件制造商的不同,时钟相位通常写为CKE或CPHA。

时钟相位(CPHA)定义了数据位相对于时钟线的时序(即相位):

- CPHA=0,在时钟信号SCK的第一个跳变沿采样;

- CPHA=1,在时钟信号SCK的第二个跳变沿采样;

3.3 四种模式

根据SPI的时钟极性和时钟相位特性可以设置4种不同的SPI通信操作模式,它们的区别是定义了在时钟脉冲的哪条边沿转换输出信号,哪条边沿采样输入信号,还有时钟脉冲的稳定电平值(就是时钟信号无效时是高还是低)。如下表,为SPI通信的4种模式:

| CPOL | CPOH | 空闲SCLK时钟 | 采样时刻 |

| 0 | 0 | 低电平 | 第1个边沿 |

| 0 | 1 | 低电平 | 第2个边沿 |

| 1 | 0 | 高电平 | 第1个边沿 |

| 1 | 1 | 高电平 | 第2个边沿 |

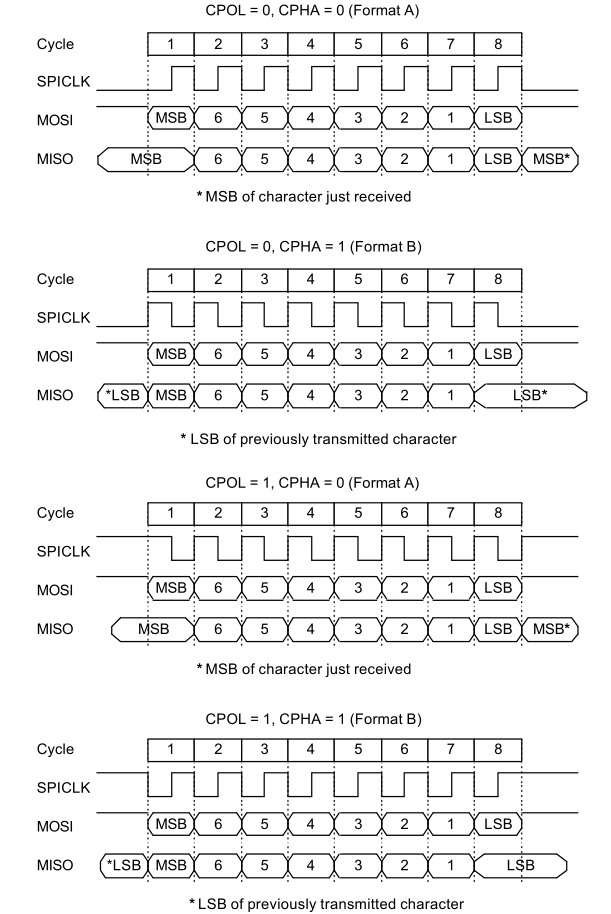

下面是我从S3C2440手册裁切到的4种模式的SPI通信时序图:

具体说明如下:

- 图1,CPOL=0,CPHA=0:当空闲态时,SCLK处于低电平,数据采样是在第1个边沿,也就是SCLK由低电平到高电平的跳变,所以数据采样是在上升沿,数据发送是在下降沿(第一位数据发送是在上升沿之前);

- 图2,CPOL=0,CPHA=1:当空闲态时,SCLK处于低电平,数据采样是在第2个边沿,也就是SCLK由高电平到低电平的跳变,所以数据采样是在下降沿,数据发送是在上升沿;

- 图3,CPOL=1,CPHA=0:当空闲态时,SCLK高于高电平,数据采样是在第1个边沿,也就是SCLK由高电平到低电平的跳变,所以数据采样是在下降沿,数据发送是在上升沿(第一个数据发送是在下降沿之前);

- 图4,CPOL=1,CPHA=1:当空闲态时,SCLK高于高电平,数据采样是在第2个边沿,也就是SCLK由低电平到高电平的跳变,所以数据采样是在上降沿,数据发送是在下降沿;

参考文章;

[1] 一文搞懂SPI通信协议

浙公网安备 33010602011771号

浙公网安备 33010602011771号