Mini2440裸机开发之Nand Flash 基础

一、Nand Flash介绍

Flash 是闪存,可以反复读写的一种存储介质,掉电后数据不会丢失。目前Flash主要分为Nor Flash 和Nand Flash。

Nand Flash和Nor Flash比较:

- Nor型Flash采用的SRAM接口,提供足够的地址引脚来寻址,可以很容易的存取其片内的每一个字节;Nand型Flash使用复杂的I/O口来串行的存取数据,各个产品或厂商的方法可能各不相同,通常是采用8个I/O引脚来传送控制、地址、数据信息。

- Nor型Flash操作是以“字”为基本单位,而Nand型Flash以“页面”为基本单位,页的大小一般为512字节。

- Nor型Flash的地址线和数据线是分开的,传输效率很高,程序可以在芯片内部执行,Nor型的读速度比Nand稍快一些;Nand型Flash写入速度比Nor型Flash快很多,因为Nand读写以页为基本操作单位。

- Nand型Flash具有较高的单元密度,容量可以做得比较大,加之其生产过程更为简单,价格较低;Nor型Flash占据了容量为1~16MB闪存市场的大部分,而Nand型Flash只是用在8~xxGB的产品中,这也说明Nor主要用在代码存储介质中,Nand适合数据存储在CompactFlash、PC Cards、MMC存储卡市场上所占的份额最大。

- Nand型和Nor型Flash在进行写入和擦除时都需要MTD(Memory Technology Drivers,MTD已集成在Flash芯片内部,它是对Flash进行操作的接口),这是它们的共同特点;但在Nor型Flash上运行代码不需要任何的软件支持,而在Nand型Flash上进行同样操作时,通常需要驱动程序,即内存技术驱动程序MTD。

目前的Nor Flash 存储器价格较高,相对而言SDRAM 和Nand Flash 存储器更经济,这样促使了一些用户 在Nand Flash 中执行引导代码,在SDRAM 中执行主代码。

常见的U盘、TF卡/SD卡,以及大部分SSD(固态硬盘)均是采用Nand Flash芯片作为存储介质。

常见的Flash厂商有:Micron(镁光)、Toshiba(东芝)、Samsung(三星)、MXIC(旺宏)、dosilicon(东芯),(Winbond)华邦、ESMT等。

1.1 Nand Flash原理图

Mini2440开发板就是将采用了的256MB的Nand Flash(型号K9F2G08U0C)。

1.2 K9F2G08U0C芯片介绍

下图的信息来是官方手册:

-

可以看出此款Nand Flash容量为256M,外加8M的冗余oob存储区;

-

page大小为2K,block大小为128K;

-

读一个page时顺序读取至少25*2048ns(数据可以每字节25ns的循环时间读出),随机读取不超过40us;

-

写一个page一般为250us;

-

擦除一个block一般为2ms

-

封装上分为TSOP分装和FBGA封装(TSOP是指引脚在侧面,FBGA是引脚封在芯片底部,更能保障数据安全,有些客户为了保障数据安全性,防止被飞线进行数据破解,会要求用FBGA封装的flash)

实际上芯片的名字K9F2G08U0C中2G表示的就是容量,即2Gb=256M,08表示的就是数据线宽度。

1.2.1 引脚信息

引脚信息如下:

| Pin Name | Pin Function |

| I/O0 ~ I/O7 |

DATA INPUTS/OUTPUTS 数据输入输出(命令、地址、数据公用数据总线) |

| CLE |

COMMAND LATCH ENABLE 命令使能,当CLE为高电平时,$\overline{WE}$ 上升沿锁存I/O输入到命令寄存器 |

| ALE |

ADDRESS LATCH ENABLE 地址使能,当ALE为高电平时,$\overline{WE}$上升沿锁存I/O输入到地址寄存器 |

| $\overline{CE}$ |

CHIP ENABLE 片选信号,低电位有效 |

| $\overline{RE}$ |

READ ENABLE 读使能,低电位有效 |

| $\overline{WE}$ |

WRITE ENABLE $\overline{WE}$上升沿锁存I/O输入到命令、地址、数据寄存器 |

| $\overline{WP}$ |

WRITE PROTECT 写保护 |

| $R/\overline{B}$ |

READY/BUSY OUTPUT 就绪/忙输出信号(低电平表示操作还在进行中,高电平表示操作完成) |

| VCC |

POWER |

| VSS | GROUND |

| NC |

NO CONNECTION |

1.3 内部存储结构

我们常见的Nand Flash,内部只有一个chip,每个chip只有一个plane。但也有些复杂的,容量更大的Nand Flash,内部有多个chip,每个chip有多个plane,这类的Nand Flash,其实就是多了一个主控将多块Flash叠加在一起,如下图:

- Block块:一个Nand Flash由很多个块(Block)组成,块的大小一般有64K,128KB,256KB,512KB,Block是Nand Flash的擦除操作的基本/最小单位。Nand Flash中,一个块中含有1个或多个位是坏的,就称为其为坏块Bad Block。

-

Page页:每个块里面又包含了很多页(page)。每个页的大小,对于现在常见的Nand Flash多数是2KB,当然也有的Nand Flash的页大小为4KB、8KB等。页Page,是读写操作的基本单位。

-

oob ( Spare Area):每一个page页,对应还附加了一块区域,一般为64byte,叫做空闲区域(spare area)/oob区域(Out Of Band),由于Nand Flash在操作过程中容易产生位反转,这是Nand Flash的物理特性决定的,所以必须要有对应的检测和纠错机制,这种机制被叫做Error Checking and Correcting,所以设计了多余的oob区域,用于放置数据的校验值。oob的读写操作,一般是随着页的操作一起完成的,即读写页的时候,对应地就读写了oob。 关于oob具体用途,总结起来有:

- 标记是否是坏快;

- 存储ECC数据;

- 存储一些和文件系统相关的数据。如jffs2就会用到这些空间存储一些特定信息;

1.3.1 K9F2G08U0C

以K9F2G08U0C为例:

- 页--Page: (2K + 64)Byte , 每页有2048个字节,需要2^11==2048,即11位地址;

- 块--Block: (128K + 4K)Byte, 每块有64页,需要2^6=64,即6位地址;

- 256M/128K = 2048Block, 芯片一共有2048块,需要2^11 = 2048,即11位地址

现在以第25块的30页中的24byte为例:

物理地址 = 块大小×块号 + 页大小×页号 + 页内地址

= 128K x 25 + 2K x 30 + 24B

= 3338264(10)

= 32F018 (16)

0x32F018 = 0011 0010 1111 0000 0001 1000;

由此可得到实际发送的数据

- A7 - A0 = 0001 1000 0xFF&col

- A10 - A8 = 000 0x07 & (col >> 8)

- A11 = 0 访问存储区,A11=1访问oob;

- A19 - A12 = 0101 1110 0xFF & page

- A27 - A20 = 0000 0110 0xFF & (page >> 8)

- A28 = 0 0x01 & (page >> 16)

其中:地址 = 64*2048*块号 + 2048 * 页号 + 页内地址;

列地址 col = A10 - A0 = 地址 & (页大小-1)= 0x32F018 & 7FF= 0x018 = 000 0001 1000,列地址表示的是某页内的2k地址;

页地址 page = A28 - A12 = 地址/页大小 = 0x32F018 / 0x800 = 0x65E = 0 0000 0110 0101 1110,页地址表示对应的某一页,或者说为行地址;

二、S3C2440 Nand Flash控制器

2.1 Nand Flash启动

我们知道Nand Flash没有独立地址线,CPU无法直接访问Nand Flash上的指令,所以Nand Flash不能片上执行。那么为何程序还能支持Nand Flash启动的呢?

为了支持Nand Flash启动,S3C2440A配备了一个称为“ Steppingstone”的内部SRAM缓冲区,容量为4K。 开机时,Nand Flash中的前4K BootLoader代码将被加载到Steppingstone中,在加载完代码后,BootLoader代码将在SRAM中将被执行,如下图所示:

我们知道s3c2440支持2种boot方式,Nand Flash或者Nor Flash,那么需要配置OM引脚来设置引导方式,OM[1:0] = 00:使能Nand Flash 存储器引导启动。

内存控制器的地址映射表如下:

2.2 引脚配置

当上电启动时,Nand Flash 控制器将通过下面的引脚状态来获取连接的 Nand Flash 的信息。

(1) NCON:Nand Flash 存储器选择(普通/先进)

- 0:普通 Nand Flash(256 字或 512 字节页大小,3 或 4 个地址周期)

- 1:先进 Nand Flash(1K 字或 2K 字节页大小,4 或 5 个地址周期)

(2) GPG13:Nand Flash 存储器page size选择

- 0:页=256 字(NCON=0)或页=1K 字(NCON=1)

- 1:页=512 字节(NCON=0)或页=2K 字节(NCON=1)

(3) GPG14:Nand Flash 存储器地址周期选择

- 0:3 个地址周期(NCON=0)或 4 个地址周期(NCON=1)

- 1:4 个地址周期(NCON=0)或 5 个地址周期(NCON=1)

(4) GPG15:Nand Flash 存储器总线宽度选择

- 0:8 位宽度

- 1:16 位宽度

如下表所示更直观:

三 Nand Flash控制器时序配置

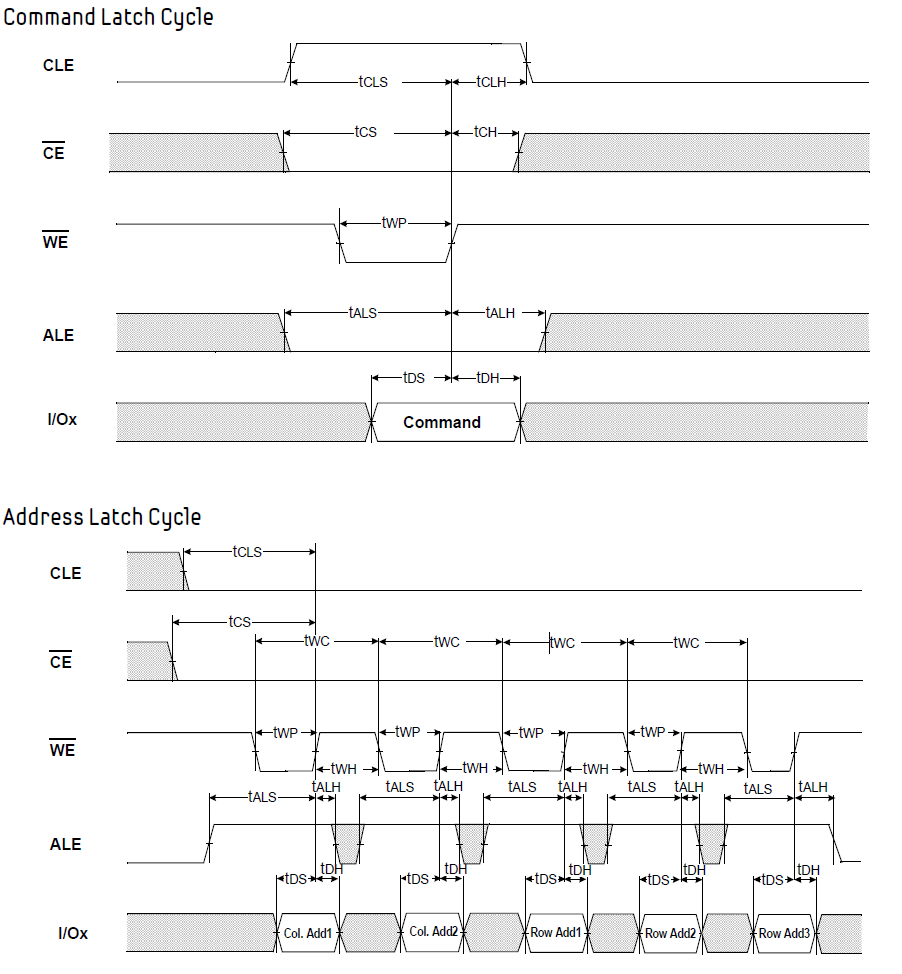

Nand Flash访问时需要遵循一定的时序才能完成命令、地址、数据的发送。以8位宽数据总线为例,那么没有地址线它是怎么和CPU通信的呢?

Nand Flash是DATA0~DATA7上既传输数据,又传输地址,又传输命令;

- 当ALE为高电平时传输的是地址;

- 当CLE为高电平时传输的是命令;

- 当ALE,CLE都为低电平表示传输的是数据 ;

下面分别介绍命令、地址、数据的发送过程。

3.1 命令/地址锁存序号(写命令/地址)

3.1.1 Nand Flsh控制器时序

1)首先看时钟,Nand Flash控制器的时钟源采用的是HCLK, 也就是AHB高速总线模式,假设HCLK=100Mhz, 则T=1/HCLK=10ns;

2)从上图可知命令、地址锁存的时序是一样的,复用一个时序图,当到达①的位置时,CLE/ALE=0;

3)当到达位置②时,CLE/ALE=1,表示命令/地址信号拉高,命令/地址开始使能,然后往数据总线DATA上放入命令或地址;

4)经过TACLS时间,到达位置③时,拉低nWE引脚,经过TWRPH0时间后,数据总线DATA上的命令/地址在nWR上升沿开始被锁存;

5)到达位置④,锁存需要一定的时间,所以经过TWRPH1时间后,数据总线DATA上的命令/地址锁存完成,此时释放CLE/ALE,一个完整的命令/地址锁存过程完成。

上面分析了命令/地址的锁存时序过程,下面详细解释下上面几个时间参数的含义:

- TACLS:CLE/ALE使能信号发送多久后才可以发送nWE信号;

- TWRPH0:nWE信号发送多久后数据(commamd/addr)才会被锁存;

- TWRPH1:nWE信号释放多久后才能释放CLE/ALE。

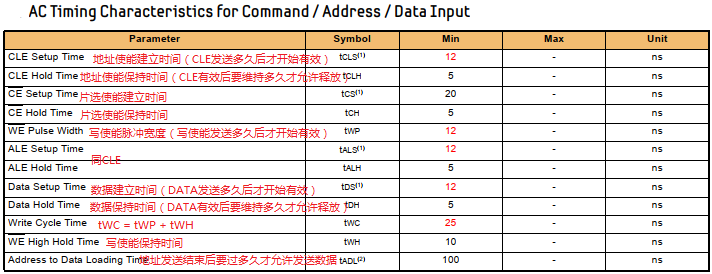

3.1.2 K9F2G08U0C 时序

那么这些时间参数要怎么配置呢?

这个需要根据我们实际使用的具体Nand Flash型号和性能来配置我们的Nand Flash控制器。我们以K9F2G08U0C这款Nand Flash为例进行讲解,手册上命令和地址锁存周期如下:

3.1.3 Nand Flash控制器参数设置

和Nand Flash控制器的命令/地址锁存时序图对比发现:

TACLS = max(tCLS,tALS) - tWP;

TWRPH0 = tWP;

TWRPH1 = max(tCLH,tALH);

我们知道S3C2440 Nand Flash控制器把命令、地址锁存时序复用成了一个时序图,其实命令和地址锁存时序参数基本一致,只不过发命令只需要一个周期就OK了,发地址需要5个时钟周期,为什么?

你想,命令多简单,无非就是读写擦,像我们这款Nand Flash数据位宽8bit,一个周期绰绰有余。但地址就不一样了,比如此款Nand Flash容量256M = 2^28,那么需要28根数据线来传输才能一个周期传输完,但这款Nand Flash的数据总线位宽只有8bit, 只有8根数据线,所以需要把地址拆分成多次发送,先发送col地址,再发送row地址,此款Nand Flash使用了5个周期发送地址。

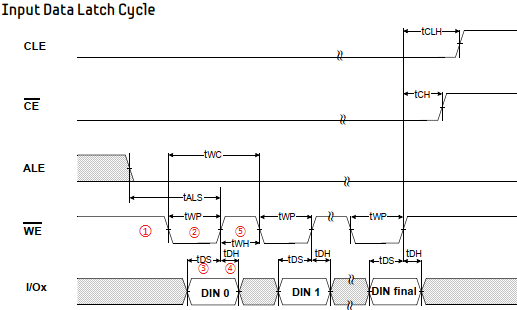

3.2 数据锁存时序(写数据)

从前面的命令地址锁存时序图中我们得知:

- CLE信号拉高,ALE信号拉低时,表示发送的命令;

- 当CLE信号拉低,ALE信号拉高时,表示发送的地址;

- 那么当CLE、ALE都拉低时,表示发送的数据;

3.2.1 K9F2G08U0C 时序

如下图,$\overline{CE}$, CLE, ALE都拉低了,表示传输的是数据。

1) 当到达①时,$\overline{WE}$还是高电平,写使能没有开启;

2) 当到达②,③时,那么经过了tWP时间(TDS时间),在$\overline{WE}$上升沿数据开始被锁存;

3) 到达④,经过tDH时间,数据锁存完成;

4) 到达⑤,也就是数据开始锁存后再过了tWH时间后释放$\overline{WE}$信号;

5) 重复②③④⑤过程。

根据上面这三个图(手册上的命令、地址、数据锁存时序图),下面详细解释各个时间参数的含义:

3.3 顺序访问周期(读数据)

3.3.1 K9F2G08U0C 时序

1)①处,表示要过tRR后才能发送读使能信号$\overline{RE}$进行访问(上一次的访问结束后,需要等待ready状态稳定后才可以进行下一次访问);

2)当到达②,需要经过tREA时间后$\overline{RE}$信号才有效(待nRE稳定);

3)当到达③,DATA总线上的读取被读取;

4)当到达④,$\overline{RE}$释放tREH时间后才允许下一次读使能

我们看到连续顺序访问时,单次访问的时间为tRC,那么这些时间参数的值也可以从K9F2G08U0C datasheet中找到:为25ns

参考文章:

浙公网安备 33010602011771号

浙公网安备 33010602011771号