FPGA设计之——DDR3

一、硬件设计

1、DDR3颗粒一侧,控制线、地址线线序不能交换;

2、DDR3颗粒一侧,数据线可随意交换;

3、FPGA一侧,控制线、地址线、数据线均有专用引脚,需全部按要求连接。

这样一是为了硬件布线能通,二是保证了FPGA分配引脚时不会乱,按照专用引脚规定的分配即可。

如此设计,FPGA写DDR3时,写地址正常翻译,写入的数据是乱序的,但对应读也是乱序的,所以FPGA读出来的数据和写入的数据相同,且和用户逻辑设定值一样,故不存在问题。

二、引脚分配

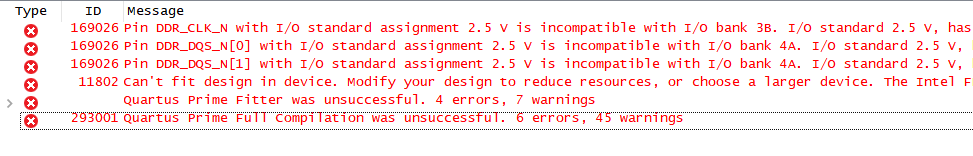

1、引脚分配时,差分引脚需特别注意,就算在 pin_planner 里正确设计了 pin 和 io 标准,综合时还是可能会报错,具体如下:

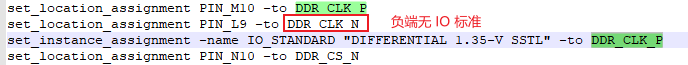

2、此时查看 qsf 文件,可看到报错的这三个差分负端PIN并没有IO标准,具体如下:

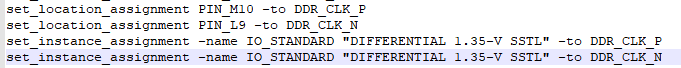

3、手动在 qsf 文件中添加如下约束,再编译时不再报错:

关于DDR3读写控制等,持续更新......

浙公网安备 33010602011771号

浙公网安备 33010602011771号