“FPGA+CPU” 并行处理大行其道

http://www.eepw.com.cn/article/201808/387131.htm

深亚微米时代,传统材料、结构乃至工艺都在趋于极限状态,摩尔定律也已有些捉襟见肘。而步入深亚纳米时代,晶体管的尺寸就将接近单个原子,无法再往下缩减。传统ASIC和ASSP设计不可避免地遭遇了诸如设计流程复杂、生产良率降低、设计周期过长,研发制造费用剧增等难题,从某种程度上大大放缓了摩尔定律的延续。

本文引用地址:http://www.eepw.com.cn/article/201808/387131.htm

显而易见的是,在巨额的流片成本面前,很多中小规模公司不得不改变策略,更多的转向FPGA的开发和设计。反观FPGA市场,即便是5年前,其相对于ASIC的市场增速还是相当迟缓的,但在近些年,尤其是迈进90nm节点之后,其成本优势逐渐凸显。

二十年如一日,长期霸占着可编程逻辑器件市场的两大巨头Xilinx和Altera依然动作频频。8月的Altera研讨会,13个城市的技术巡演,大张旗鼓地力推28nm工艺上的V系产品、SOPC Builder到Qsys新平台的更迭乃至SOC FPGA的新构想。相比之下,9月的Xilinx则低调许多,但依然拿出了7系列产品与对手叫板。从一年前的65nm到今天的28nm,由于门延时早已不再是速度性能提升的瓶颈,因此用户能够感受到的变化只是器件密度的提高和单位成本的下降。除此以外,只能说厂商绞尽脑汁的优化器件架构和改善开发工具性能成为了另一道可供观赏的风景线。 无独有偶,Xilinx和Altera都纷纷加速推出了内嵌硬核CPU的FPGA器件。FPGA+CPU的解决方案并不稀奇,早在五年前就被提出并付诸实践,Xilinx和Altera也一直在致力于自己的软核CPU的推进,但市场反应显然没有达到预期。Xilinx顺应市场需求,率先于去年4月发布了集成ARM Cortex-A9 CPU和28nm FPGA的可扩展式处理平台(Extensible Processing Platform)架构。时隔不到一年,可扩展处理平台Zynq-7000系列又被搬上了前台,Xilinx的用心良苦可见一斑。Altera也不示弱,英特尔在去年秋季发布的凌动E600C可配置处理器中就集成了Altera的FPGA,并且Altera即将推出的同样集成Cortex-A9 CPU的SoC FPGA明显是要与Xilinx唱对台戏。

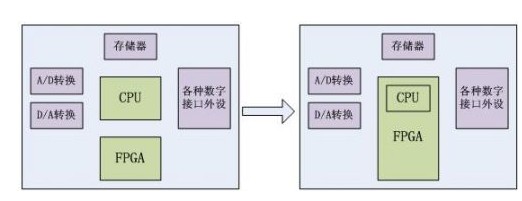

对于我们而言,更多的是需要去探讨和思索这种新的开发平台是否真的满足客户日益增长的“物质文化”需求。我们也不禁会问:FPGA+CPU的集成架构到底是顺应了历史发展的趋势,还是仅仅昙花一现转眼即逝? 如图1所示,一个比较简化的传统嵌入式系统如左图所示,单片集成了CPU的FPGA架构则如右图所示。单从硬件架构层面来看,好像没有太大的优势,仅仅只是二合一而已。但是真正做过系统开发的工程师都知道,这种二合一所带来的不仅仅是BOM成本降低和布局的简化,更多的利好是我们肉眼看不到的软硬件底层衔接的优化和无形之中的灵活性以及潜在的性能提升。

图1

基于FPGA的CPU集成将带来的一些潜在优势包括:更易于满足大多数系统的功能性需求;潜在的改善了系统的性能;在某些应用中的灵活性和可升级性大大提高;处理器到外设的接口能够得到优化;软硬件互联的接口性能获得极大的提升;有利于设计的重用和新设计的快速成型;简化单芯片甚至整板的PCB布局布线。

FPGA+CPU的单片集成相较于传统应用的优势由此可见一斑,但从另一个角度看,正如CPU从单核到多核演进在延续着摩尔定律的“魔咒”,FPGA+CPU的强势出击更像是并行处理在嵌入式应用中的大行其道。

延续一贯的作风,Xilinx和Altera在其嵌入CPU的FPGA器件上都不约而同地选择了性能出色的ARM Cortex-A9内核,可见他们目前瞄准的市场趋向于中高端应用客户。而在低端应用方面,即便是网络爆炸的时代,默默无闻的Capital-Micro公司依然不为广大工程师们所熟知,但他们开发的可重构系统芯片CsoC(Configurable SoC)却悄然无声地在中低端市场应用中杀出了一片血路。值得一提的是,这是一家地地道道的中国本土FPGA厂商。

从1971年Intel的第一片4位处理器问世至今恰好已有40个年头,虽然嵌入式行业经历了翻天覆地的巨变,但即便你认为它是“土得掉牙”却简单实用的8位MCS-51单片机却依然独树一帜,尤其是在国内的整个工控行业中还是有着很强的生命力。从05年成立至今,Capital-Micro先后推出了Astro和AstroII两代CSoC。其内嵌的8051在两代器件上分别可以稳定地运行到100MHz和150MHz。虽然由于FPGA制造工艺还处于0.13um,大大制约了逻辑性能,但目前的这两代产品至少可以满足包括步进电机控制、LCD驱动控制、接口扩展、LED控制卡、微型打印机在内的工业应用需求。

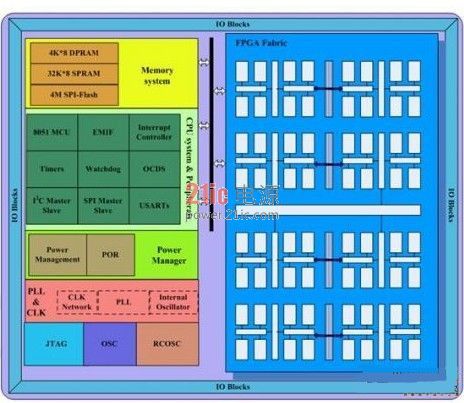

从器件的内部架构上来看,如图2所示,AstroII中不仅有同类产品中堪称性能“卓越”的8051硬核,也集成了一些常见的外设如定时器、看门狗、UART、IIC和SPI等。当然,8051的程序启动也完全采取了类似很多ARM的直接映射(Fully Shadowed)方式,确保读写缓慢的ROM不再成为制约CPU性能的瓶颈。而8051与FPGA的互联方面,不仅可以使用8051的EMIF寻址(23位宽可寻址地址总线),4K×8bit的DPRAM也是高速数据传输的不错选择,并且在这些互联接口上都已经固化好了同步逻辑,无需设计者浪费精力。此外,从最廉价的晶体时钟支持,到I/O数量的最大化,再到其平易近人的价格,无不向我们展示着这款国产芯片的“经济适用”。

图2

总而言之,无论是Xilinx还是Altera,抑或是横空出世的Capital-Micro,他们所力推的全新单片集成器件,无不预示着FPGA+CPU的并行处理架构将在嵌入式应用中开辟出一片崭新的天地,在这个单片性能提升即将迈入极限的深亚纳米时代,灵活多变的FPGA凭借其独有的并行性必将助力传统CPU的性能再次迈向新的高度。

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 基于Microsoft.Extensions.AI核心库实现RAG应用

· Linux系列:如何用heaptrack跟踪.NET程序的非托管内存泄露

· 开发者必知的日志记录最佳实践

· SQL Server 2025 AI相关能力初探

· Linux系列:如何用 C#调用 C方法造成内存泄露

· 无需6万激活码!GitHub神秘组织3小时极速复刻Manus,手把手教你使用OpenManus搭建本

· Manus爆火,是硬核还是营销?

· 终于写完轮子一部分:tcp代理 了,记录一下

· 别再用vector<bool>了!Google高级工程师:这可能是STL最大的设计失误

· 单元测试从入门到精通