计算机原理

计算机工作原理

1、首先,把计算步骤的程序和计算中需要的原始数据,在控制器输入命令的控制下,通过输入设备送入计算机的存储器设备;

2、其次,控制器从存储器读取指令,对指令进行译码,根据指令要求,向存储器发出存储、取数命令,向运算器发出运算命令;

3、其次,把运算器的运算结果存放在存储器内;

4、最后,在控制器的取数和输出命令命令作用下,通过输出设备输出计算结果。

cpu工作原理

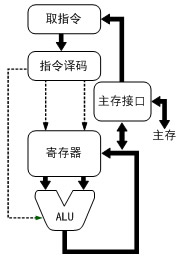

CPU主要由运算器和控制器两大部分组成

CPU功能

CPU是按照CPU指令来执行操作的,CPU功能如下:

1.指令控制:控制程序按照规定的顺序执行

2.操作控制:取出的指令,产生控制信号,发送相关的部件,控制这些部件按指令的要求工作

3.时间控制:控制信号在时间上有严格的先后顺序,如读取存储器的数据,只有当地址总线信号稳定后,才能进行读取。

4.数据加工:对数据进行算术运算和逻辑运算处理

对于一个通用的CPU来说,我们只需要关注他的核心部件:算数逻辑单元和操作控制单元

地址总线:实现内存寻址

数据总线:传输数据

控制总线:传输控制命令

CPU工作流程

CPU的基本工作是执行存储的指令序列,即:程序。程序的执行过程实际上是不断地取指令、分析指令、执行指令的过程。其工作可用分为5个阶段:

取指令、指令译码、执行指令、访存取数和结果写回。

存储器

存储器为CPU提供指令和数据

存储器系统层次结构

存储器不单包括内存,存储器系统是一个具有不同容量,不同访问速度的存储设备的层次机构,包括:

寄存器、缓存、内部存储器(内存)、外部存储(硬盘等),下面层次越高,速度最快,价格越高

相对与cpu而言,存储器的速度相对比较慢,通过提高存储器性能,可用改善计算机整体性能。

存储技术

寄存器

CPU内部有一些寄存器,寄存器速度最快,和cpu同时钟频率。一个寄存器需要20多个晶体管,占面积,所以CPU只有少量的寄存器。

RAM随机访问存储

RAM分2类:静态(SDAM)和动态(DRAM),SRAM相比DRAM速度更快功耗更低,但由于结构复杂占用面积大,一般少量在CPU内部

用作Cache,DRAM主要用来作为计算机的内存。

Cache:目前CPU一般集成2到3级Cache,容量从128K到4M,一般用来存储指令和数据,存在命中的问题:没有命中,需要向

下一集存储器获取新的数据,这是cache回被lock,导致实际的执行速度要比寄存器慢。cache速度:L1>L2>L3

内存:DRAM实现

ROM只读存储

RAM断电会丢失数据,断电不丢失称为ROM,特殊情况下,ROM也是可用写入数据的

PROM:可编程rom,只能编程1次

EPROM:可擦写可编程ROM,写入次数1K次

EEPROM:电子可擦除可编程ROM,不需要特殊设备而可直接在印制的电路板上编程,写入次数10w次

Flash Memory:闪存,基于EEPROM,但速度快很多,部分使用在U盘,SD卡、手机存储上。

ROM在计算机上应用也比较多,如:BIOS芯片,一般使用EPROM,如果损坏,计算机无法启动。而目前手机中也采用rom

来烧入系统,RAM作为内存,Flash Memory作为机身存储。

磁盘存储

从硬盘读取数据需要几个毫秒,而CPU时钟周期以纳秒计算。磁盘读取操作要比DRAM慢10w倍,比SRAM慢百万倍

磁盘存储是一种机械结构,数据通过电磁流来改变极性的方式被电磁流写到磁盘上,而通过相反的方式读回。

一个硬盘由多个盘片组成,每个盘片被划分为磁道,扇区和最小的单位簇。每个盘面都由一个磁头用来读取和写入数据,而硬盘的马达

装置则控制磁头的运动。

虚拟硬盘(VHD)和固态硬盘(SSD)

虚拟硬盘:内存虚拟成硬盘

固态硬盘:使用flash Memory

远程存储

将数据指令存储在其他机器上,远程存储的速度以秒来计算

存储器访问和总线

这一节介绍CPU和存储器之间是如何通信的

总线

所谓总线是各种功能部件之间传送信息的公共通信干线,总线就是用来连接五大组件的导线

总线可以分为:

数据总线: 数据总线DB是双向三态形式的总线,把CPU的数据传送到存储器或输入输出接口等其它部件,反之亦可。我们说的32位,64位计算机指的就是数据总线

地址总线: 地址总线AB是单向三态的,专门用来传送地址的,地址只能从CPU传向外部存储器或I/O端口,地址总线的位数决定了CPU可直接寻址的内存空间大小。

控制总线:控制总线是双向的,主要用来传送控制信号和时序信号

总线也可以按照CPU内外来分类:

- 内部总线:在CPU内部,寄存器之间和算术逻辑部件ALU与控制部件之间传输数据所用的总线称为片内部总线。

- 外部总线:通常所说的总线指片外部总线,是CPU与内存RAM、ROM和输入/输出设备接口之间进行通讯的通路,也称系统总线

控制芯片

CPU需要和存储器,I/O设备等进行交互,会有多种不同功能的控制芯片,我们称之为控制芯片组(Chipset)

目前计算机,控制芯片集成在主板上,有南北桥结构和单芯片结构,与芯片相连接的总线可以分为前端总线(FSB)、存储总线、IQ总线,扩展总线等。

- 南北桥芯片结构:

- 北桥芯片,控制着CPU的类型,主板的总线频率,内存控制器,显示核心等。它直接与CPU、内存、显卡、南桥相连,所以它数据量非常大;

- 前端总线:是将CPU连接到北桥芯片的总线。FSB的频率是指CPU和北桥之间的数据交换速度。速度越快,数据带宽越高,计算机性能越好;

- 内存总线:是将内存连接到北桥芯片的总线。用于和北桥之间的通信;

- 显卡总线:是将显卡连接到北桥芯片的总新。目前有AGP,PCI-E等接口。其实并没有显卡总线一说,一般认为属于I/O总线;

- 南桥芯片,它主要负责外部接口和内部CPU的联系;

- I/O总线:连接外部I/O设备连接到南桥的总线, 比如USB设备,ATA,SATA设备,以及一些扩展接口;

- 扩展总线:主要是主板上提供的一些PCI,ISA等插槽;

- 北桥芯片,控制着CPU的类型,主板的总线频率,内存控制器,显示核心等。它直接与CPU、内存、显卡、南桥相连,所以它数据量非常大;

- 单芯片结构: 单芯片组主要是是取消了北桥,因为现在CPU中内置了内存控制器,不需要再通过北桥来控制,这样就能提高内存控制器的频率,减少延迟。而现在一些CPU还集成了显示单元。也使得显示芯片的频率更高,延迟更低

运行频率

外频

外频是建立在数字脉冲信号震动速度基础上的,外频是系统总线的工作频率

频率和控制芯片

刚开始,CPU和内存还有I/O设置是直接通过总线连接的而没有控制芯片

随着CPU速率变大,与I/O设备有速率差,在CPU与I/O之间加入芯片解决,芯片起到降频实现,也就相对于系统总线的分频技术

发展到后来,出现了北桥芯片,CPU和北桥之前的总线称为了FSB总线,而内存与北桥之前称为内存总线

分频和倍频

分频:使得I/O设备可以和较高的外频协同工作

倍频:为了提高CPU频率又正常的和内存进行工作,所以产生了倍频,CPU实际频率=倍频*外频

FSB频率

FSB的实际频率是和外频一样的

内存频率

包括了核心频率,总线频率和传输频率:

核心频率和外频类似,是建立在脉冲震荡信号上的

总线频率就是指内存总线的工作频率。也就是内存和北桥芯片之间的工作频率

传输频率类似FSB,是指实际传输数据的频率

I/O设备

最后一部分简单介绍一下CPU和I/O设备是如何通信的

I/O设备原理

对于程序员来说,关注的只是I/O设备的编程接口

I/O设备分类

- 块设备: 块设备把信息存放在固定大小的块中,每个块都有自己的地址,独立于其他块,可寻址。例如磁盘,USB闪存,CD-ROM等。

- 符号设备:字符设备以字符为单位接收或发送一个字符流,字符设备不可以寻址。列入打印机、网卡、鼠标键盘等

设备控制器

I/O设备由机械部件和电子部件组成,电子部件一般以芯片的形式组成,如南桥芯片,南桥芯片中包含了多种设备的控制器,比如硬盘控制器,USB控制器,网卡、声卡控制器等,通过总线以及卡槽

和设备连接,比如:PCI、USB、SATA(不同的控制器可以控制不同的设备)

驱动程序

对于不同的设备控制器,进行的操作控制也是不同的,需提供专门软件对其进行控制,这类软件称为驱动程序。

内存映射I/O

每个控制器都有几个寄存器和CPU进行通信。通过写入这些寄存器,可以命令设备发送或接受数据,开启或关闭。通过读这些寄存器就能知道设备的状态

寄存器数量和大小有限,所以设备提供RAM缓存来存放数据,比如硬盘的读写缓存,显卡的显存,作用:提供数据存放、提高I/O操作速度

CPU如何和这些设备的寄存器或数据缓冲区进行通信:

方案1:为每个控制器分配一个I/O端口号,放在内存中,OS通过特殊的指令和端口号来从设备读取或是写入数据(早期计算机实现方案)

方案2:将所有控制器的寄存器映射到内存空间,并保证每个设备的寄存器在内存中有唯一的地址,称为内存映射I/O

方案1通过汇编实现,方案2通过C实现

内存映射I/O缺点:

cache可以对内存进行缓存,cache对内存映射I/O缓存会有问题,需提供机制来禁用

CPU和I/O设备数据交换方式

CPU通过内存映射的方式和I/O设备交换数据,对于CPU而言,无论从内存还是I/O读取数据,都需要放到地址总线上。然后在向控制总线传输一个READ信号,

还要1条信息线来表示是从内存还是I/O读取数据。目前有3种方式进行操作:

1.程序控制I/O:CPU向I/O设备发出指令后,通过程序查询方式检查I/O设备是否完成工作,如果完成就读取数据。缺点:CPU在I/O设备完成工作时被占用

2.中断驱动I/O:为使CPU减少I/O等待,在I/O设备工作时,CPU不再等待,而是执行其他操作。通过一个中断信号,通知CPU来处理接下来的工作,如读取数据放到内存,缺点:

每次只能请求一个字节,效率低。

3.DMA:DMAC利用一种特殊芯片存在与CPU和I/O设备之间。大大提高了速度。

内存工作原理

DRAM芯片结构

上图DRAM芯片是一个单元的结构图,1个单元=N个超单元,上图:16个超单元,每个超单元存8位的存储模块。称为16*8bit的DRAM芯片。而超单元(2,1),我们可通过data=DRAM[2.1]

每个超单元的信息通过地址线和数据线传输查找和传输数据。上图有2根地址线和8根数据线连接到存储控制器,为了读取或写入[i,j]超单元的数据,存储控制器需要通过地址线传入行地址i和

列地址j,行地址称为RAS请求,列地址称为CAS请求。

内存编址

一个内存可能是8位,也可能是64位,容量可能是1M,也可能是1G。那么内存是如何编地的呢?和地址总线,计算机字长之间又有什么关系呢?

字长

计算机在同一时间内处理的一组二进制数称为一个计算机的“字”,而这组二进制数的位数就是“字长”。

通常称处理字长为8位数据的CPU叫8位CPU,32位CPU就是在同一时间内处理字长为32位的二进制数据

地址总线

地址总线的数量决定了他最大的寻址范围,如32位计算机最大寻址范围是4G(0x00000000~0xFFFFFFFF)

内存编址

内存的大小和它芯片扩展方式有关,比如内存模块采用16M*8bit的内存颗粒,那么我们使用4个颗粒进行位扩展,成为16M*32bit,使用4个颗粒进行字容量扩展变为64M*32bit。

那么我们内存模块使用了16个内存颗粒,实际大小是256MB

例如内存=256M,我们需要对内存进行编址,以便CPU能够使用它,常用编址方式:

1.按字编址:对于256M,寻址范围=64M,每个内存地址可以存储32bit数据

2.按半字编址:

3.按字节编址:

目前计算机主要采用按字节编址的方式,可以把内存简单的看成一个线性数组,数组每个元素的大小为8bit,我们称为一个存储单元

对于32bit计算机来说,可以容纳2^32个存储单元(B),即4GB

CPU指令

| 操作码字段 | 地址码字段 |

浙公网安备 33010602011771号

浙公网安备 33010602011771号