JZ2440开发笔记(8)——FCLK、HCLK和PCLK

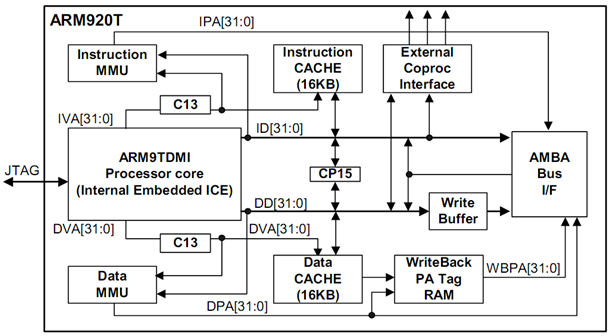

S3C2440中有三种时钟,分别是FCLK,HCLK和PCLK。这三种时钟的功能各不相同,其中FCLK主要是为ARM920T的内核提供工作频率,如图:

HCLK主要是为S3C2440 AHB总线(Advanced High performance Bus)上挂接硬件提供工作频率,AHB总线主要挂接有内存,NAND,LCD控制器等硬件,如图:

PCLK主要是为APB总线提供频率,APB总线上主要挂载UART、WatchDog等硬件控制器,如图:

S3C2440上的时钟源是12MHz,如果想让CPU工作在更高频率上,就需要通过PLL(锁相环)来提高主频。S3C2440上的PLL有两种,一种是MPLL,它是用来产生FCLK、HCLK、PCLK的高频工作时钟;还有一种是UPLL,用来为USB提供工作频率。

从时序图中,我们可以看到,上电之后,如果什么都不设置,FCLK和晶振的频率相等。当设置PLL后,CPU并不是马上就使用设置好的高频时钟,而是有一段锁定时间,在这段时间里,CPU停止运行,等12MHz变成高频时钟稳定以后,整个系统再重新运行。

开启MPLL的过程: 1、设置LOCKTIME变频锁定时间

2、设置FCLK与晶振输入频率(Fin)的倍数

3、设置FCLK,HCLK,PCLK三者之间的比例

从手册上可以看到,LOCKTIME的默认时间是0xFFFFFFFF,控制方法如图:

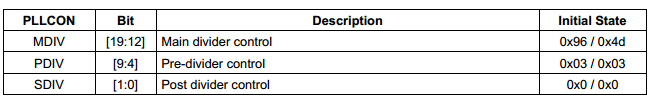

FCLK与Fin的倍数通过MPLLCON寄存器设置,三者之间有以下关系:

MPLL(FCLK) = (2*m*Fin)/(p*2^s)

其中:m = MDIV + 8, p = PDIV + 2, s = SDIV

PLL配置寄存器如图:

当设置完MPLL之后,就会自动进入LockTime变频锁定期间,LockTime之后,MPLL输出稳定时钟频率。

FCLK、HCLK、PCLK的设置比例如图:

而设置HDIVN和PDIVN的值是通过设置CLKDIVN来完成的,如图:

如果HDIV设置为非0,CPU的总线模式要进行改变,默认情况下FCLK = HCLK,CPU工作在fast bus mode快速总线模式下,HDIV设置为非0后, FCLK与HCLK不再相等,要将CPU改为asynchronous bus mod异步总线模式,可以通过下面的嵌入汇编代码实现:

__asm__( "mrc p15, 0, r1, c1, c0, 0\n" /* 读出控制寄存器 */ "orr r1, r1, #0xc0000000\n" /* 设置为“asynchronous bus mode” */ "mcr p15, 0, r1, c1, c0, 0\n" /* 写入控制寄存器 */ );