Verilog Circuits-Combination Logic-Arthmetic Circuits

Problem 65:Half adder

实现一个 2 进制 1bit 加法器,加法器将输入的两个 1bit 数相加,产生两数相加之和以及进位。

module top_module(

input a, b,

output cout, sum );

assign {cout,sum}=a+b;//使用位连接符,省去显示的变量信号声明

endmodule

Problem 66:Full adder

实现一个 2 进制 1bit 的全加器,全加器与上一题中的加法器的区别在于,除了将输入的两个 1bit 的数相加之外,还累加来自前级的进位,产生相加之和和进位。

- 全加器将三维相加并产生和和进位

module top_module(

input a, b, cin,

output cout, sum );

assign{cout,sum} = a + b + cin;

endmodule

- 全加器比半全加器使用更为广泛,这里的 1bit 全加器往往会并行构成更宽的全加器。

Problem 67:3-bit binary adder(Adder3)

实例化三个全加器,将它们级联实现一个位宽 为 3bit 的二进制加法器,加法器将输入的两个 3bit 数相加,产生相加之和以及进位

- 一个 3bit 的全加器由 3 个 1bit 的全加器组成,那么每个 bit 对应一个全加器,假设最低位产生进位,那么最低位的全加器就会输出一个 1'b1 到更高 1bit 的全加器中。信号连接时,最低位的 cout 就是次低位的 cin 信号,以此类推……

module top_module(

input [2:0] a, b,

input cin,

output [2:0] cout,

output [2:0] sum );

adder U1(.a(a[0])

,.b(b[0])

,.cin(cin)

,.cout(cout[0])

,.sum(sum[0])

);

adder U2(.a(a[1])

,.b(b[1])

,.cin(cout[0])

,.cout(cout[1])

,.sum(sum[1])

);

adder U3(.a(a[2])

,.b(b[2])

,.cin(cout[1])

,.cout(cout[2])

,.sum(sum[2])

);

endmodule

module adder(

input a,b,cin,

output cout,sum );//例化1bit全加器

assign {cout,sum}=a+b+cin;

endmodule

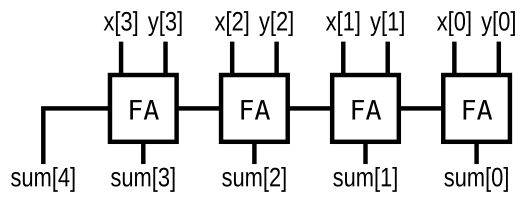

Problem 68:adder

此题是一个 4-bit 全加器,与上一题性质相同,但没有上一题中的限制。

module top_module (

input [3:0] x,

input [3:0] y,

output [4:0] sum

);

// This circuit is a 4-bit ripple-carry adder with carry-out.

assign sum = x+y; // Verilog addition automatically produces the carry-out bit.

// Verilog quirk: Even though the value of (x+y) includes the carry-out, (x+y) is still considered to be a 4-bit number (The max width of the two operands).

// This is correct:

// assign sum = (x+y);

//verilog语法会自动将x+y扩展成5bit数

// But this is incorrect:

// assign sum = {x+y}; // Concatenation operator: This discards the carry-out

endmodule

Problem 69:Signed addition overflow

关于有符号数相加的溢出问题

需要实现一个 2 进制 8bit 有符号数加法器,加法器将输入的两个 8bit 数补码相加,产生相加之和以及进位。

- 负负相加可能会溢出,正正相加可能会溢出

module top_module (

input [7:0] a,

input [7:0] b,

output [7:0] s,

output overflow

); //

assign s = a+b;

//下面开始判断溢出

assign overflow =(a[7]&b[7]&~s[7])|(~a[7]&~b[7]&s[7]);//(正数相加产生溢出变成负数)|(负数相加产生溢出变成正数)

endmodule

Problem 70:100-bit binary adder

创建一个 100bit 的二进制加法器,该电路共包含 两个 100 bit 的输入和一个 cin,输出产生 sum 和 cout

module top_module(

input [99:0] a, b,

input cin,

output cout,

output [99:0] sum );

assign {cout,sum}=a+b+cin;//位宽不同,Verilog会自动补齐

endmodule

Problem 71:4-digit BCD adder

构建一个 BCD 加法器,输入为 2 个 4bit 的 BCD 码,一个 cin,输出 sum 和 cout

给出例化:

module bcd_fadd {

input [3:0] a,

input [3:0] b,

input cin,

output cout,

output [3:0] sum );

要求实例化 4 次 bcd_fadd 来创建一个 4 位 BCD 加法器,共 16bit;同样产生 sum 和 cout

module top_module(

input [15:0] a, b,

input cin,

output cout,

output [15:0] sum );

wire [3:0] carry;

bcd_fadd add1(.a(a[3:0])

,.b(b[3:0])

,.cin(cin)

,.cout(carry[0])

,.sum(sum[3:0])

);

bcd_fadd add2(.a(a[7:4])

,.b(b[7:4])

,.cin(carry[0])

,.cout(carry[1])

,.sum(sum[7:4])

);

bcd_fadd add3(.a(a[11:8])

,.b(b[11:8])

,.cin(carry[1])

,.cout(carry[2])

,.sum(sum[11:8])

);

bcd_fadd add4(.a(a[15:12])

,.b(b[15:12])

,.cin(carry[2])

,.cout(carry[3])

,.sum(sum[15:12])

);

assign cout=carry[3];

endmodule

浙公网安备 33010602011771号

浙公网安备 33010602011771号