Quad-SPI

https://embeddedinventor.com/quad-spi-everything-you-need-to-know/

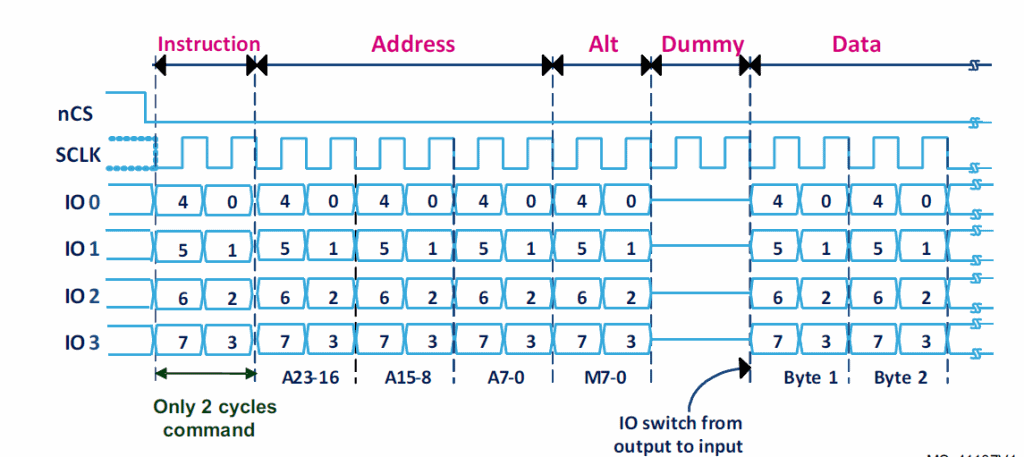

It is faster than traditional SPI as quad-SPI uses 4 data lines (I0, I1, I2, and I3) as opposed to just 2 data lines (MOSI and MISO) on the traditional SPI.

Unlike normal SPI which uses separate data lines for input and output (MISO and MOSI), the Quad-SPI interface configures the data lines on the fly so that they act as outputs if we need to send some information to the flash memory and they can act as inputs if we need to read some memory contents.

It uses 4 data lines namely I0, I1, I2 and I3 as shown in the figure (courtesy STMicroelectronics).

XIP stands for eXecute In Place, it is a feature which allows the microcontroller to execute code straight from the external flash memory without copying it first. This allows for faster and more efficient execution of code.

When the code size gets too big to be stored in the on-chip storage, we usually go for external memory, but the problem with external memory used to be the fact that it was very slow to access. But using Quad-SPI mode and a prefetch mechanism, the data retrieval speed of external flash devices can be made comparable to the on-chip storage and hence can be used to not just store some databases and multimedia but it can be used to execute code too.

Execute in Place Address Mapping

Execute in Place Address Mapping

Some of the advantages of Quad-SPI mode include the following.

- lower pin count as compared to parallel memories, which means there are more GPIO for other uses

- easier to design the PCB which is a direct consequence of lower pin count, which further leads to the lower overall cost of development

- more compact design can be achieved as opposed to parallel memory options

- multiple devices can be linked to a single Quad-SPI interface and the same data lines can be connected to multiple devices. To select a particular chip, the chip select pin can be used. This is an advantage since if we use a parallel memory solution we need a separate set of data lines for each chip we interface with.

- approximately 4 times more throughput can be achieved as compared to SPI

- has support for executing code in place through XIP, which can help increase the code memory and efficiency of complex systems