精简的makefile示例分析

1 make

make 是Linux自带的构建器,构建的规则在makefile文件中

2 makefile文件名

makefile 或 Makefile

3 makefile中的规则

- makefile的规则有三部分:目标,依赖,命令;

- makefile有一条或多条规则组成;

- 第一个目标是makefile的终极目标;

- 用 # 添加注释。

-------------------------------------------------------------------------

目标:依赖

(tab缩进) 命令

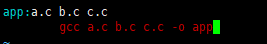

gcc a.c b.c c.c -o app 改为makefile文件如下:

4 makefile的编写

工作原理:依赖不存在,就向下搜索下面的规则,如果找到用来生成查找依赖的规则,就执行规则中的命令;依赖存在,就判断是否需要更新

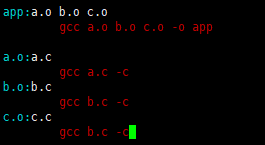

第一版:改为多条规则如下,可以实现只有修改的文件才重新编译。

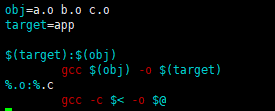

第二版:使用自定义变量,减少冗余

a.自定义变量:

obj=a.o b.o c.o

obj=10

b.变量的取值:

aa=$(obj)

c. makefile自带的变量:大写

CPPFLAGS

CC

d. 自动变量:只能在命令中使用

$@ : 规则中的目标

$< : 规则中的第一个依赖

$^ : 规则中的所有依赖

e. 模式匹配:

%.o:%.c

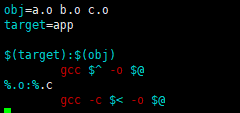

第三版:全部改为自定变量。

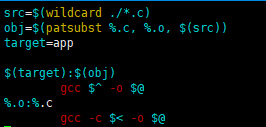

第四版:使用函数,实现makefile文件在不同的项目中通用。makefile所有的函数都有返回值。

a. 查找指定目录下指定类型的文件

src=$(wildcard ./*.c)

b. 匹配替换

obj=$(patsubst %.c, %.o, $(src))

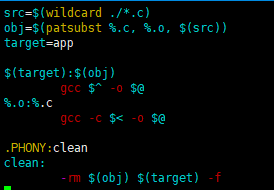

第五版:添加清理项目功能。只需要添加一个新的规则:clean即可,注意:clean应该名声为伪目标。

a. 使用.PHONY声明伪目标,如果clean不声明为伪目标,并且目录下有一个文件名为clean的文件,那么make clean就永远不会执行。

b. rm命令前面添加一个 - 号,表示命令执行失败时,继续向下执行。

src=$(wildcard ./*.c)

obj=$(patsubst %.c, %.o, $(src))

target=app

$(target):$(obj)

gcc $^ -o $@

%.o:%.c

gcc -c $< -o $@

.PHONY:clean

clean:

-rm $(obj) $(target) -f