IIC初学习

IIC总线

IIC历史:

IIC是集成电路总线

IIC是主从模式总线,一种简单的,双向的二进制的串行总线

3. 低速,串行,串行数据,串行时钟等信号总线,半双工总线。

4. 目前速率100k~400Kbit/s

架构

IIC架构是主从架构,每次读写都是由master发起。每次读取或写入1byte,都需要slave端回应ACK/NACK。如果是多个master,需要引入仲裁机制。Slave端设备地址有7bits(常用)与10bits之分。7bits可以外挂128个次设备。10bits可以外挂1024个设备。

备注:总线电容最大是400pF,管教都是有电容的,PCB上也有电容,经验值外挂设备一般为8个。

IIC的GPIO一般为开漏输出,故需要外部上拉。

电阻与电容构成RC滤波电容,电容越大,信号边沿越缓。

数据信号线与时钟信号线在空闲的时候为高。

低电平:<0.33Vdd 高电平 >0.7Vdd

而且外挂设备地址是静态地址。

线与功能

线与:所有GPIO输出高就是高,只要一个输出低,整条线上面都是低。

开漏输出结构满足此要求。

推挽输出不满足此线与要求

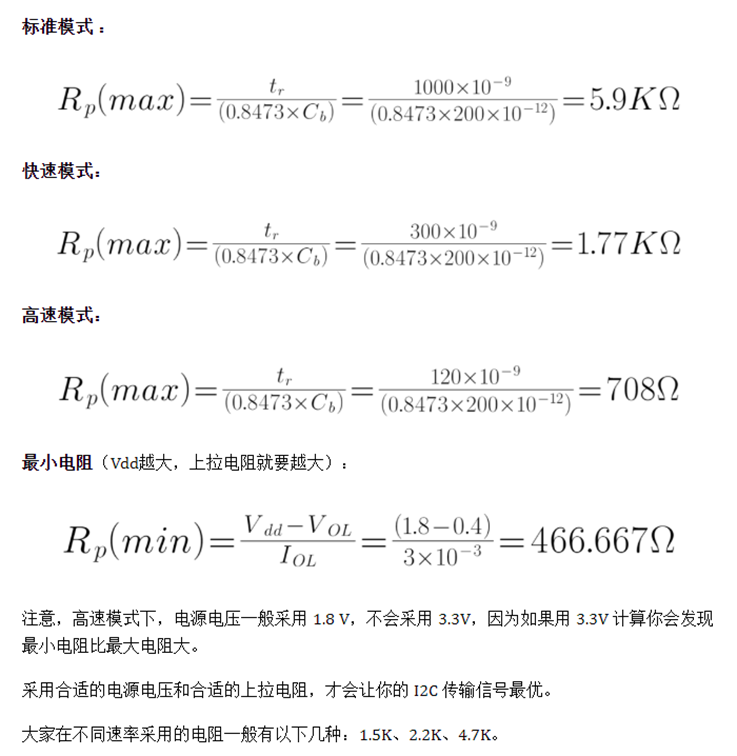

上拉电阻计算

1、上拉电阻过小,电流大,端口低电平 level 增大,会发现总线上电平拉不到 0V。

2、上拉电阻过大,上升沿时间增大,方波可能会变成三角波。

因此计算出一个精确的上拉电阻阻值是非常重要的。计算上拉电阻的阻值,有明确计算公式:

最大电阻和上升沿时间 tr 、总线电容 Cb 、标准上升沿时间 0.8473 有关

最小电阻和电源 Vdd 电压、GPIO 最大输出电压 Vol、 GPIO 最大电流 Vol 有关。

假设:Vdd 是 1.8V,Cb 总线电容 200pF(虽然协议规定负载电容最大 400pF,实际上超过 200pF波形就很不好,我们以 200pF 来计算,实际大家使用时建议以 100pF 计算)

图 1 IIC匹配电阻

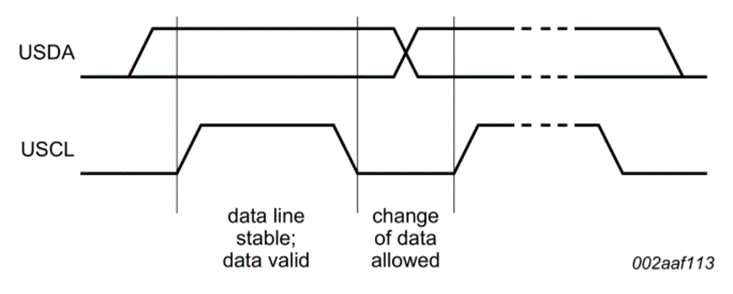

数据有效性

在 SCL 高电平期间,SDA 必须稳定,所以一般情况下,SCL 高电平宽度小,SDA 高电平宽度大,用示波器看也是这样的。

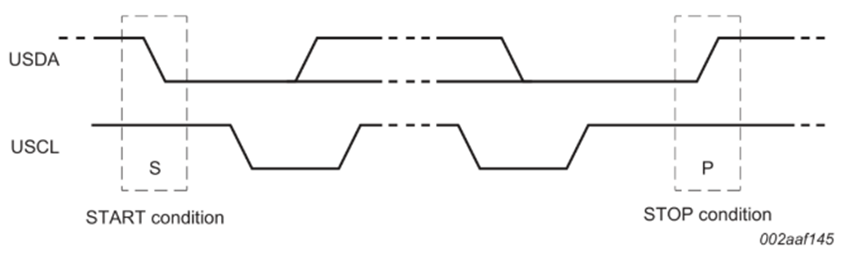

起始条件和停止条件

起始条件:SCL 高电平时,SDA 由高变低。

停止条件:SCL 高电平时,SDA 由低变高。

note:因为 SCL 和 SDA 两根线有上拉电阻,因此空闲时两根线为高电平。因此,START 条件一定是某条线拉低,spec 规定是 SDA 线拉低为开始条件。这也是开始条件和停止条件不能互换的原因。

图 3 IIC开始与结束的时序

传输长度必须是一个字节(8 bit)

每次传输的字节不受限制

数据必须以 MSB 开头进行传输,也就是先传输最高位

从机可以将时钟线 SCL 保持在低位,迫使主机进入等待状态。

在 ACK 后,从设备可以拉低 SCL 线进行时钟延展(比如从设备需要准备数据等)

note:SCL 高电平的时候,SDA 开始采样,SDA 是高就是 1,是低就是 0。SCL 低电平期间,SDA 变换数据。不可以在 SCL 高电平期间变换数据,否则会认为是 起始和停止条件。

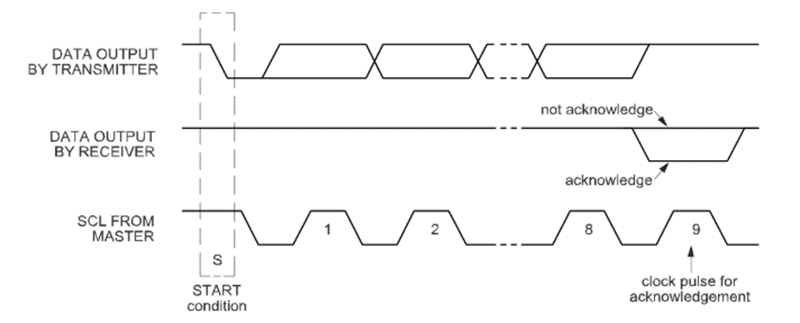

ACK与NACK

每次传输完一个字节以后,从设备要进行一个回应,回应 ACK 或者 NACK。

ACK :在传输 8 bit 以后,在第九个 bit ,SCL 高电平,如果 SDA 是低电平,说明回应了 ACK。

NACK:在传输 8 bit 以后,在第九个 bit ,SCL 高电平,如果 SDA 是高电平,说明回应了 NACK。

图 4 IIC应答时序波形

spec 规定以下五种情况会出现 NACK

主机发送到总线上的地址,却没有匹配的从机,因此出现 NACK

从机处于 busy 状态,出现 NACK

在传输过程中,从机获取其不理解的数据或命令。

在传输过程中,从机无法再接收任何数据字节。

主接收机必须向从发射机发送传输结束的信号的时候,会出现 NACK。

补充

I2C 不支持从设备在 SCL 和 SDA 总线上发起一个中断,通知主设备来读数据。有中断需求的从设备需要额外接一根中断线,通知主控数据已经准备好,让主控发起读数据的操作。这无疑增加了系统复杂性,多占用了 pin 脚。I3C 则不存在这种问题。I3C 允许从设备在 SCL 和SDA 上发起中断,叫“带内中断”。