N76E003系统时钟

系统时钟源

N76E003共有3种系统时钟源,包括: 内部高速/低速振荡器、外部输入时钟。它们每一个都可以作为N76E003的

系统时钟源。开启不同的时钟源可能会影响到多功能引脚P3.0/XIN 。

内部振荡器

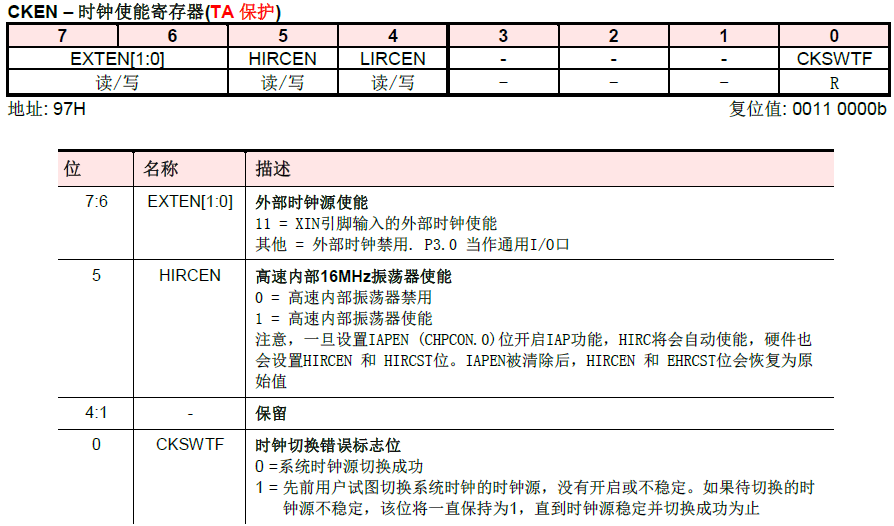

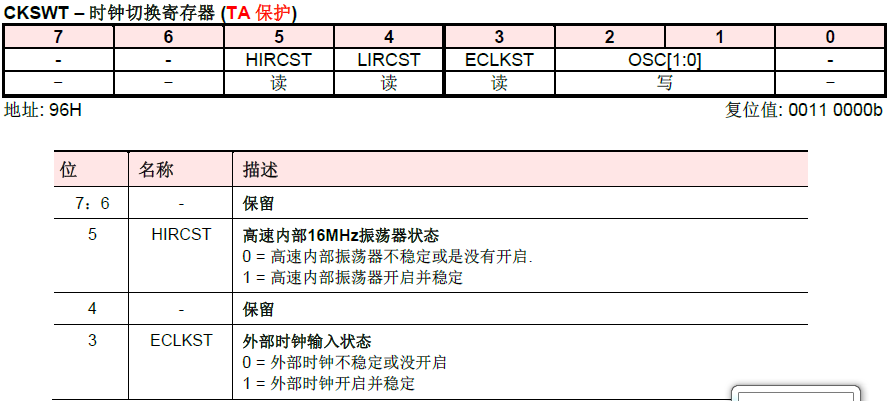

N76E003内部有两个RC振荡器,一个高速16MHz(HIRC)和一个低速10 kHz(LIRC)。它们都可被选择用作

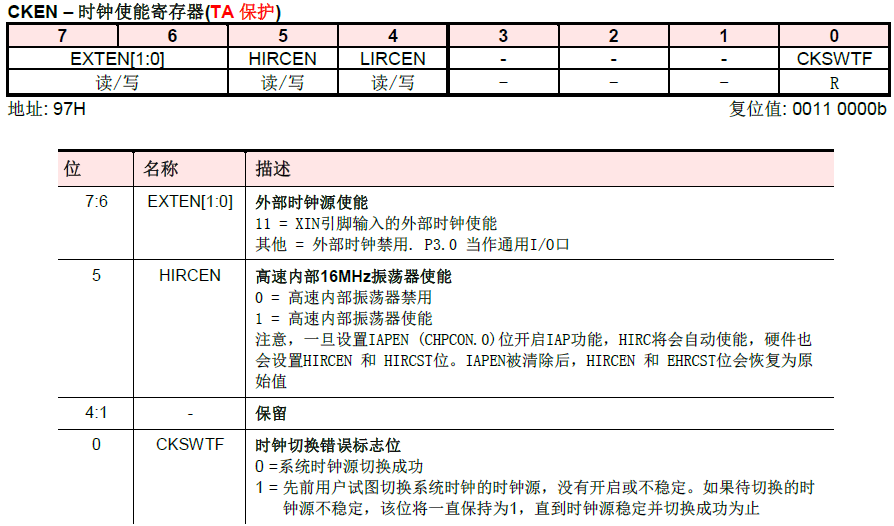

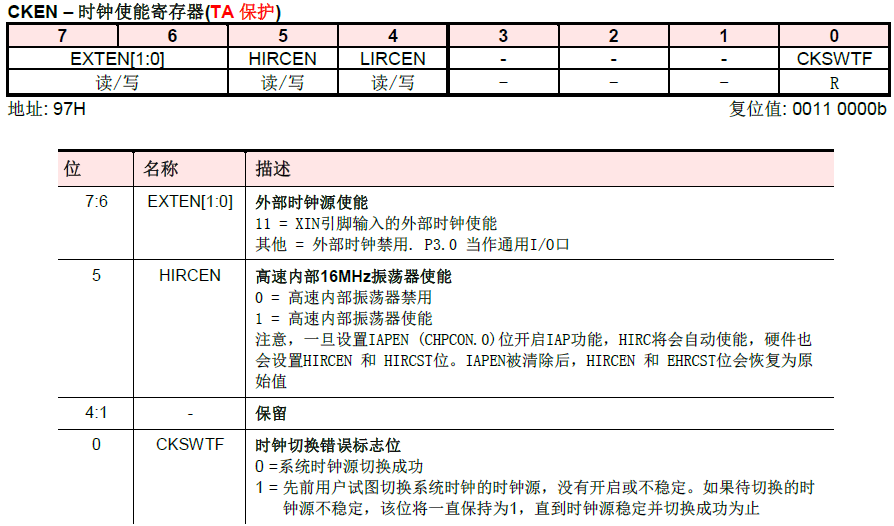

系统时钟。通过设置HIRCEN (CKEN.5)位使能HIRC,设备上电时LIRC被使能。用户可设置OSC[1:0] (CKSWT

[2:1])为[0,0]选择HIRC作为系统时钟,设置OSC[1:0](CKSWT [1:0])为[1,0]选择LIRC作为系统时钟。注意:

N76E003上电后HIRC 和 LIRC都被使能,并且系统默认HIRC为系统时钟。当系统使用内部振荡器作为时钟源

时,XIN 自动作为普通I/O P3.0,用来扩展普通I/O数量。可以通过配置P3M1和P3M2寄存器来选择P3.0的输出模式。

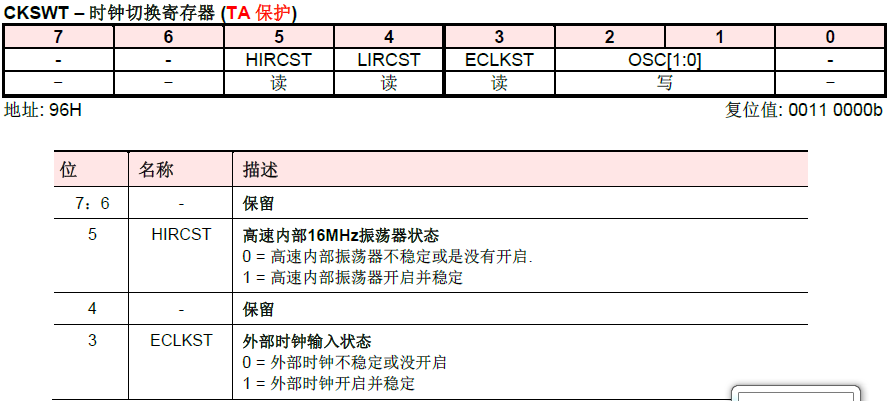

23.2 系统时钟切换

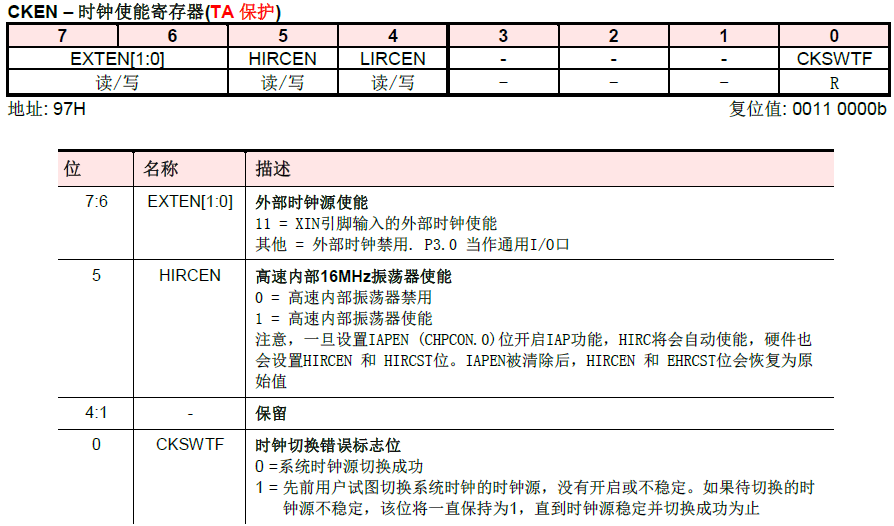

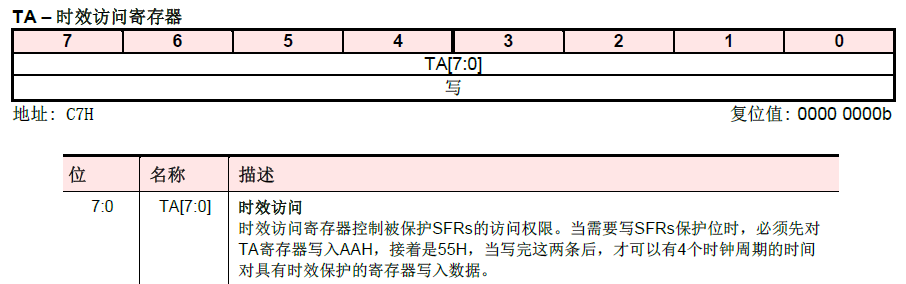

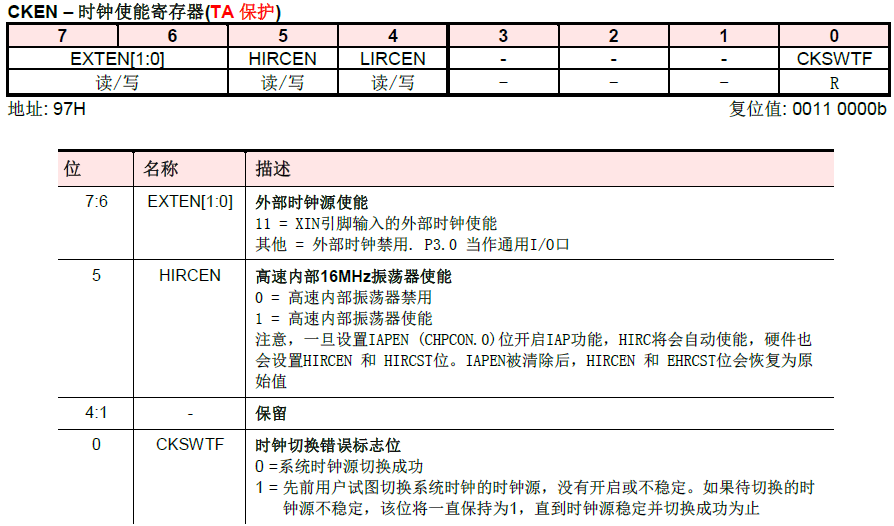

N76E003可以通过软件设置CKSWT 和 CKEN寄存器切换时钟源。这给应用带来了很大方便。注意,这些特殊寄存器是写时效访问控制受TA保护寄存器。

在时钟源控制下,时钟源可以在外部时钟、内部时钟,甚至内部高速与低速之间自由的切换。

然而在切换时钟源时,必须确保待切换时钟源已稳定。因此,用户需要遵循以下设置步骤才能成功完成时钟源切换。

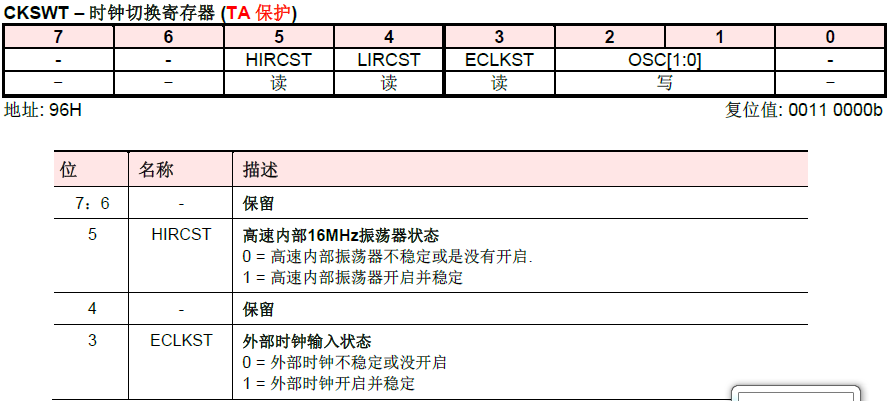

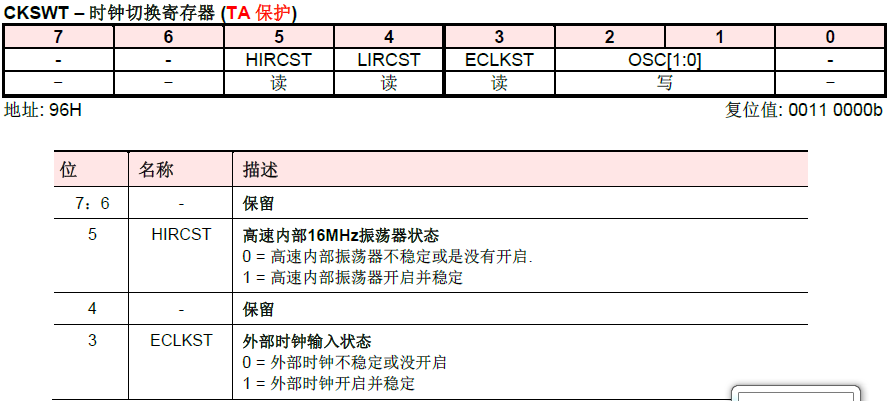

用户首先要通过配置CKEN寄存器打开目标时钟源,再通过查询CKSWT寄存器中对应的标志位,确定时钟源是否稳定,并且通过写OSC[1:0] (CKSWT[2:1])切换到目标时钟源。

这些步骤过后,将会成功的切换时钟源。如果用户关心功耗的话,可以将原先时钟源关闭了。如果不遵守以上步骤,硬件将会采取以下一些措施来应对这些违规的操作。

1.如果用户试图改变CKEN的值来关闭当前时钟源,设备将忽略这个操作。系统时钟维持现状,CKEN值不变。

2.如果用户试图改变OSC[1:0]的值来切换系统时钟,而待切换新时钟源未被打开,OSC[1:0]值将会被立即更新,但是系统时钟保持不变,CKSWTF (CLKEN.0)会被硬件置位。

3.如果用户切换系统时钟源,但是目标时钟源已经打开还没稳定,那么硬件会等待目标稳定后,再切换过去。在等待期间,设备继续以原来时钟源工作,并且CKSWTF会被置1。等到目标时钟源稳定后,标志位(见 CKSWT[7:3])被置位,时钟将会成功切换,CKSWTF会被硬件自动清0。

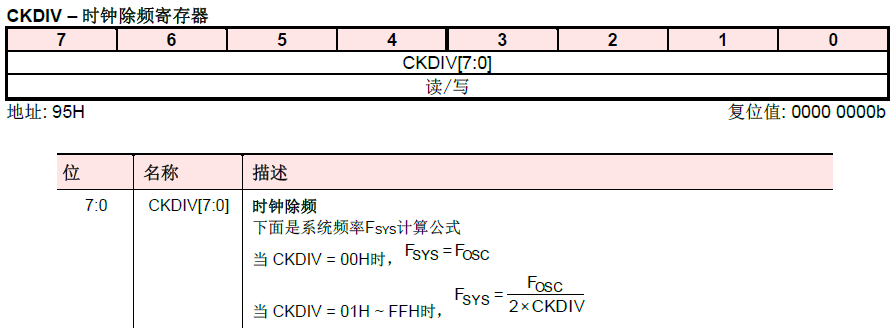

系统时钟除频

振荡频率(FOSC)通过配置除频寄存器CKDIV,整数倍(最大到1/510)除频后,再供给系统作为系统时钟(FSYS)。这一特征可以临时让MCU跑在很低的速度下来降低功耗。通过时钟除频,可以让MCU在正常工作模式下,很低的速度运行,确保其及时能够响应中断事件(比如空闲模式只能通过中断事件退出)。这有可能比空闲模式还要省电。这样,可以避免掉电模式情况下,需要等待振荡器重新起振的时间。CKDIV的值可以在任何时间被程序改变,除了不能在中断服务程序里改变。

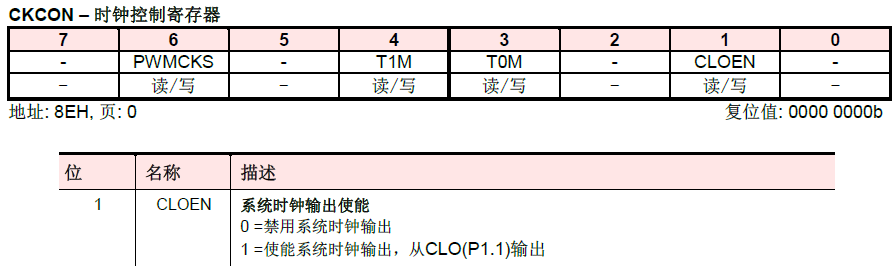

系统时钟输出

系统时钟输出

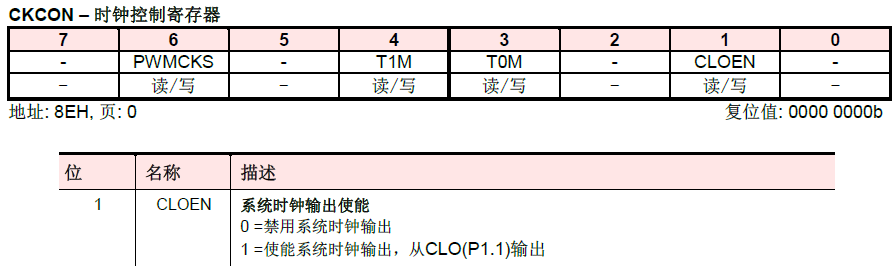

N76E003提供一个CLO(P1.1)引脚可以输出系统时钟,该频率与FSYS 频率相同。通过设置CLOEN (CKCON.1)位打开这个功能。在掉电模式下CLO输出会停止,因为系统时钟已被关闭。注意当有干扰问题或是功耗问题时,用户最好关闭CLO输出。

用户首先要通过配置CKEN寄存器打开目标时钟源,

再通过查询CKSWT寄存器中对应的标志位,确定时钟源是否稳定,并且通过写OSC[1:0] (CKSWT[2:1])切换到目标时钟源。

#include "N76E003.h" #include "SFR_Macro.h" #include "Function_define.h" #include "Common.h" #include "Delay.h" //======================================================================== // The test process: // 1. Power on is run as default HIRC, show LED Fsys tickle faster // 2. toggle P3.0 to GND. // 2. call modify Fsys code to LIRC. // 3. LED tickle speed slowly than before. //======================================================================== void main(void) { /* Note MCU power on system clock is HIRC (16 MHz) Please keep P3.0 HIGH before you want to modify Fsys to LIRC */ Set_All_GPIO_Quasi_Mode; // In Common.h define set_CLOEN; // Also can check P1.1 CLO pin for clock to find the Fsys change. set_P30; while (P30) // when P3.0 keep high, clock out HIRC { clr_GPIO1; // Check LED output tickle time Timer0_Delay1ms(200); set_GPIO1; Timer0_Delay1ms(200); } ////------------------------------------------------------------------------------------------------------ ///*********************************** Change system closk source ***************************************/ ////------------------------------------------------------------------------------------------------------ ////***** HIRC enable part ***** // set_HIRCEN; //step1: enable HIRC clock source run // while((CKSWT&SET_BIT5)==0); //step2: check ready // clr_OSC1; //step3: switching system clock source if needed // clr_OSC0; // while((CKEN&SET_BIT0)==1); //step4: check system clock switching OK or NG // ////***** LIRC enable part***** ////** Since LIRC is always enable, switch to LIRC directly set_OSC1; //step3: switching system clock source if needed clr_OSC0; while((CKEN&SET_BIT0)==1); //step4: check system clock switching OK or NG clr_HIRCEN; ////-------------------------------------------------------------------------------------------------------- /* Now Fsys = LIRC , LED tickle slowly. */ while(1) { clr_GPIO1; // Check LED output tickle time clr_P00; set_GPIO1; set_P00; } /* =================== */ }

#define set_CLOEN CKCON |= SET_BIT1

set_CLOEN;

#define set_P30 P30 = 1 #define clr_P30 P30 = 0

////***** HIRC enable part ***** // set_HIRCEN; //step1: enable HIRC clock source run // while((CKSWT&SET_BIT5)==0); //step2: check ready // clr_OSC1; //step3: switching system clock source if needed // clr_OSC0; // while((CKEN&SET_BIT0)==1); //step4: check system clock switching OK or NG // ////***** LIRC enable part***** ////** Since LIRC is always enable, switch to LIRC directly set_OSC1; //step3: switching system clock source if needed clr_OSC0; while((CKEN&SET_BIT0)==1); //step4: check system clock switching OK or NG clr_HIRCEN;

set_HIRCEN;

用户首先要通过配置CKEN寄存器打开目标时钟源

#define set_HIRCEN BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;CKEN|=SET_BIT5;EA=BIT_TMP;

while((CKEN&SET_BIT0)==1); //step4: check system clock switching OK or NG

确定时钟源是否稳定

并且通过写OSC[1:0] (CKSWT[2:1])切换到目标时钟源

set_OSC1; //step3: switching system clock source if needed

clr_OSC0;

#define set_HIRCST BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;CKSWT|=SET_BIT5;EA=BIT_TMP; #define set_LIRCST BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;CKSWT|=SET_BIT4;EA=BIT_TMP; #define set_ECLKST BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;CKSWT|=SET_BIT3;EA=BIT_TMP; #define set_OSC1 BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;CKSWT|=SET_BIT2;EA=BIT_TMP; #define set_OSC0 BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;CKSWT|=SET_BIT1;EA=BIT_TMP; #define clr_HIRCST BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;CKSWT&=~SET_BIT5;EA=BIT_TMP; #define clr_LIRCST BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;CKSWT&=~SET_BIT4;EA=BIT_TMP; #define clr_ECLKST BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;CKSWT&=~SET_BIT3;EA=BIT_TMP; #define clr_OSC1 BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;CKSWT&=~SET_BIT2;EA=BIT_TMP; #define clr_OSC0 BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;CKSWT&=~SET_BIT1;EA=BIT_TMP;

while((CKEN&SET_BIT0)==1); //step4: check system clock switching OK or NG

判断是否稳定