I.MX RT 时钟控制模块(CCM)

|

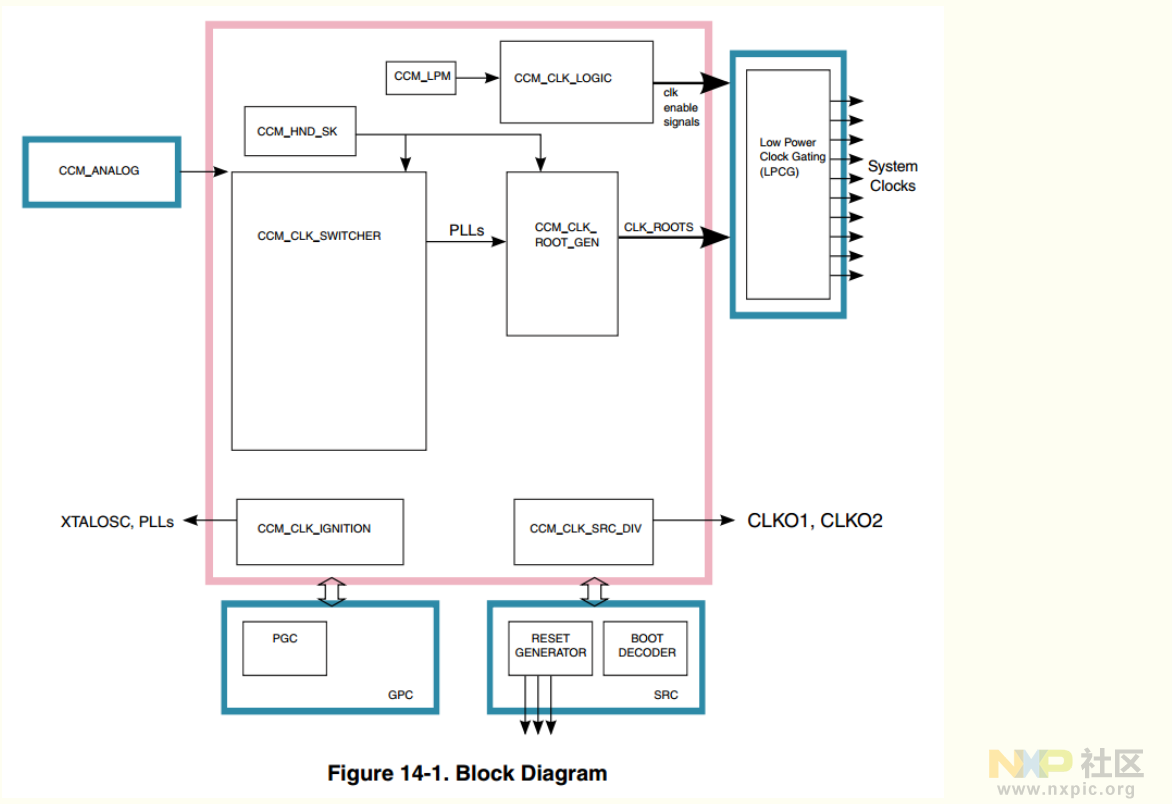

RT1052 的时钟系统由时钟控制模块 CCM 进行控制,其主要功能如下: 1)使用 PLL 锁相环电路将参考时钟倍频,得到频率更高的时钟。为芯片内核和外设提供可选的时钟源。 RT1052 共有 7 个 PLL 锁相环电路, 分别为 ARM PLL(PLL 1)、System PLL(PLL 2)、 USB1 PLL(PLL 3)、 Audio PLL(PLL 4)、 Video PLL(PLL 5)、ENET PLL(PLL 6) 、 USB2 PLL(PLL 7)。 2)提供 PLL 控制寄存器、时钟选择寄存器、时钟分频寄存器 灵活控制输出到外设和内核的时钟频率。 3)控制低功耗机构。 2 时钟控制模块结构构图 <ignore_js_op>

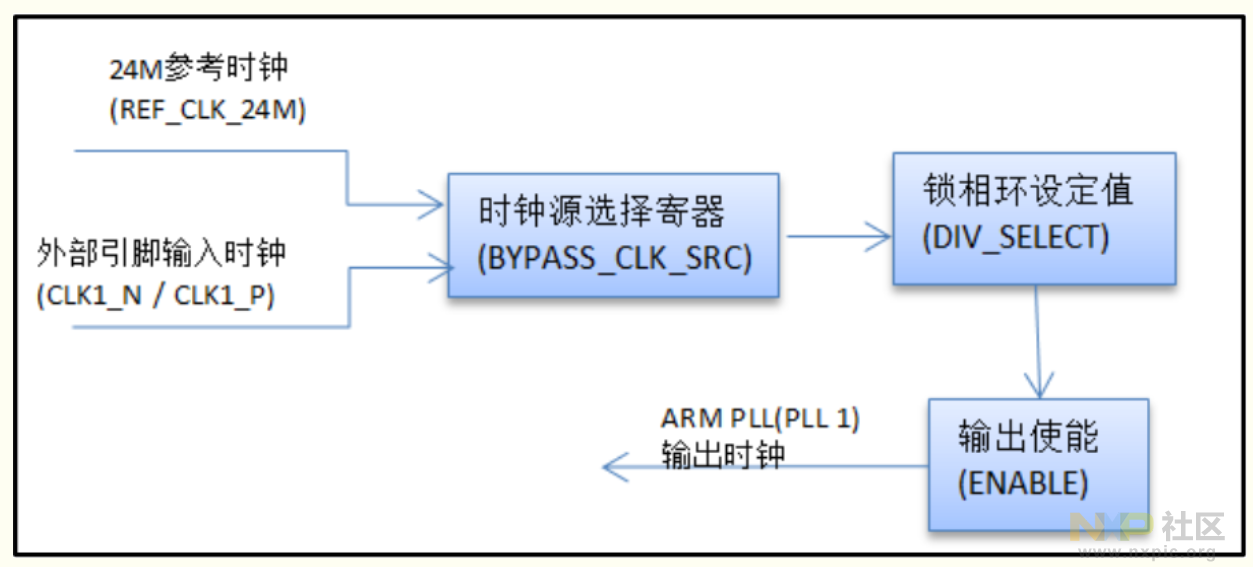

CCM_CLK_IGNITION 管理从外部晶振时钟到稳定的根时钟输出的整个过程。 CCM 完成重置之后 CCM_CLK_IGNITION 模块立即启动。 GPC 是 General Power Controller 的缩写, 即总电源管理模块,它不属于 CCM,系统电压与时钟关系密切,简单来说,系统电压影响系统最高的时钟频率, CCM 又可以控制总电源管理模块(GPC)进入待机或低功耗状态。 1. ②PLL 时钟产生 CCM_ANALOG 为 CCM 的模拟部分,作用是将频率较低的参考时钟(例如 24MHz 的XTALOSC 时钟)使用 PLL 锁相环电路倍频到更高的时钟。 CCM_CLK_SWITCHER 模块接收来自 CCM_ANALOG 模块的锁相环时钟输输出,以及锁相环的旁路时钟,并为CCM_CLK_ROOT_GEN 子模块生成切换时钟输出(pll3_sw_clk)。 RT1052 共有 7 个 PLL 锁 相环电路, 可以独立配置。其中 PLL2 与 PLL3 结合 PFD 能够输出多个频率可调的时钟。 2. ③根时钟生成 CCM_CLK_ROOT_GEN 接收来自 CCM_CLK_SWITCHER 模块的 PLL 或 PFD 时钟,经过时钟的选择、分频等操作之后产生并输出根时钟。根时钟将会作内核或外设的时钟源。 3. ④时钟同步 当更改某些时钟的时钟源时需要进行时钟的同步 CCM_HND_SK 模块用于管理时钟握手,即时钟的同步。 4. ⑤低功耗管理与时钟启用模块 CCM_LPM 用于管理低功耗模式,管理时钟的开启与关闭。 CCM_CLK_LOGIC,根据来自 CCM_LPM 模块和 CCM_IP 的信号产生时钟启用或关闭信号。 5. ⑥低功耗时钟门控模块(LPCG) 低功耗时钟门控模块(LPCG)根据 CCM_CLK_LOGIC 模块输出信号控制时钟输出。时钟越多、频率越高功耗也就越高。关闭没有使用的时钟或降低时钟频率能够有效的降低功耗 。 3 时钟树简介 RT1052 芯片时钟的结构以时钟树的方式进行描述。当我们设置外设时钟时大多会参考时钟树进行设置。 1. ①时钟转换器 CLOCK SWITCHER RT1052 外部连接了两个晶振,分别用于提供 32.768KHz 和 24MHz 时钟。其中32.768KHz 晶振称为外部低速时钟(CKIL),当芯片上电后要保持该时钟一直处于运行状 态, 为需要的外设提供时钟。 32.768KHz 时钟主要为芯片的实时时钟外设(RTC)提供时钟源,若不使用 RTC,可以不提供该时钟。 24Mhz 晶振产生的时钟称为外部高速时钟(CKIH) , 芯片利用内部振荡器产生基准时钟(OSC), 内部振荡器产生基准时钟(OSC)与外部高速时钟(CKIH)连接, 产生 24MHz 的参 考时钟。24MHz 参考时钟常用作 PLL 锁相环电路的输入时钟。下面以 ARM PLL(PLL 1)为例讲解从 24MHz 参考时钟到 ARM PLL(PLL 1)时钟的过程 <ignore_js_op>

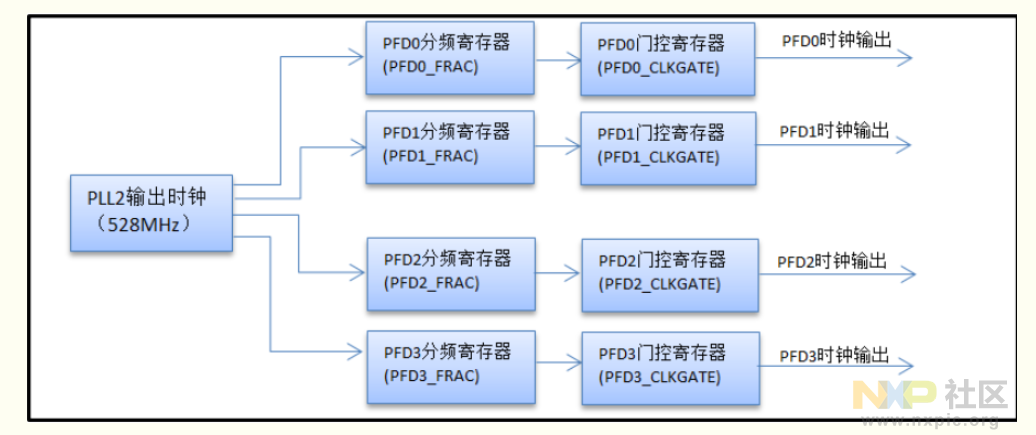

ARM PLL(PLL 1)只有一个控制寄存器 CCM_ANALOG_PLL_ARMn,CCM_ANALOG_PLL_ARMn[BYPASS_CLK_SRC]用于选择输入钟源(Fin), 一般我们使用24MHz 参考时钟,当然也可以选择外部引脚输入引脚(CLK1_N / CLK1_P)输入的外部时 钟。 CCM_ANALOG_PLL_ARMn[DIV_SELECT]位选择锁相环分频值(DIV_SELECT)。取值范围为 54 到 108。输出频率计算公式为 ARM_PLL = Fin * DIV_SELECT/ 2.0。如果选择 24MHz 参考时钟作为时钟输入, DIV_SELECT 选择 88 则 ARM PLL 的输出频率为1056MHz。 CCM_ANALOG_PLL_ARMn[ENABLE]用于配置是否使能 ARM PLL 输出,如 果要使用 ARM PLL 就需要将该位设置为 1 。 PLL2 与 PLL3 下方各有一组 PFD。 PFD 是 Phase FractionalDividers 的缩写,我们这里翻译为分数分频。 PFD 的频率由 PLL2 或 PLL3 输出频率分频产生。 <ignore_js_op>

寄存器 CCM_ANALOG_PFD_528n 用于控制 PFD0~PFD3 的输出频率。以 PFD0 为例,CCM_ANALOG_PFD_528n[PFD0_FRAC]用于设置分频值,取值范围为 12 到 35, PFD0 的 输出频率计算公式为: PFD0_out =528*18/ PFD0_FRAC 如果 PFD0_FRAC = 27, PFD0 的输出频率为 352MHz。CCM_ANALOG_PFD_528n[PFD0_CLKGATE]门控寄存器,用于设置是否使能 PFD0的输出。 2. ②根时钟生成模块 CLOCK ROOT GEN 根时钟生成模块主要完成两个工作,第一选择时钟,第二设置时钟分频。 时钟转换器(CLOCK SWITCHER)输出了多个频率不同的 PLL时钟。每个外设时钟通过 MUX 模块连接到多个 PLL 时钟输出,每个 MUX 实际是一个寄存器,用于选择时钟源。 |