i.MX RT1050 Memory Management

i.MXRT1052 支持多种选择,通过 EMC/SEMC、FlexRAM、FlexSPI 或 SD/eMMC/SDIO 卡接口使用和扩展系统内存

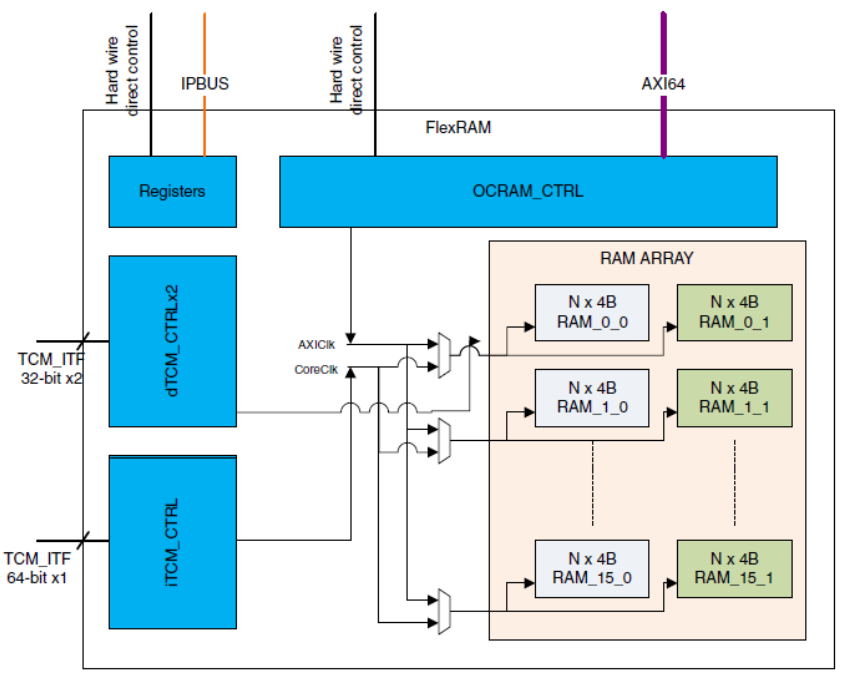

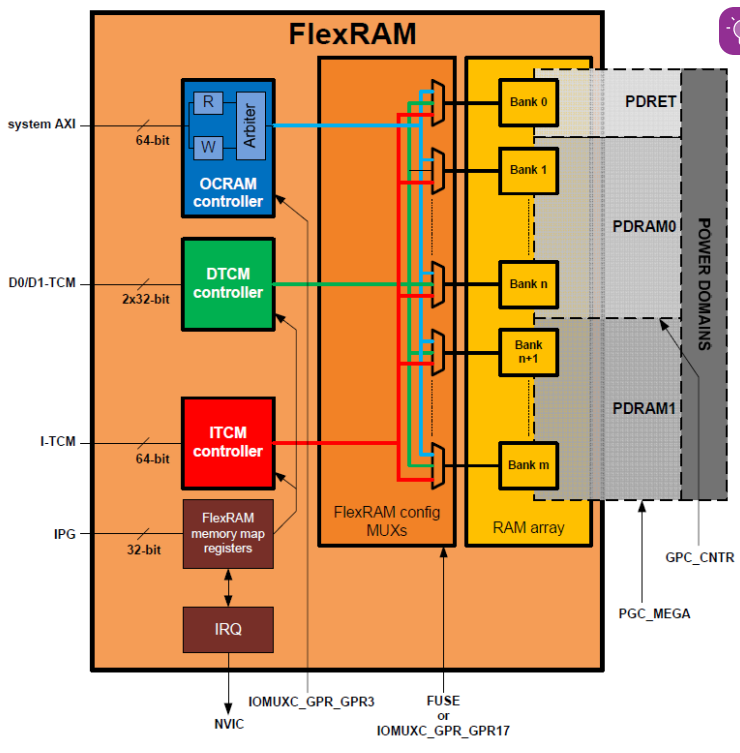

将 AXI / TCM 接口信号转换为 RAM 接口信号

− 实现 OCRAM、DTCM 和 ITCM 访问片上 RAM 的多路复用器控制

− 3 个用于 I-TCM、DTCM 和 OCRAM 的集成 RAM 控制器,通过专用总线接口

− 片上 RAM 可灵活划分为 TCM、OCRAM 存储器

− 3 个电源域分配给专用组或组组以降低功耗

− 时钟源从 6MHz(默认)到最大 600MHz(对 flexram_clk、ocram_clk 有效)

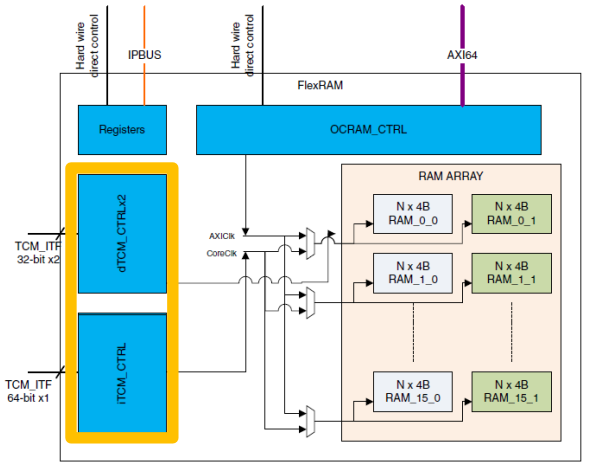

Integrated I-TCM and D-TCM controller

将 TCM 接口信号转换为 RAM 访问信号

− 64 位 I-TCM 接口和 2x32 位 D-TCM 接口

▪ 支持高达 16MB TCM(I-TCM 和 DTCM)空间

− 支持两种访问模式:

▪ 快速模式:1 周期 R/W 访问(默认)

▪ 等待模式:2 周期 R/W 访问(可通过 TCM_CTRL 启用

寄存器)

− 与以相同频率运行的 M7 Core 的同步接口

− 自动时钟门控控制以降低功耗

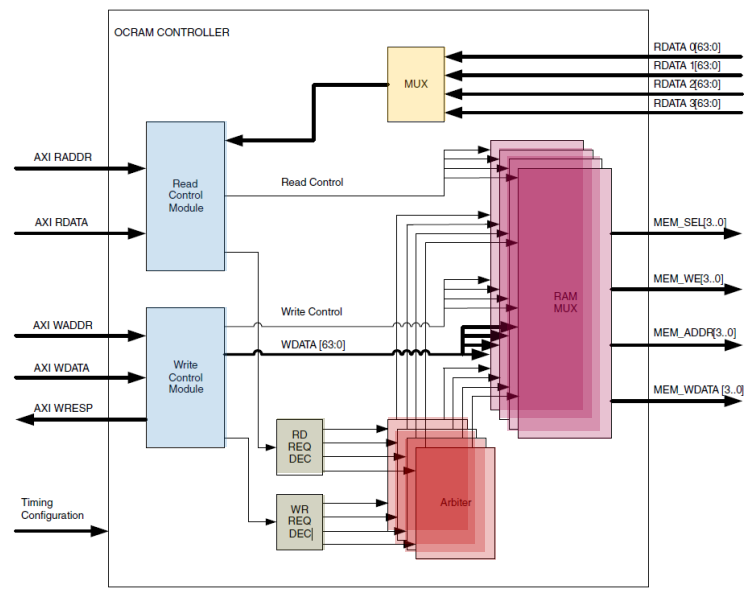

将 AXI 接口信号转换为 RAM 访问信号

− 支持高达 512KB SRAM 的单组控制器

− 包含 2 个独立控制单元,用于专用 R/W 访问

− 集成循环仲裁器以控制同时 R/W 访问

在同一个 RAM 银行

▪ 无需调用仲裁器即可同时 R/W 访问不同的 RAM bank

▪ 针对相同的 RAM bank 时,READ 优先于 WRITE

− 与系统总线同步,与总线同频运行

− 允许为 R/W 访问配置时序参数

▪ 可通过 OCRAM_CTL[3:0] 位中的 IOMUXC_GPR_GPR3 进行配置

▪ 启用时提供 3 种计时模式:

• R/W 地址流水线 - 来自 AXI 主机的 R/W 地址字延迟 1 个时钟周期

• 写入数据流水线 - 来自 AXI 主机的 WRITE 数据字延迟 1 个时钟周期

• 读取数据等待状态 - 2 周期读取访问

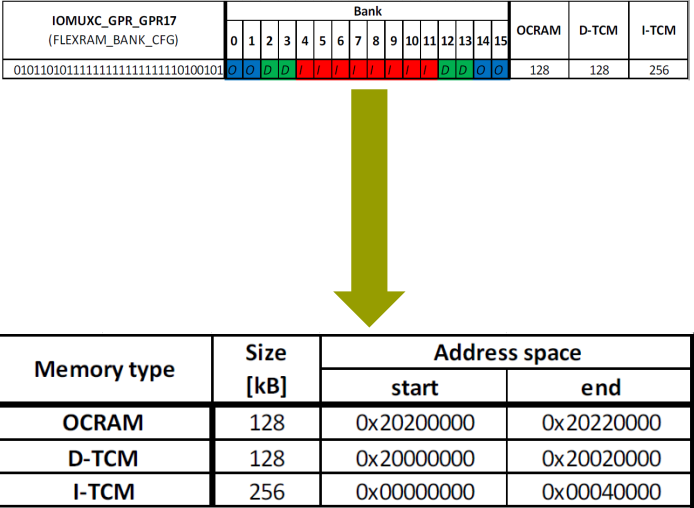

RAM 阵列分区

− ITCM、DTCM 和 OCRAM 的可配置大小(0 至 512kB)

▪ 通过IOMUXC_GPR 寄存器,每个bank 2bits

− 最小的 RAM 分区为 32kB,最多可形成 16 个 RAM bank

− 灵活的 RAM 银行组织(但不允许重叠)

− 根据设备内存映射分区产生连续的地址空间

• 访问控制

− Bank8-15 可以通过硬件熔断器禁用(最大 RAM 大小为

256KB)

− 当 OCRAM/ITCM/DTCM 访问超出时产生中断

配置的 RAM 范围

− 访问配置的 OCRAM、ITCM 或

发生 DTCM 地址(在 *_MAGIC_ADDR 寄存器中分配)

− OCRAM、ITCM 和 DTCM 的独立地址控制

− 基于寄存器设置的读或写访问中断生成

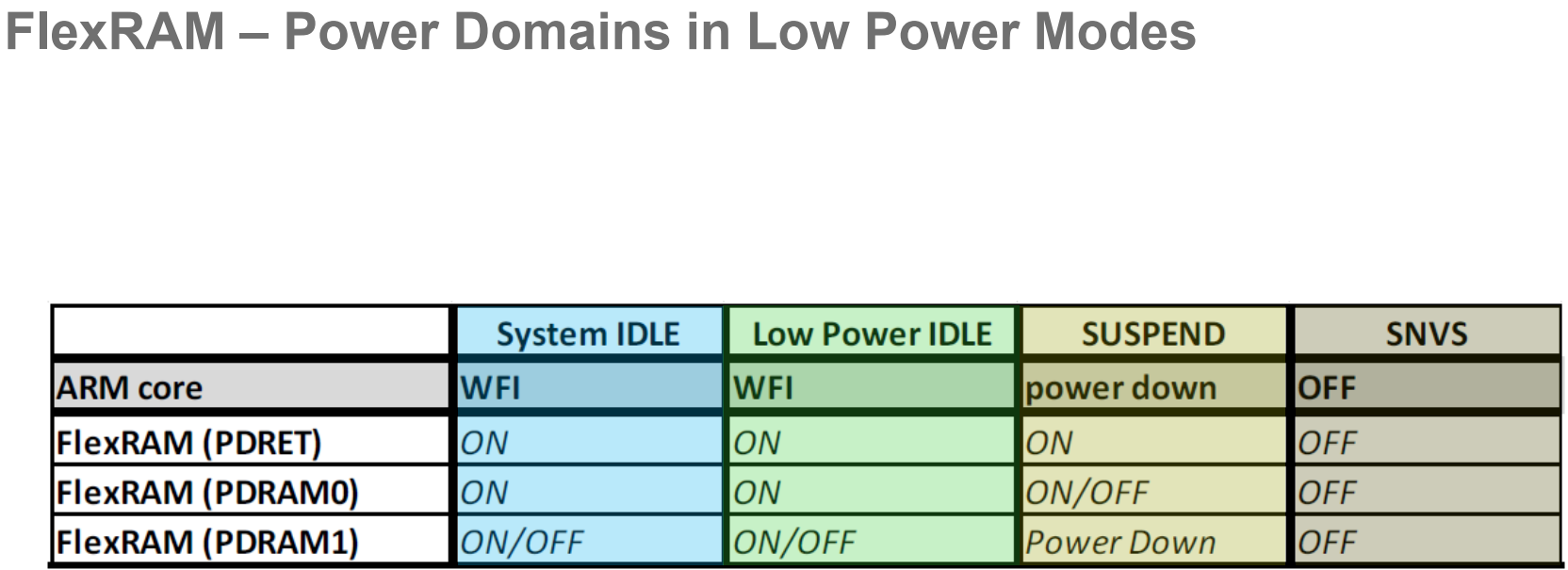

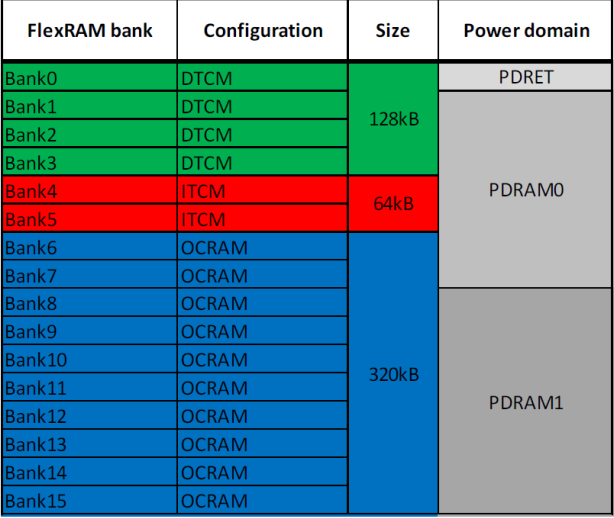

3 个电源域 PDRET、PDRAM0 和 PDRAM1 支持低功耗模式

− 通过 GPC 和 PGC 单元启用/禁用电源域

▪ PDRET

• 仅 RAM bank 0 (32kB),除 SNVS 模式外始终开启

▪ PDRAM0

• RAM bank 1-7 (224kB),通过 GPC_CNTR 寄存器中的 PDRAM0_PGE 位打开/关闭电源

• 当 PDRAM0_PGE 置位时,PDRAM0 在 ARM 内核断电时保持活动状态

▪ PDRAM1

• RAM bank 8-15 (256kB),通过 PGC_MEGA 寄存器中的电源门控控制

• 通过 PGC_MEGA_PDNSCR、PGC_MEGA_PUSCR 寄存器的电源时序时序

• 通过 PGC_MEGA_CTRL 寄存器的电源控制选项,在电源关闭 PDRAM1

向下请求

− 操作模式:

▪ 运行模式 - 所有 RAM 库都已通电

▪ 保留模式 – 除 Bank0 外,所有 RAM 库均已断电

▪ 部分模式 - 8 个 RAM 银行 (Bank8-15) 可以随时断电

配置取决于应用要求

• 高速运行时分区很重要

• TCM 可视为单周期 RAM

• TCM 内存仍可通过 DMA 访问

• 使用以下注意事项:

− 关键代码(向量表、ISR)和代码通常只有

核心访问的应该/可以放在 ITCM 区域

− 数据通常仅由核心(堆栈、堆……)访问

应该/可以放在 DTCM 区域

− 数据通常由多个总线主控器(核心、

DMA) 应放置在 OCRAM 中

− 不太重要的数据可以放在外部 SDRAM 中

ITCM、DTCM 和 OCRAM 的最佳大小需要是

在构建过程中确定和调整

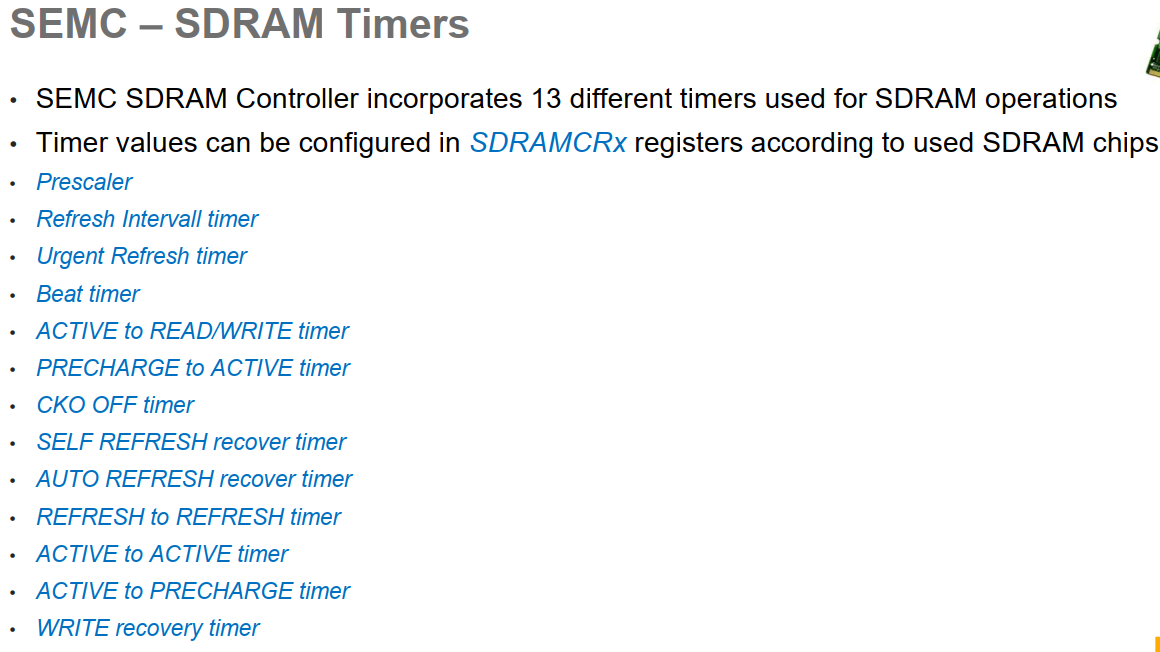

SEMC SDRAM 控制器包含 13 个用于 SDRAM 操作的不同定时器

• 定时器值可根据使用的 SDRAM 芯片在 SDRAMCRx 寄存器中配置

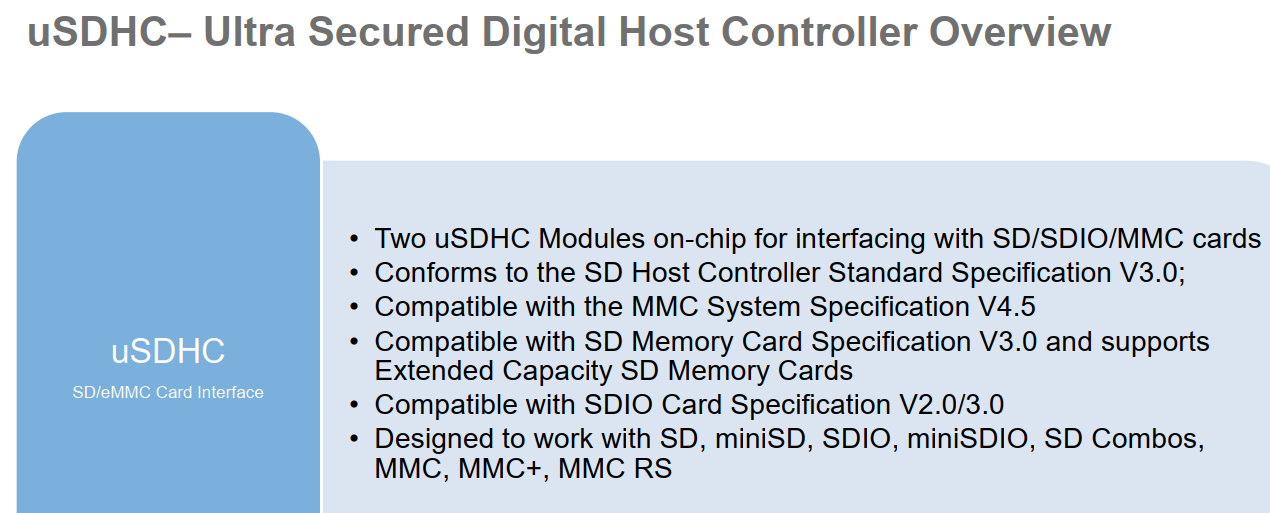

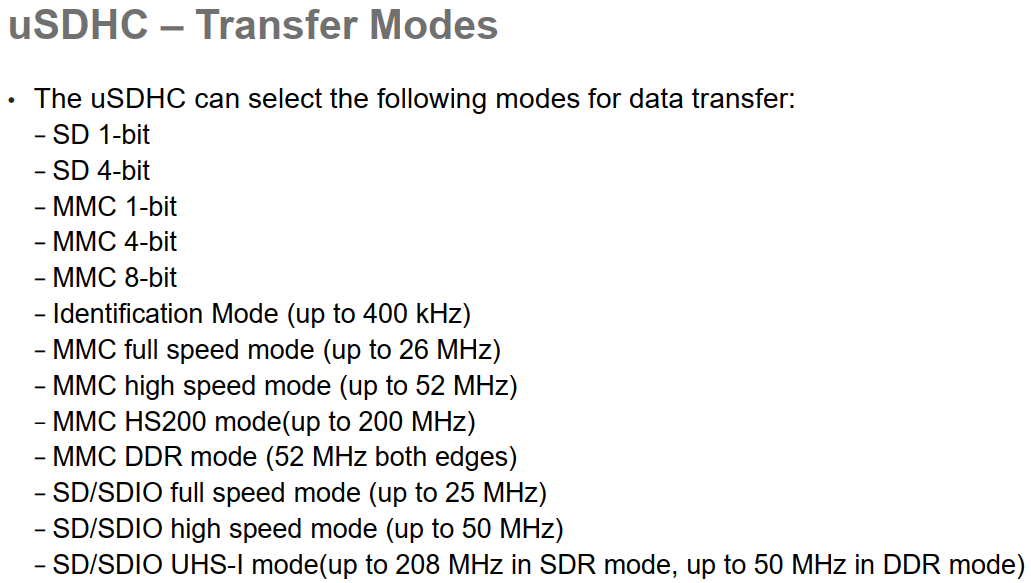

两个片上 uSDHC 模块,用于连接 SD/SDIO/MMC 卡

• 符合SD Host Controller Standard Specification V3.0;

• 与 MMC 系统规范 V4.5 兼容

• 兼容 SD 存储卡规范 V3.0 并支持

扩展容量 SD 存储卡

• 兼容 SDIO 卡规范 V2.0/3.0

• 设计用于 SD、miniSD、SDIO、miniSDIO、SD 组合、

MMC、MMC+、MMC RS

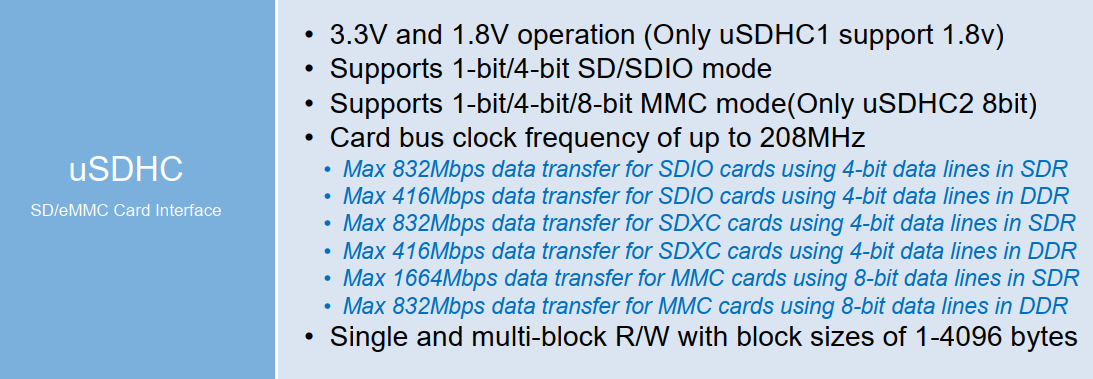

3.3V 和 1.8V 操作(只有 uSDHC1 支持 1.8v)

• 支持 1-bit/4-bit SD/SDIO 模式

• 支持1-bit/4-bit/8-bit MMC 模式(仅uSDHC2 8bit)

• 卡总线时钟频率高达 208MHz

• 使用 SDR 中 4 位数据线的 SDIO 卡的最大 832Mbps 数据传输

• 使用 DDR 中 4 位数据线的 SDIO 卡的最大 416Mbps 数据传输

• 在 SDR 中使用 4 位数据线的 SDXC 卡的最大数据传输率为 832Mbps

• 使用 DDR 中 4 位数据线的 SDXC 卡的最大 416Mbps 数据传输

• 在 SDR 中使用 8 位数据线的 MMC 卡的最大 1664Mbps 数据传输

• 使用 DDR 中的 8 位数据线的 MMC 卡的最大 832Mbps 数据传输

• 块大小为 1-4096 字节的单块和多块 R/W

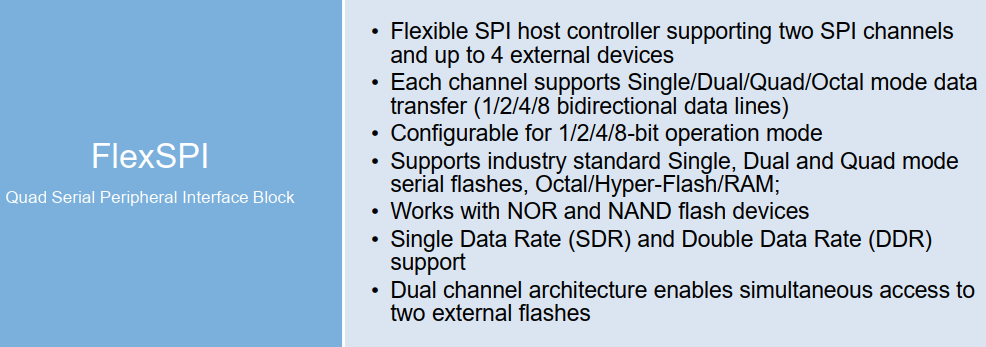

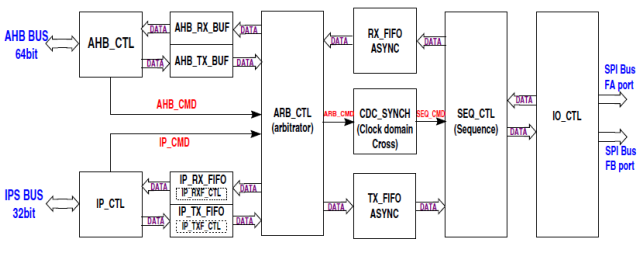

灵活的 SPI 主机控制器,支持两个 SPI 通道和多达 4 个外部设备

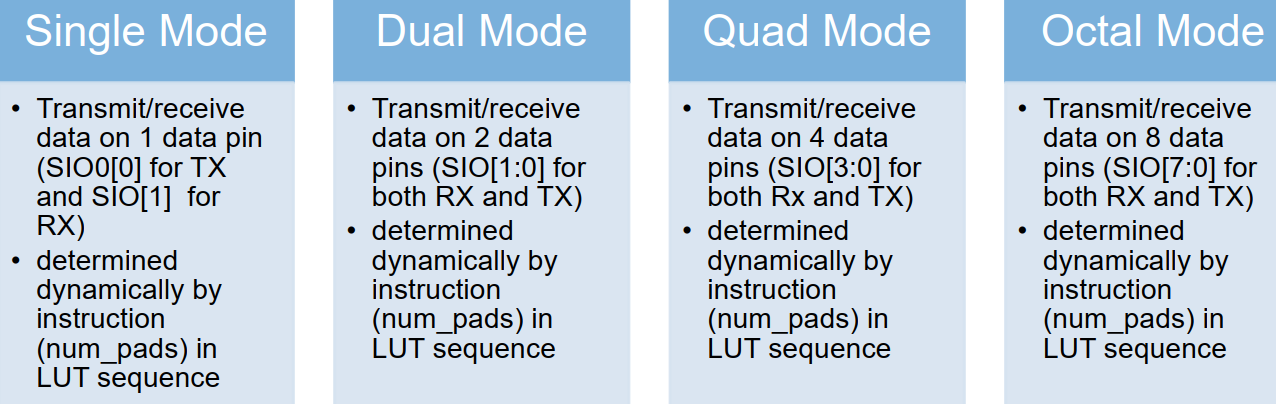

• 每个通道支持单/双/四/八模式数据传输(1/2/4/8 双向数据线)

• 可配置为 1/2/4/8 位操作模式

• 支持行业标准的单、双和四模式

串行闪存、八进制/Hyper-Flash/RAM;

• 适用于 NOR 和 NAND 闪存设备

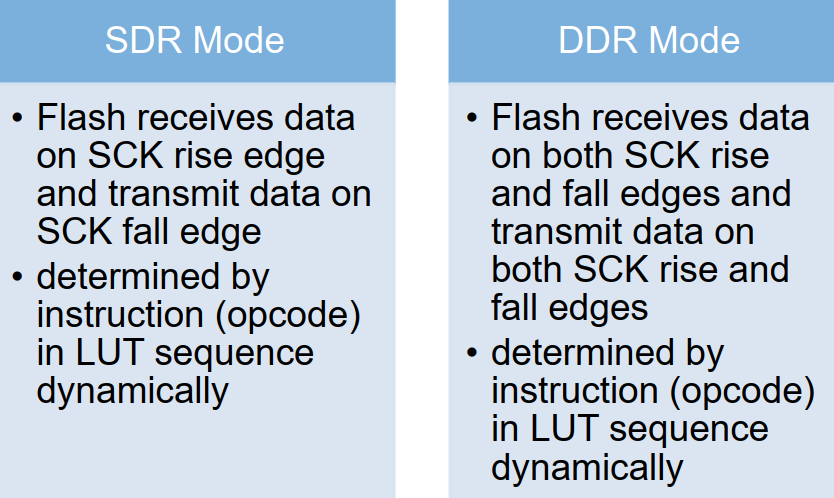

• 单数据速率 (SDR) 和双数据速率 (DDR) 支持

• 双通道架构可同时访问两个外部闪存

灵活的序列引擎(LUT 表)以支持各种供应商

▪ 串行 NOR 闪存

▪ 串行 NAND 闪存

▪ HyperBus 设备 (HyperFlash/HyperRAM)

▪ FBGA 器件

− 闪存访问模式

▪ 单/双/四/八模式

▪ 特别提款权/DDR

➢ SDR 模式下高达 133MHz,DDR 模式下高达 66MHz,内部 DQS 环回模式

➢ 在 SDR 和 DDR 模式下高达 166MHz,带 DQS 输入

▪ 单独/并行模式

− 支持采样时钟模式

▪ 内部虚拟读取选通在内部和从焊盘环回

▪ 从焊盘环回的 SCK 时钟输出

▪ Flash 提供读频闪

− 自动数据学习以选择正确的采样时钟相位

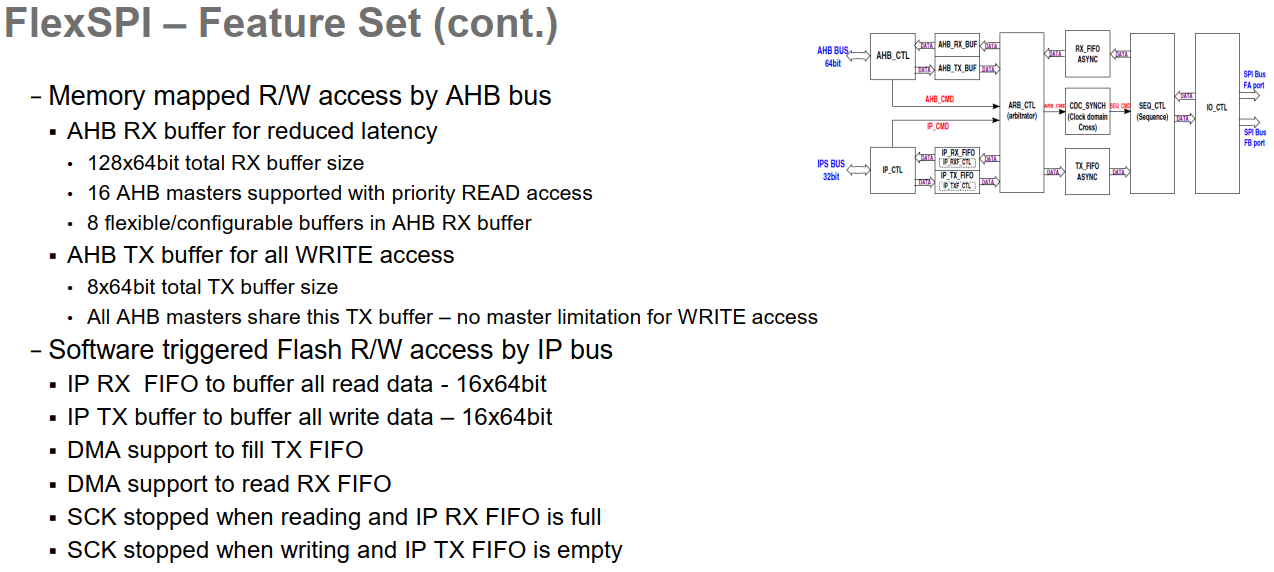

通过 AHB 总线进行内存映射 R/W 访问

▪ 用于减少延迟的 AHB RX 缓冲区

• 128x64bit 总 RX 缓冲区大小

• 支持 16 个 AHB 主机,具有优先读取访问权限

• AHB RX 缓冲器中有 8 个灵活/可配置的缓冲器

▪ 用于所有 WRITE 访问的 AHB TX 缓冲区

• 8x64 位总 TX 缓冲区大小

• 所有 AHB 主机共享此 TX 缓冲区——对 WRITE 访问没有主机限制

− 通过 IP 总线软件触发 Flash R/W 访问

▪ IP RX FIFO 缓冲所有读取数据 - 16x64bit

▪ IP TX 缓冲区用于缓冲所有写入数据 – 16x64 位

▪ DMA 支持填充 TX FIFO

▪ DMA 支持读取 RX FIFO

▪ SCK 在读取且 IP RX FIFO 已满时停止

▪ SCK 在写入且 IP TX FIFO 为空时停止

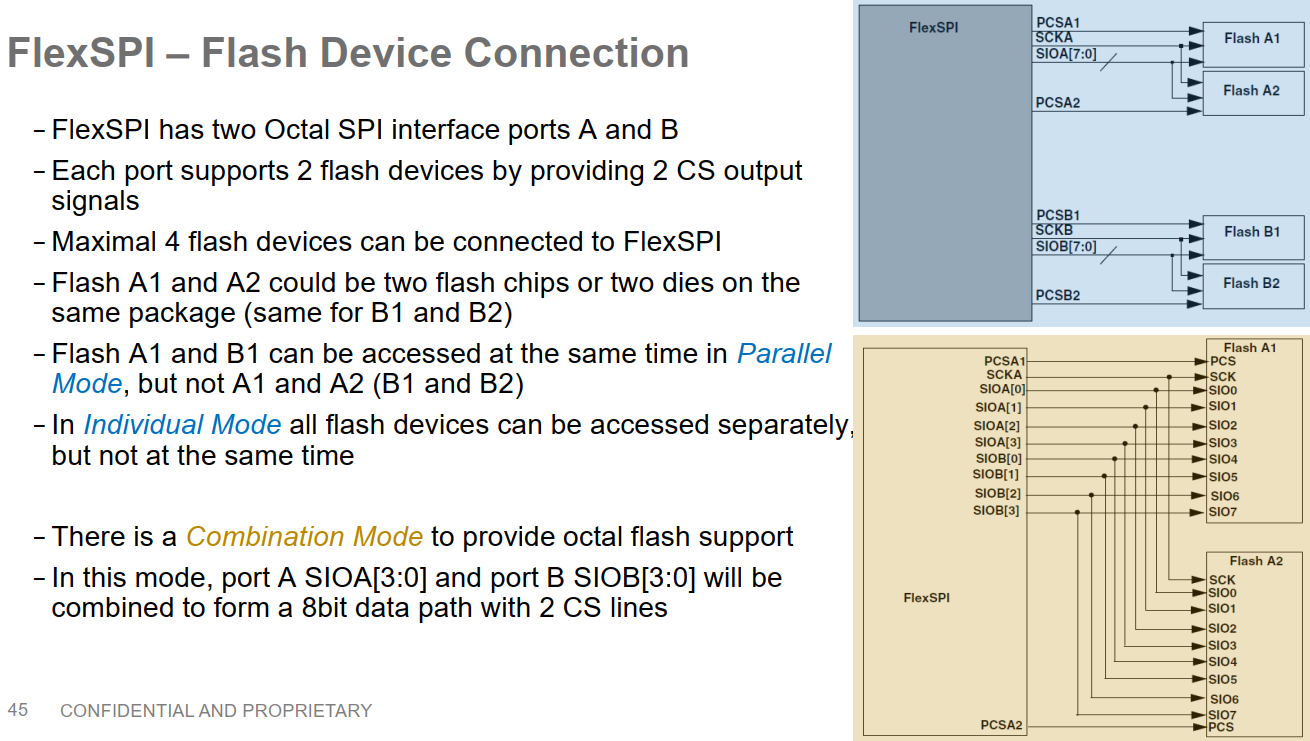

− FlexSPI 有两个 Octal SPI 接口端口 A 和 B

− 每个端口通过提供 2 个 CS 输出信号支持 2 个 flash 设备

− 最多可连接 4 个闪存设备到 FlexSPI

− Flash A1 和 A2 可以是两个闪存芯片或同一封装上的两个裸片(B1 和 B2 相同)

− Flash A1 和 B1 可以同时并行访问

模式,但不是 A1 和 A2(B1 和 B2)

− 在独立模式下,所有闪存设备都可以单独访问,但不能同时访问

− 有组合模式提供八进制闪存支持

− 在此模式下,端口 A SIOA[3:0] 和端口 B SIOB[3:0] 将组合形成具有 2 个 CS 线的 8 位数据路径

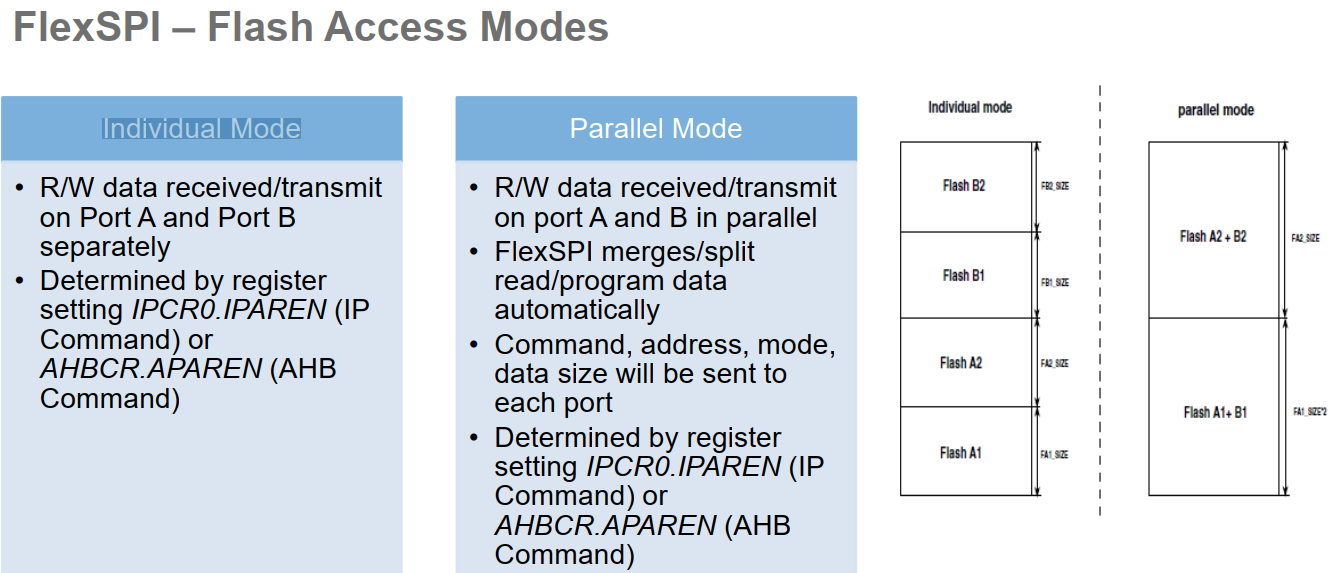

在端口 A 和 B 上并行接收/发送 R/W 数据

• FlexSPI 自动合并/拆分读取/编程数据

• 命令、地址、模式、数据大小将被发送到每个端口

• 由寄存器设置 IPCR0.IPAREN(IP 命令)或

AHBCR.APAREN(AHB 命令)

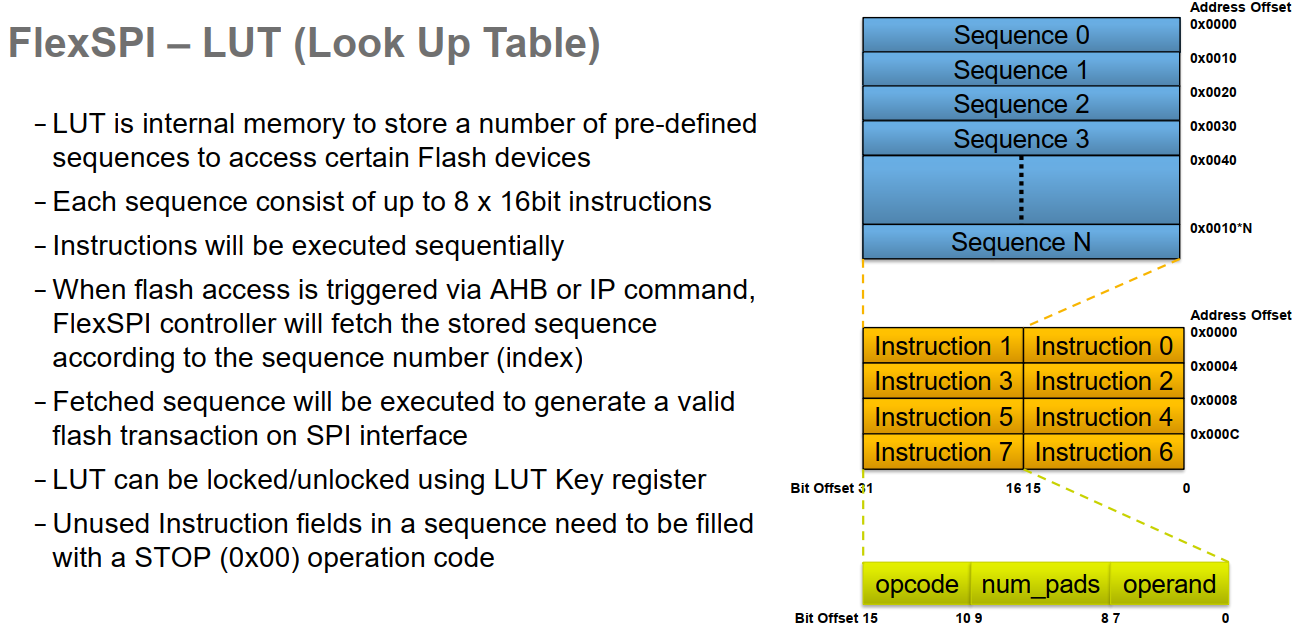

LUT 是用于存储许多预定义序列以访问某些 Flash 设备的内部存储器

− 每个序列最多包含 8 个 16 位指令

− 指令将按顺序执行

− 当通过 AHB 或 IP 命令触发 flash 访问时,FlexSPI 控制器将根据序列号(索引)获取存储的序列

− 将执行获取的序列以在 SPI 接口上生成有效的闪存事务

− LUT 可以使用 LUT Key 寄存器锁定/解锁

− 序列中未使用的指令字段需要填写

带有 STOP (0x00) 操作码 opcode num_pads 操作

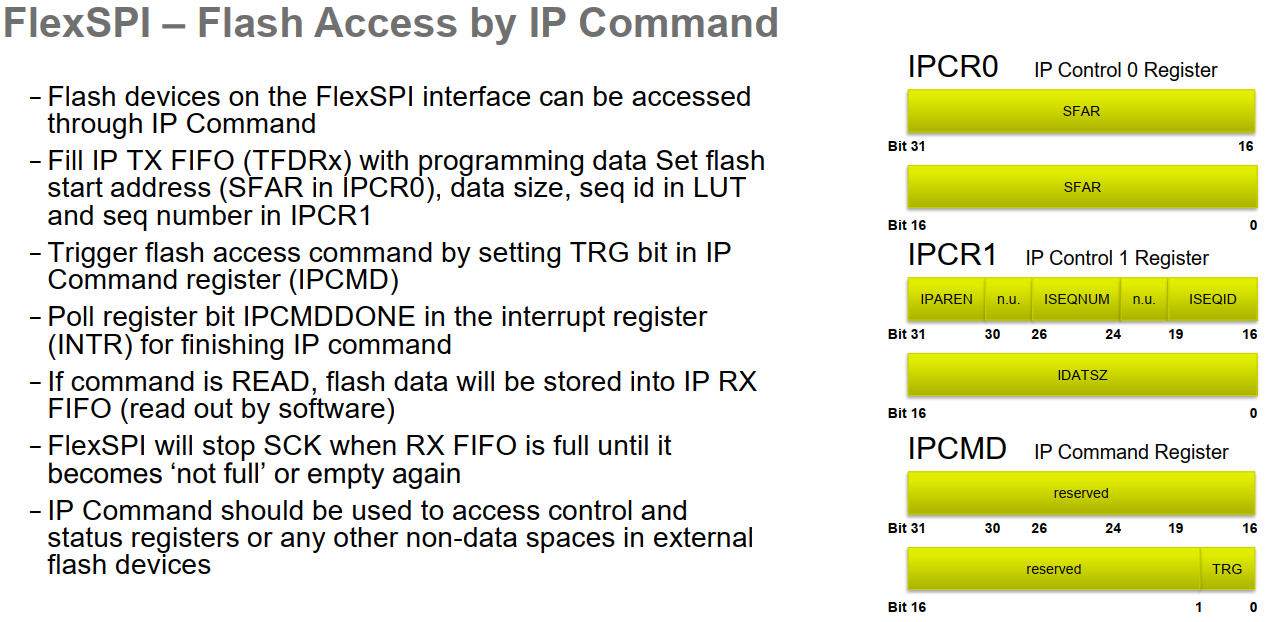

FlexSPI 接口上的 Flash 设备可以通过 IP 命令访问

用编程数据填充 IP TX FIFO (TFDRx) 设置闪存起始地址(IPCR0 中的 SFAR)、数据大小、LUT 中的 seq id 和 IPCR1 中的 seq 编号

通过设置 IP 命令寄存器 (IPCMD) 中的 TRG 位触发闪存访问命令

中断寄存器中的轮询寄存器位 IPCMDDONE

(INTR) 用于完成 IP 命令

如果命令为 READ,闪存数据将存储到 IP RX FIFO(由软件读取)

FlexSPI 将在 RX FIFO 已满时停止 SCK,直到

再次变为“未满”或为空

IP 命令应用于访问控制和状态寄存器或外部闪存设备中的任何其他非数据空间

FlexSPI 接口上的闪存设备可以通过 AHB 总线直接访问地址 0x60000000

− 地址空间直接映射到 FlexSPI 端口上的串行闪存

− 内存映射的 r/w 访问该空间将触发闪存访问

根据需要的命令序列

− 当 READ 访问时,FlexSPI 会从 flash 中取出数据到 AHB RX Buffer 并在 AHB 总线上返回数据

− WRITE 访问时,FlexSPI 将数据缓冲到 AHB TX Buffer 中,然后将所有数据传输到串行闪存设备

−AHB 总线访问通常用于数据 R/W 访问