Denali NAND FLASH控制器的验证

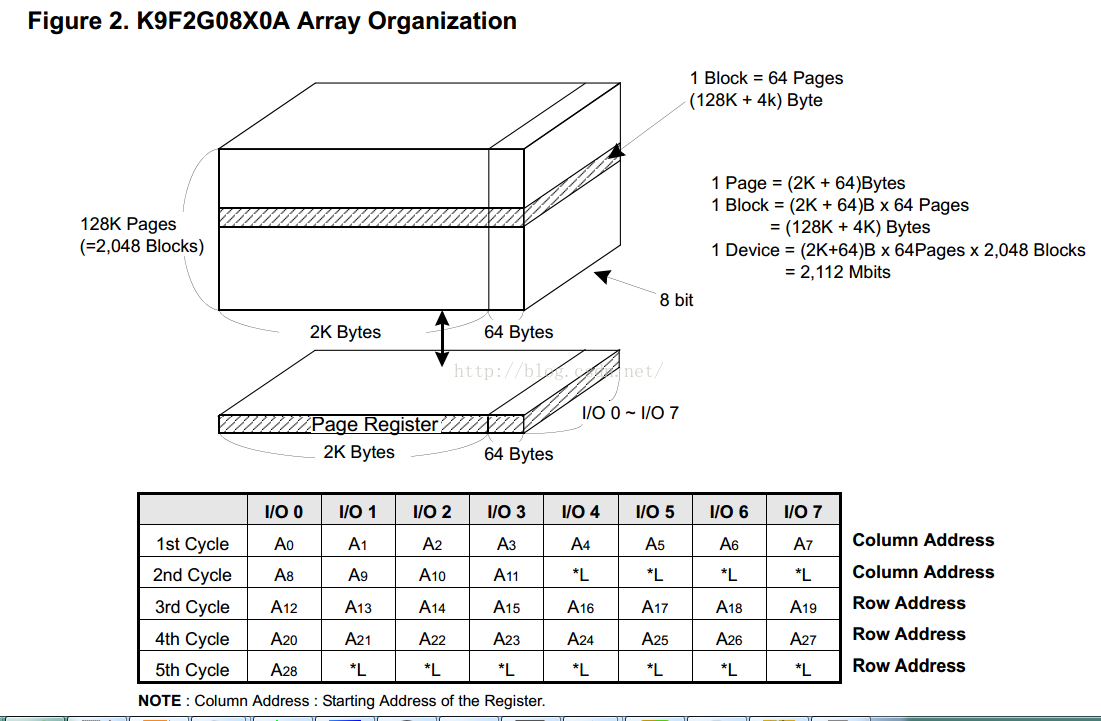

NAND FLASH的结构如图所示:

Denali NAND FLASH控制器模块提供了从AHB总线到外部NAND FLASH存储器芯片IO管脚的访问功能。主要技术特性包括:

1.标准32位AHB总线接口;

2.提供AHB交易缓存异步FIFO,实现速度匹配和数据通路调整,与AHB总线、与NAND FLASH存储器之间的数据通路均可配置(最大64bit);

3.提供数据缓存以提高访问性能;

4.支持内建的BOOT启动访问;

5. 提供4路bank片选信号,每路bank片选信号支持4片外部存储器件(?);

6.提供16bit位宽的内部控制寄存器,访问时序可配置;

7.提供控制通路,处理器可直接控制外部访问;同时也提供智能硬件抽象层,减轻处理器访问负担。

NAND FLASH控制器支持器件特性如下:

1.支持32页、64页及128页的块大小;

2.支持512B、2kB、4kB及8kB的页大小

3.支持多层器件;

4.支持SLC(Single Layer Cell,单层单元)和MLC(Multiple Layer Cell,多层单元),并具有可配置ECC纠检错功能。

控制器通过内置命令实现对存储器的操作,支持四种命令格式:MAP00/MAP01/MAP10/MAP11。

MAP00命令 一般不单独使用,对页缓冲区进行操作操作

MAP01命令 读、写存储器的一页(Nand Flash读写最小单位是页,擦除最小单位是块)

MAP10命令 包含六个子命令:擦除(块)、复制(页)、锁定(块)、页的读写修改(可修改单个字节)、传输模式配置(主区+备份区)、流水线

MAP11命令 每太看懂是干嘛的...

此外,还支持ECC校验功能。