NIOS II 之串口学习

UART中有6个寄存器分别为control, status, rxdata, txdata, divisor,endofpacket. 的寄存器是16位位宽的。

UART会产生一个高电平的中断,当接收到数据或者准备好发送下一个字符时

UART IP核使用逻辑0表示mark,逻辑1表示space.

1. even 每个字节传送整个过程中bit为1的个数是偶数个(校验位调整个数)

2. odd 每个字节穿送整个过程中bit为1的个数是奇数个(校验位调整个数)

3. noparity没有校验位

4. space 校验位总为0

5. mark 校验位总为1;

发送部分包括一个7,8,9位的txdata保持寄存器和一个相应的7,8或9位的移位寄存器。当移位操作没有进行时,移位寄存器自动加载保持寄存器数据。移位操作寄存器自动发送给TXD输出,LSB先。

主控可以通过status寄存器的,发送就绪(TRDY),移位寄存的空信号(tmt),发送溢出错误位(TOE),

接收部分包括一个接收移位寄存器和一个rxdata保持寄存器,当接收到一个字符之后,数据从移位寄存器自动加载到保持寄存器。主控可以检测status中的接收就绪(RRDY),接收溢出错误(ROE),break detect (BRK), parity error (PE), and framing error (FE) bit

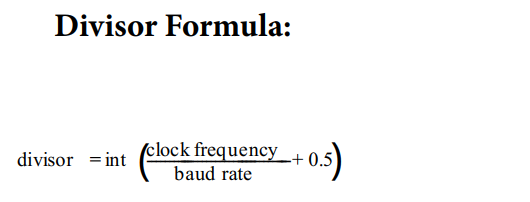

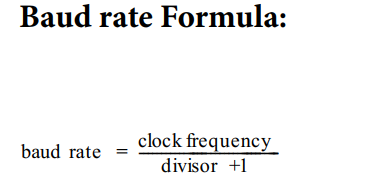

波特率

16位的divisor寄存器

rxdata register

当接收到一个完整的字符,数据会保存在rxdata寄存器,并把rrdy置位为1,当rxdata中的数据读走后rrdy为0,如果当数据还没读走时再次有数据传输到rxdata,roe会置位为1,向rxdata寄存器写入数据无效。

txdata寄存器

当数据写入txdata时,TRDY 为0时,当txdata寄存器中的数据传输到发送移位寄存器时,TRDY为1,如果当TRDY为0时向txdata寄存器写入数据,会造成结果不确定。