CDR锁定方式

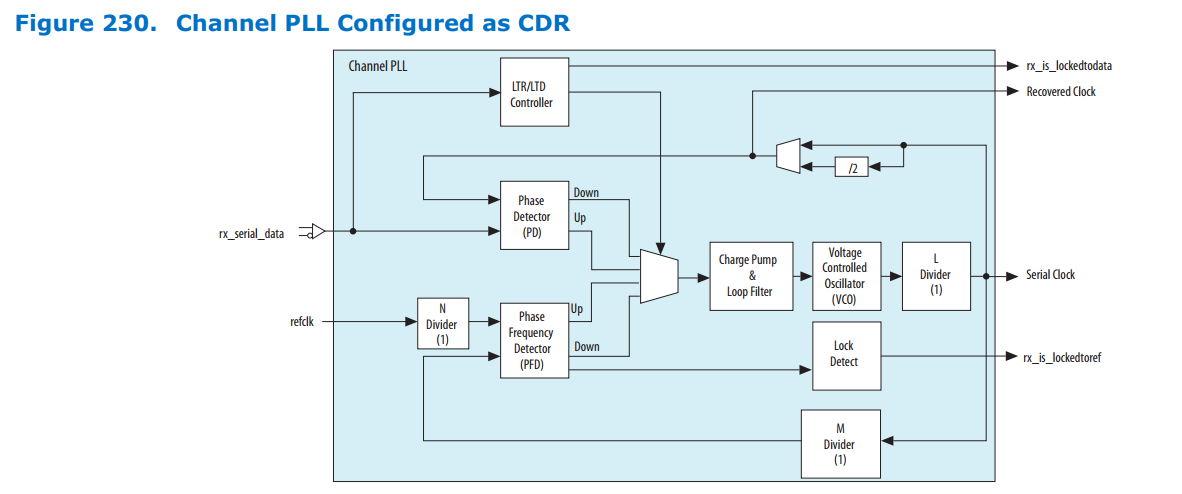

每个通道的PMA包括一个通道PLL可以配置成接收器CDR。还可以把通道1和4的PLL配置成CMU PLL用于发送器。

CDR有两种锁定方式

1、Lock-to-Reference Mode(LTR)

在LTR模式,PFD跟踪接收通道的参考时钟,PFD控制充电泵调谐CDR中VCO,

rx_is_lockedtoref状态信号拉高表示CDR锁定到了参考时钟上。

注意:在LTR模式下,PD处于失效状态。

2、Lock-to-Data Mode(LTD)

在正常模式,CDR必须在LTD模式,从串行数据中恢复时钟,在LTD模式中,PD跟踪串行数据。基于接收数据和CDR输出时钟之间的相位差,PD控制CDR调谐VCO的充电泵。

注意:在LTD模式中,PFD无效,rx_is_lockedtoref也无意义,可能会随意翻转。

锁定时间由决定于接收数据速率(文档为transition density)和该通道参考时钟与上游发送器参考时钟的ppm差。在CDR接收到有效的串行数据后,

rx_is_lockedtodata停止翻转;所以在rx_is_lockedtodata拉高并保持最小4us之后,才能释放rx_digitalreset信号。

两种锁定模式

Automatic Lock Mode

在自动锁定模式,CDR先锁定到参考时钟(LTR模式),当锁定到参考时钟之后,CDR再锁定到串行数据(LTD模式),但要满足下面的条件:

- 当使能了rx_std_signaldetect后,信号门限检测电路判断到接收器输入buffer的信号有效

- CDR输出时钟与输入参考时钟在配置的ppm频率范围内(频率锁定)

- CDR输出时钟和输入参考时钟在相位上匹配,大约在0.08UI(unit interval)内(相位锁定)

如果因为频率偏移或者信号衰减过大而造成CDR不能锁定到数据上,CDR会切换回LTR模式。

Manual Lock Mode

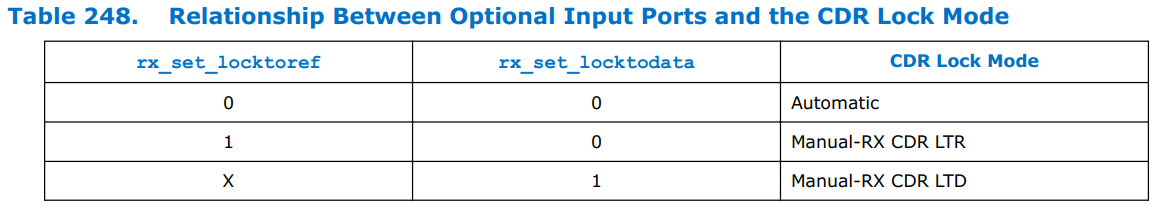

对于某些需要CDR快速锁定的应用来说,PPM检测器和相位关系检测器反应时间可能会时间过长。这时可以手动控制CDR来减少锁定时间,这需要用到两个端口:rx_set_locktoref和rx_set_locktodata

demo上实现过程是,当PHY不进行过采样时,使用Automatic,当PHY进行过采样时,使用Manual-RX CDR LTR。这是为什么呢?

过采样是对同一个数据采样5次,如果使用LTD,那得到的数据速率是不可能采样5倍的数据速率的,所以只能提高cdr_refclk时钟才能实现过采样,

而当数据速率大于1G时,使用Automatic自动去检测数据的锁定,是一种感觉更稳妥的方式。