VIP之Switch

| Switch II |

|

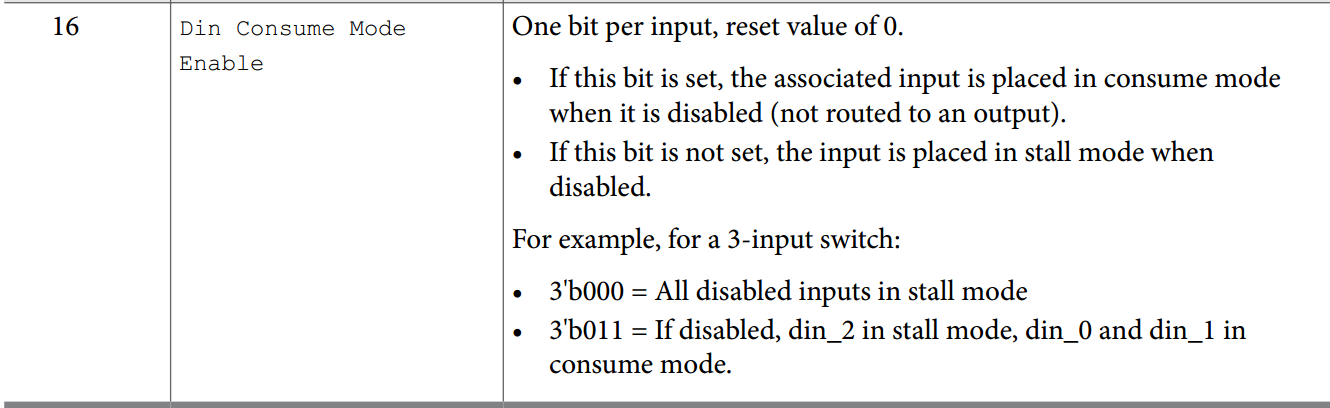

现在发现switch IP很难启动,可能在某个点上设置有问题,没有din_ready信号,经过测试发现控制寄存器中的地址16控制着din_ready信号,把相应的位设置为1之后,相应的din_ready信号就会拉高,这里以两输入为例,如果两个din_ready信号全拉高之后,很可能造成输出不确定,所以最好要输出那个通道就把相应的din_ready拉高。而且在设置好这些参考之前不要使能IP,使能IP要放在最后。

加载一组新的配置有如下两种方式可以选择:

1、向Go寄存器写入0,等待Status寄存器读到0,再向Go寄存器写入1;

2、向Output Switch寄存器写入1执行与1过程相同的操作,但不需要用户干预,这是一种厂家推荐的方式。

综上,感觉下面是操作的过程会比较靠谱:

IOWR(VIP_SW_5CH_BASE,16,0x001f);

IOWR(VIP_SW_5CH_BASE,4,layer[0]);

IOWR(VIP_SW_5CH_BASE,5,layer[1]);

IOWR(VIP_SW_5CH_BASE,6,layer[2]);

IOWR(VIP_SW_5CH_BASE,7,layer[3]);

IOWR(VIP_SW_5CH_BASE,8,layer[4]);

// IOWR(VIP_SW_5CH_BASE,3,1);

IOWR(VIP_SW_5CH_BASE,0,0);

IOWR(VIP_SW_5CH_BASE,0,1);

2018/4/16

今天调试发现:

1、在配置Nios程序时,SignalTap II一定要停止运行,否则程序不能配置进去(好像也不是这样的)。

2、今天把1个输入同时输出两个通道的功能打通了,其实这本应该是个很简单的问题,不知以前为什么,可能与发现1有关。

3、感觉Nios的系统时钟降低下可能会比较好。

问题:switch ii在Nios中配置不了

与别的VIP 一样添加到Qsys之后,经过综合编译之后,本来以为很快就可以出结果,但是Switch II这次怪的很,每当Nios II配置Switch II时就会卡死。

猜想1:因为一次添加了三个IP,除Switch之外,还有CVI和CSC,而CSC的类中定义了好几个数组,会不会是因为CSC占用的内存空间太大呢?

可以先做一个尝试,只在Nios中添加Switch,看能否运行过去。

猜想2:是不是因为Qsys互连中一个复位信号驱动多个IP造成IP始终处理复位状态呢?

可以通过SiganlTap II查看下

猜想3:由于Switch中的Avalon--mm Slave 口与别的IP略有区别,是不是Nios不能支持呢?

这个概率应该是很小的,也是最不想看到的结果。

结论:Switch是可以通过Nios驱动是没问题的。复位也是没有问题的,但是没有找到什么原因,只能把程序退回到以前的版本。