Arria10收发器校正

收发器的模拟和数字部分都需要校正来补偿过程,电压和温度(PTV)带来的变化。

Arria10使用PreSICE来执行校正过程。

校正主要包括上电校正和用户校正两方面:

- 上电校正在器件上电时自动执行,它在器件的配置期间执行。

- 用户校正在动态重配置时执行。用户需要使能需要地校正序列。

Arria10使用CLKUSR来进行收发器校正。

1、 仲裁

PreSICS Avalon-MM接口和用户Avalon-MM接口共用内部总线,可能通过仲裁获取内部总线控制权,实现对收发器通道和PLL的可编程寄存器及校正寄存器。

两种方式检测部线控制权归属:

- 使用reconfig_waitrequest

- 使用Capability寄存器

使用reconfig_waitrequest

Native PHY IP和PLL默认设置是使用reconfig_waitrequest.当PreSICE控制内部配置总线时,从内部配置总线输出 的reconfig_waitrequest输出为高,

当用户访问被授权后,从内部配置总线输出 的reconfig_waitrequest输出为低。

reconfig_waitrequest可以从Native PHY的不同位置产生,比如内部配置总线、Streamer等等。它们绑定在一起变成一个reconfig_waitrequest。

其中reconfig_address决定那个reconfig_waitrequest输出到重配置接口。如果在校正期间设置reconfig_address为streamer偏移地址,

Reconfig_waitrequest在校正完成之前可能是低电平,在校正期间要保证reconfig_address保持静止。

|

校正过程

|

校正完成

|

|

|

内部配置总线输出

|

1

|

0

|

|

streamer

|

可能会拉低

|

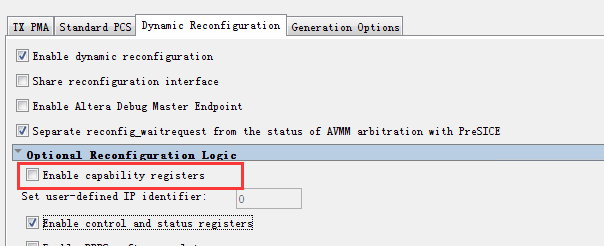

使用Capability寄存器

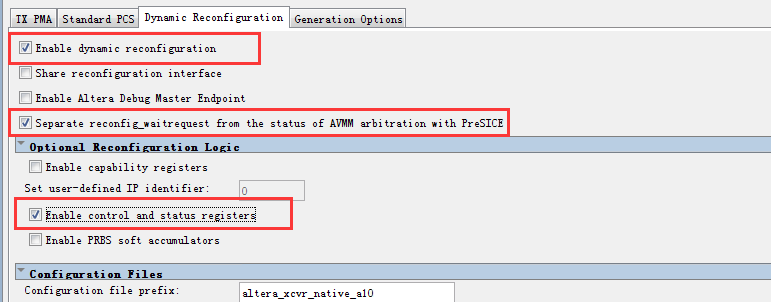

使能Capability操作如下

这样可以通读取Capability寄存器0x281[2]来检测通道访问控制权,通过Capability寄存器0x280[2]来检测PLL的访问控制权。并且reconfig_waitrequest将不会在PreSICE控制内部总线时拉高。

1)内部控制总线到PreSICE:

如果0x100有校正位使能,向偏移地址0x0[7:0]写入0x1;

如果0x100没有校正位使能,向偏移地址0x0[7:0]写入0x3;

2)仲裁内部总线到用户:

向0x0写入0x2,PreSICE会停止校正把控制权交给用户,此时reconfig_waitrequest虽然拉低,但没有校正完成。

检测校正是否完成

- 监控pll_cal_busy,tx_cal_busy和rx_cal_busy信号

- 从Capability寄存器读取*_cal_busy信号状态

在校正过程*_cal_busy信号保持高电平。

配置Capability寄存器0x281[5:4]来单独使能或者禁止tx_cal_busy或者rx_cal_busy

校正寄存器

- Avalon-MM 接口仲裁寄存器:用于内部总线访问请求

- 校正使能寄存器:PMA与PLL校正使能寄存器映射地址为0x100。校正完成后校正使能寄存器自动清除。

- Capablity寄存器

- 速率切换标志寄存器:只用于CDR

(1)Avalon-MM接口仲裁寄存器(0x0)

|

Bit

|

Offset address

|

|

|

[0]

|

0x0

|

控制avalon-mm接口。

0:用户请求控制内部总线

1:归还PreSICE内部总线控制权

|

|

[1]

|

0x0

|

用于指示是否校正完成。这是cal_busy取反的信号。该位可以进行写操作,但是如果没有在0x100中写入任何使能校正位,而在该位写入了0x0,PreSICE可能会把该位拉高,但cal_busy保持拉高。如果

cal_busy连接到复位控制器通道复位会被触发。

读操作:

0x1 = 校正完成

0x0 = 校正没有完成

写操作:

0x1 :不触发校正,不触发校正分两种情况,一早当用户控制总线时

PreSICE是不能触发校正的,所以用户仲裁一般向地址0x0写入0x02,

二是当没有在0x100使能任何校正位时,也不需要触发校正,此时把

仲裁交换PreSICE时向地址0x00写入0x03。

|

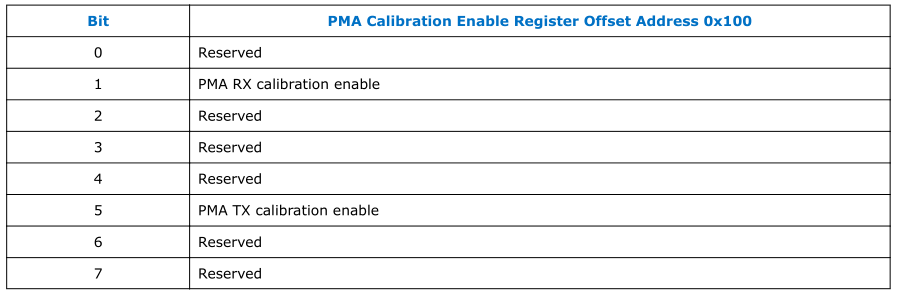

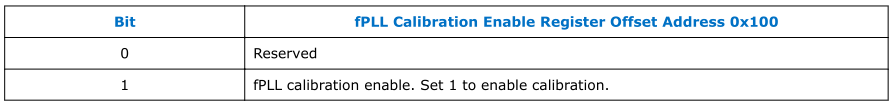

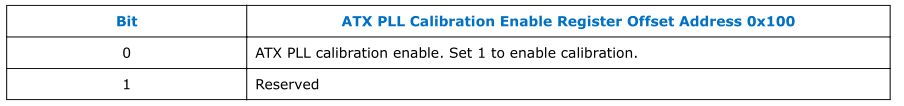

(2)校正使能寄存器(0x100)

用户校正PMA和PLL的校正使能寄存器,映射偏移地址为0x100,所有校正使能寄存器在校正处理完成后自动清除。当校正期间reconfig_waitrequest为高电平时,禁止对校正使能寄存器进行读写操作。

按读—调整—写过程使能校正寄存器。下面是使能ATXPLL的操作步骤:

1) 读偏移地址0x100

2) 设置LSB[0]位为1,保持MSB[7:1]值不改变

3) 把修改后的值写入偏移地址0x100

收发器通道PAM校正寄存器

fPLL校正寄存器

ATX PLL校正寄存器

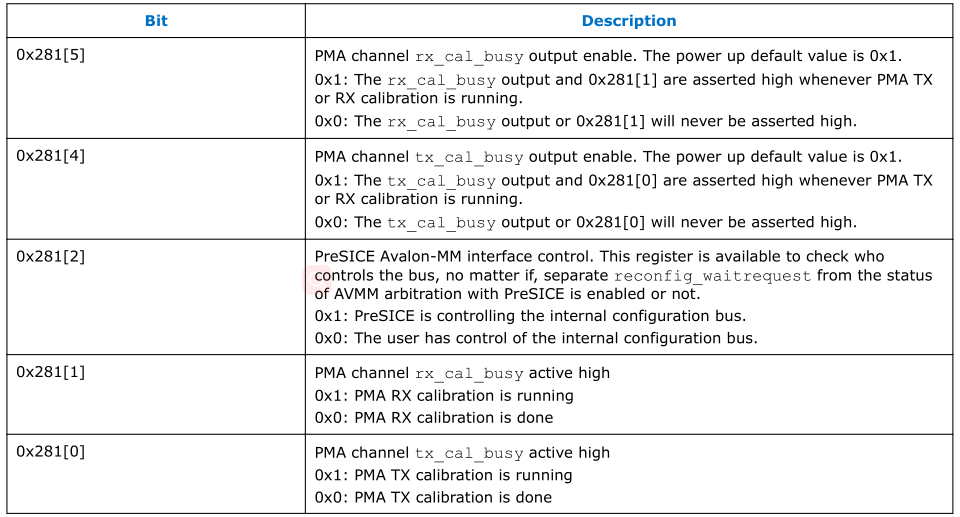

(3)Capability寄存器(0x281)

允许通过Avalon-MM配置接口读取校正状态。该寄存器是FPGA逻辑中的软逻辑。读功能寄存器不需要总线仲裁,在校正期间也可以读取。要使用功能寄存器必须在生成IP中勾选Enable Capability Registers。

tx_cal_busy,rx_cal_busy,ATX PLL pll_cal_busy,和fPLL pll_cal_busy信号由该寄存器控制。Capability寄存器0x281[5:4]使能或者禁止rx_cal_busy或tx_cal_busy,

tx_cal_busy和rx_cal_busy信号是由同一部分硬件产生,在校正期间会同时改变状态,这样的话读校正可能会被写校正影响,而写校正也会被读校正影响。功能寄存器0x281[5:4]正是为了解决这个问题而定义的。如果在发送校正期间,设置0x281[5]为0x0,则rx_cal_busy的值不会改变,如果在接收校正期间,设置0x281[4]为0x0,则tx_cal_busy的值不会改变。如果涉及到单工的TX和RX合并,这个功能是不能使用的。

PMA校正功能寄存器

|

Bit

|

|

|

0x281[5]

|

PMA通道中rx_cal_busy输出使能。上电默认为高电平

如果设置为1,在PMA TX和RX校正期间rx_cal_busy输出和0x281[1]都会置高

如果设置为0,rx_cal_busy和0x281[1]永远不会被置高

|

|

0x281[4]

|

PMA通道中tx_cal_busy输出使能。上电默认为高电平

如果设置为1,在PMA TX和RX校正期间tx_cal_busy输出和0x281[0]都会置高

如果设置为0,tx_cal_busy和0x281[0]永远不会被置高

|

|

0x281[1]

|

1:PMA RX正在进行校正

0:PMA RX校正完成

|

|

0x281[0]

|

1:PMA TX正在进行校正

0:PMA TX校正完成

|

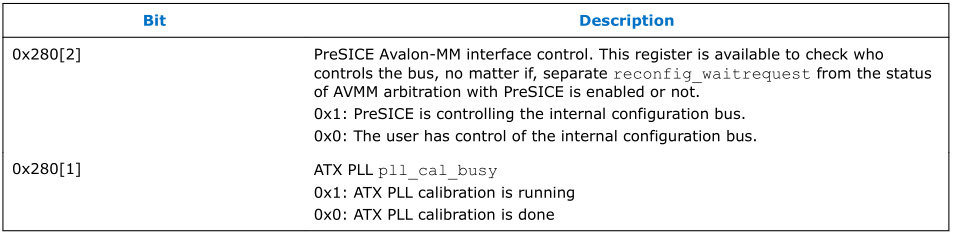

ATX PLL功能校正寄存器

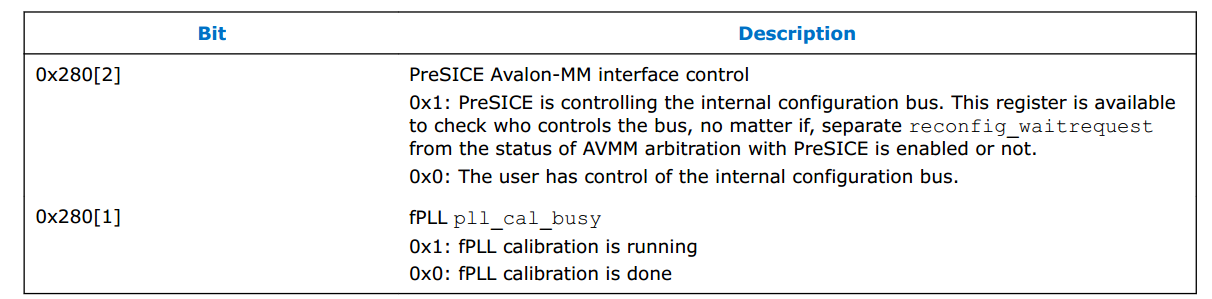

fPLL Capability寄存器用于校正状态

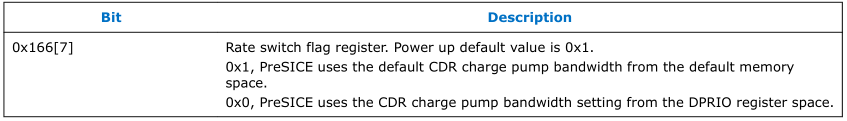

(4)速率转换标志寄存器(0x166)

速率转换标志用于CDR电荷泵校准.每个SOF有一个CDR默认的电荷泵设置。上电后,这些设置被装载在PreSICE的存储空间。如果要改变线速率,就要通过Avalon-MM来设置,该值存放在Avalon-MM重配寄存器空间。在RX PMA(包括CDR)校正,PreSICE需要知道那个CDR电荷泵校准值会被使用。如果设置0x166[7] = 0x1,PreSICE认为存放在它空间的值依然有效,如果设置0x166[7] = 0x0,PreSICE使用Avalon-MM配置寄存器的值。校正完成后,自动设置0x166[7] = 0x1。速率转换标志只用在速率转换时。

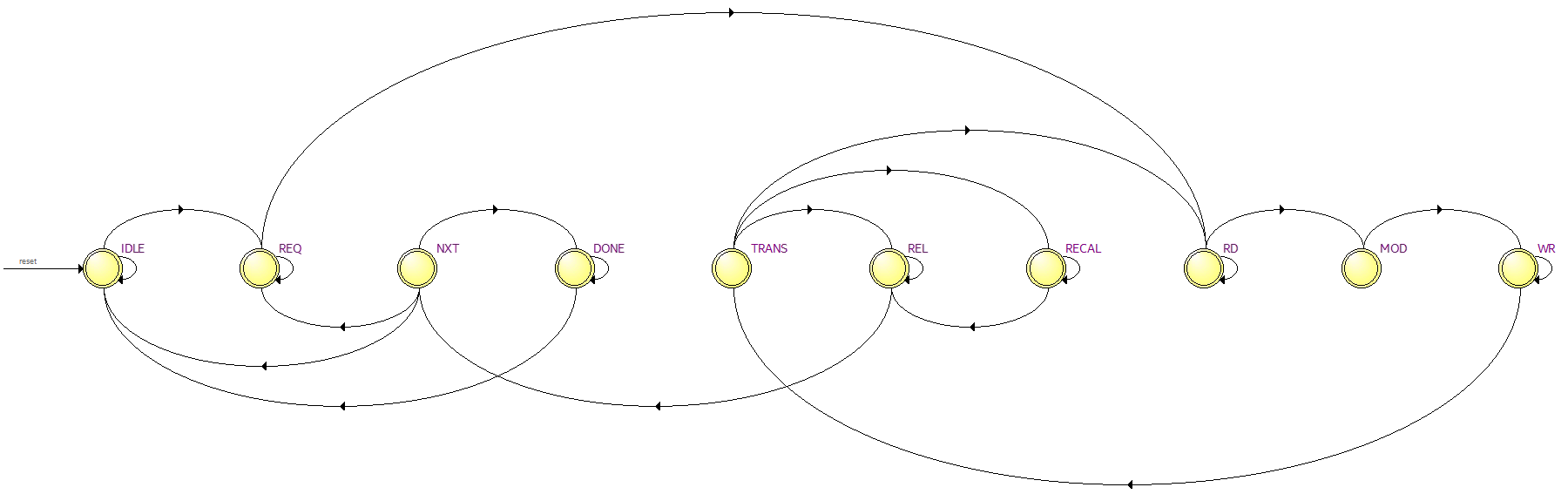

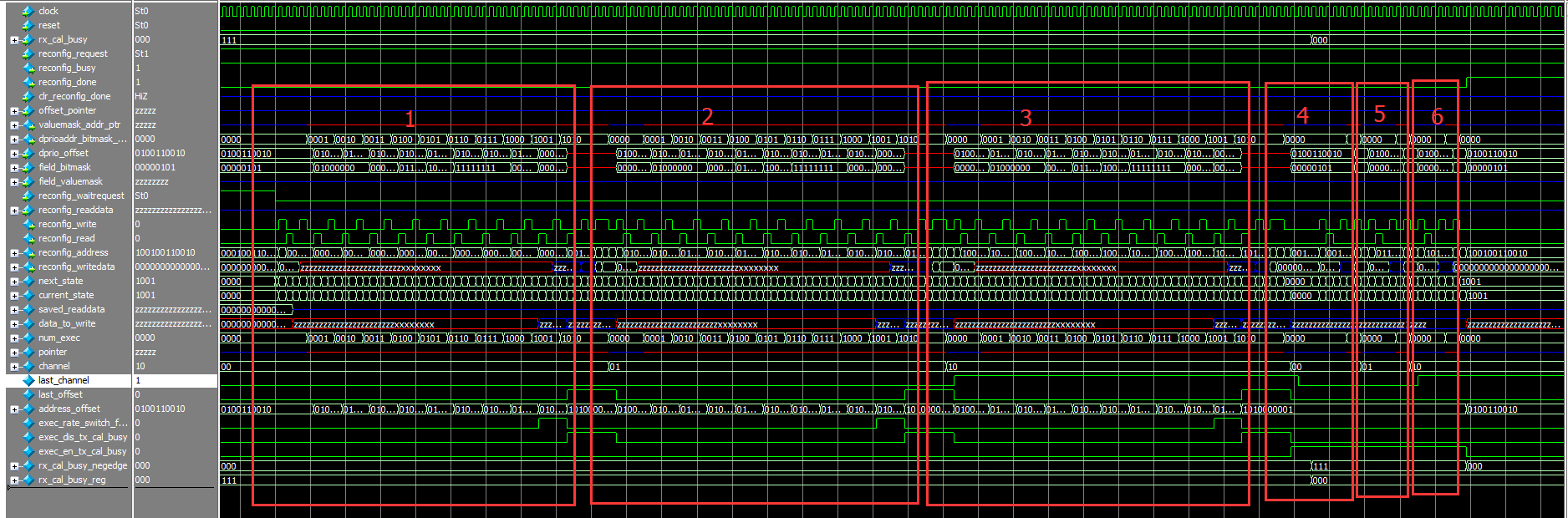

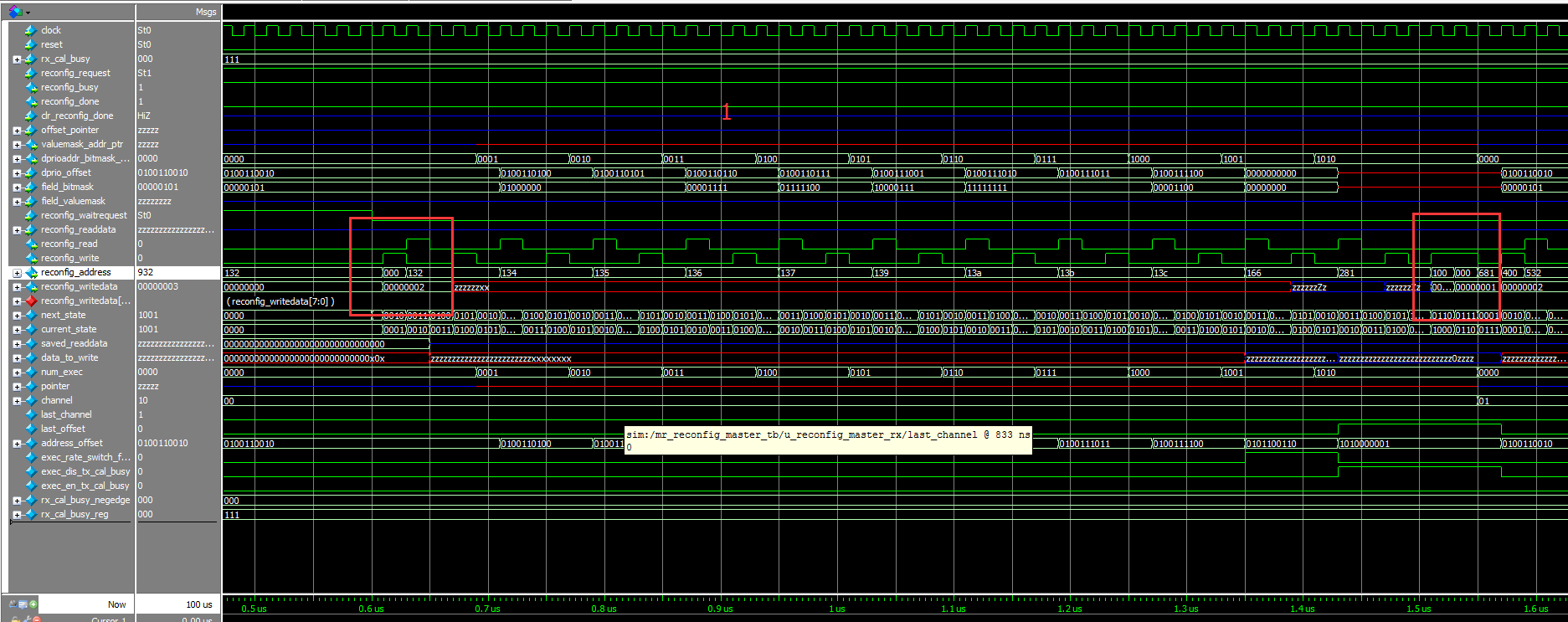

2、 校正步骤

2)用户校正

如果对PLL或者收发器通道进行了重配—--尤其速度改变后,必须对收发器进行校正。Arria10有一个专用的校正引擎PreSICE(hardened Precision Signal Integrity Calibration Engine),用于校正收发器模拟部分,从而保证接收器和发送器处于最佳性能。CLKUSR时钟脚用于驱动校正引擎。

在校正之后,必须要对收发器进行复位操作。推荐使用PHY复位控制器,它有推荐的复位时序。当校正完成后复位是自动进行的。

用户校正步骤:

1、 向偏移地址0x0[7:0]中写入0x2,向内部配置总线请求用户访问校准寄存器。

2、 等待reconfig_waitrequest拉低。或者等待Capability寄存器的PreSICE Avalon-MM接口控制=0,对于PMA是地址0x281[2],对于ATX PLL和fPLL地址是0x280[2]。

3、 通过读—调整—写方式向偏移地址0x100写入请求校正的位。fPLL写入0x02,ATX_PLL写入0x01,如果要使能PMA通道校正,必须设置0x100[6]位为0

4、 为PMA校正设置速率转换标志寄存器,如果校正ATX PLL和fPLL则跳过该步骤

读—调整—写 0x1 到偏移地址0x166[7] 如果没有CDR速率转换。

读—调整—写 0x0 到偏移地址0x166[7] 如果有不同CDR带宽设置的转换速率。

5、为PAM校正向功能寄存器0x281(capability registers)写入适当的值,用于使能或者禁止tx_cal_busy或者rx_cal_busy输出。如果校正ATX PLL和fPLL则跳过该步骤

读—调整—写 0x1到0x281[5],使能rx_cal_busy

读—调整—写 0x0到0x281[5],禁止rx_cal_busy

读—调整—写 0x1到0x281[4],使能tx_cal_busy

读—调整—写 0x0到0x281[4],禁止tx_cal_busy

6、向偏移地址0x0[7:0]中写入0x1,释放内部配置总线给PreSICE来执行校正。直到cal_busy拉低表示校正完成

7、定期检测cal_busy或者读取地址0x281(对于GXB是0x281,而AXT PLL和fPLL都是0x280)(capability registers)来查看cal_busy的状态,直到校正完成。

|

Source

|

Destination

|

Condition

|

|

IDLE

|

IDLE

|

(1)reconfig_waitrequest == 1,校正未完成

(2)发出校正请求,但

|

|

IDLE

|

REQ

|

(1)发出校正请求,但

|

|

REQ

|

REQ

|

虽然发出用户总线控制请求,但是

reconfig_waitrequest为高电平

|

|

REQ

|

RD

|

reconfig_waitrequest为低电平

|

|

RD

|

RD

|

reconfig_waitrequest为高电平

|

|

RD

|

MOD

|

reconfig_waitrequest为低电平

|

|

MOD

|

WR

|

|

|

WR

|

WR

|

reconfig_waitrequest = 1

|

|

WR

|

TRANS

|

reconfig_waitrequest = 0

|

|

TRANS

|

REL

|

如果三个通道都设置完成就释放控制权限给PreSICE

|

|

TRANS

|

RECAL

|

当设置一个通道之后,但还没有完成3个通道的设置

|

|

TRANS

|

RD

|

继续执行一次读——调整——写操作

|

|

REL

|

REL

|

|

|

REL

|

NXT

|

|

state

|

||

|

NXT

|

转向下一个通道

|

|

|

TRANS

|

执行一次读——调整——写操作,能进入TRANS的状态只有WR

|

|

|

REL

|

能进入NXT状态的唯一状态。实

现总线控制权的释放

|

|

|

RECAL

|

控制地址100,使能PMA RX校正‘

该状态之后的一个状态一定是REL

该状态的前一状态一定是TRANS,转换的条件是last_offset

|

|

|

DONE

|

该状态也只在三个通道都完成之后才执行一次

|

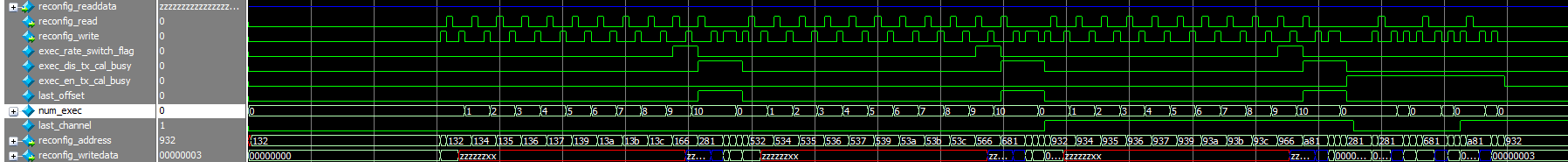

000 132 134 135 136 137 139 13a 13b 13c 166 281 100 000

002 002 001

400 532 534 535 536 537 539 53a 53b 53c 566 681 500 400

002 002 001

800 932 934 935 936 937 939 93a 93b 93c 966 a81 900 800

002 002 001

000 281 000

002 003

400 681 400

002 003

800 a81 800

002 003

总共循环两,每次都是三个通道。