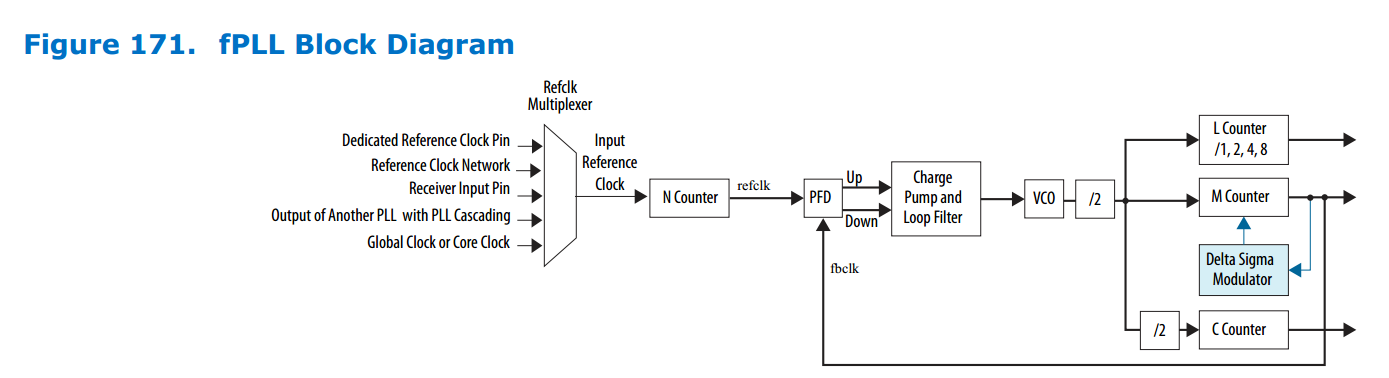

fPLL结构及动态配置

输入参考时钟

从上图可以看到参考时钟输入的几种类型。

注意:fPLL的校正是由CLKUSR来驱动的,这个时钟必须要保持稳定。

参考时钟利用器

N计数器

N计数器会把参考时钟利用器输出进行分频。N计数器帮助降低环路带宽、减少PFD内部频率操作范围。N计数器支

持的分频因子从1到32

相频检测器(PFD)

N计数块输出的refclk和M计数器输出fbclk同时作为PFD的输入。当参考时钟的下降沿早于反馈时钟的下降沿时,

PFD生成一个“UP”信号,相反的,如果反馈时钟的下降沿早于参考时钟的下降沿,PFD生成一个“Down"信号

充电泵和环路滤波器(CP + LF)

PFD的输出用于充电泵和环路滤波器生成VCO的控制电压,充电泵把”up/down“信号转换脉冲转换成电流脉冲,再

经过环路低通滤波器后成为VCO的控制电压。

压控制振荡器

VCO把输入电压转换成可调节的时钟频率。

VCO freq = 2*M*Input reference clock/N.

后缩放计数器,L

L 计数器把VCO输出的时钟分频,当fPLL作为一个发送器的PLL时,L计数器驱动CGB并通过x1时钟线来驱动TX PMA。

M计数器

对VCO输出时钟分频,M计数器可以选择任何VCO相位。M计数据 和N计数器输出频率相同。M计数器在整数模式的范

围从8到128,而在小数模式的范围是11到123。

Delta-Sigma Modulator(Delta-Sigma 调制器)

delta-sigma modulator (DSM)与 M 乘法计数器一起用于使 PLL 运行在小数分频模式。DSM 从周期

到周期动态地修改 M 计数器因子。不同的 M 计数器因子允许"average" M 计数器因子是一个非整

形。4-20 时钟倍频与分频

C计数器

FPLL C计数器分频因子从1到512.

小数分频模式(Fractional Mode)

在小数分频模式下,M 计数器值等于 M 反馈因子与小数分频值的和。小数分频值等于 K/2^32, 其中K 是 0 到(2^32–1)之间的整数。

整数模式(Integer Mode)

对于运行在整数模式的 PLL,M 是一个整数值,DSM 是禁用的。

I/O PLL 只能运行在整数模式。

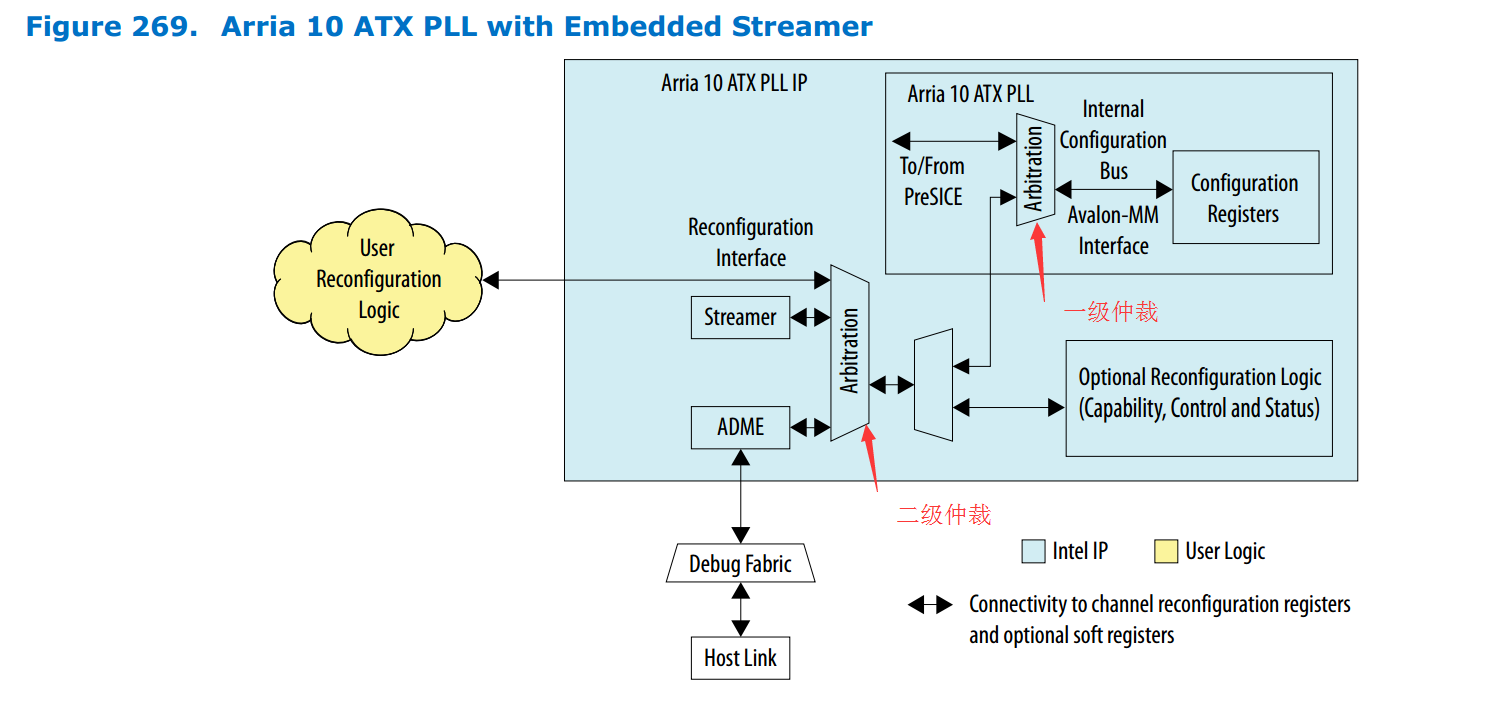

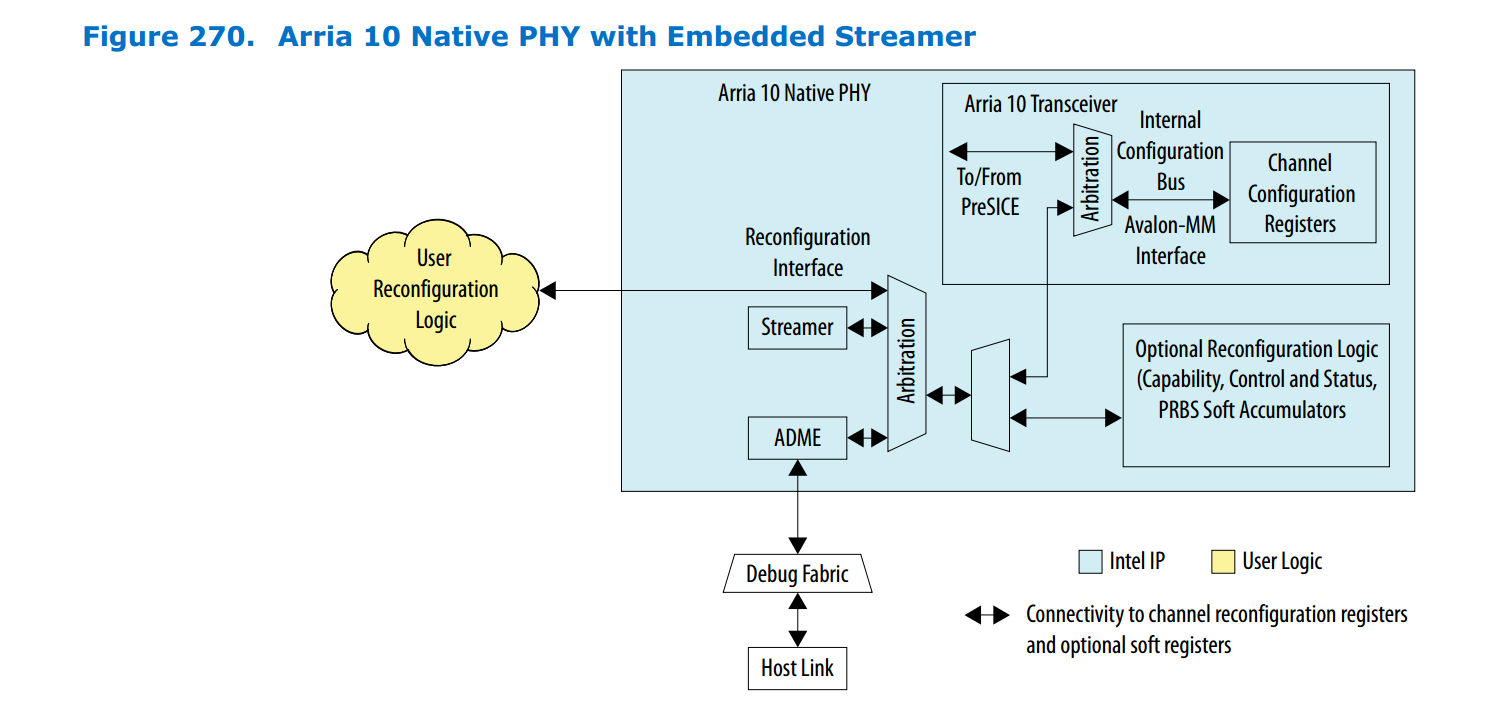

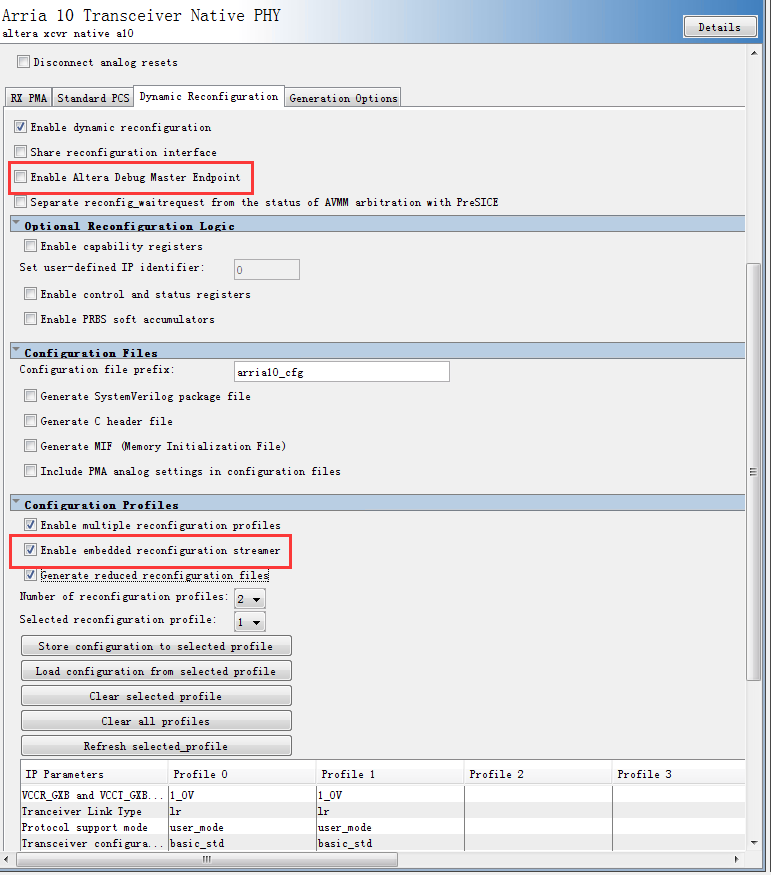

二、动态重配

可选择重配置逻辑(Optional Reconfiguration Logic)

使能选项:

• Capability registers

• Control and status registers

• PRBS soft accumulators (Native PHY IP core only)

两级仲裁

1、重配置接口与PreSICE校正引擎仲裁

2、Native PHY/PLL IP的主avalon-mm接口之间的仲裁

- 内嵌重配置器(Embedded reconfiguration streamer)(只能用于Native PHY和ATX PLL,说明应该不可以用于fPLL)

- ADME

- 用户配置逻辑

它们三个就是所说的特征块(feature blocks)

当PreSICE没有控制内部总线时,三个特征块才可以使能来访问内部配置总线。三个特征块同时访问时,是有优先级的,

其中内嵌重配置器优先级最高,用户配置逻辑次之。当优先级低的正在访问过程,优先级高的只能等到优先级低的访问完

成后才能访问。要注意的是:如果使能ADME,要连接一个avalon-mm主到配置接口,或者连接reconfig_clock,reconfig_reset信

号并把reconfig_write,reconfig_read,reconfig_address和reconfig_writedata信号接地。如果配置接口没有正确连接,ADME就不

会有时钟和复位,ADME也可能工作失常。

动态重配中建议

- Tx PLL重配建议

在以下两种情况时,使用软寄存器控制fPLL的pll_powerdown

- 把fPLL的模式从integer修改为fractional

- 把fPLL的模式从fractional修改为integer

当涉及数据速率和协议模式重配时,建议在PLL重配和校正过程中,PLL和发送器通道同时处于复位状态。可以通过tx_digitalreset, rx_digitalreset,

tx_analogreset, 和rx_analogreset或者通道软寄存器进行复位。如果需要重配ATX PLL,使用TX PLL切换模式或者使用本地时钟分频来实现速率调整而避免校正ATX PLL。

- 通道建议

- 当进行涉及数据速率和协议模式重配时,在配置过程中,可以通过tx_digitalreset, rx_digitalreset, tx_analogreset, 和rx_analogreset或者通道软寄存器进行复位。

- 当进行不涉及数据速率和协议模式重配时,建议在配置过程只对数字部分进行复位。