HDMI ip中的时钟 vid_clk与ls_clk

|

文件模块

|

mr_rate_detect

|

|

|

refclock

|

被测时钟

|

|

|

measure_clk

|

参考时钟,为固定100M

|

|

|

reset

|

复位,高电平有效

|

|

|

refclock_measure

|

在一定时间内被测时钟的计数值

|

|

|

valid

|

计数完成时的效指示信号

|

tmds_clk时钟既与色彩深度有关,也与数据速率有关。

tmds时钟速率(tmds clock rate)时钟通道在HDMI电缆上振荡的速率。当字符速率小于等于340Mcsc时,TMDS时钟速率与字符速率相等。

当字符速率大于340Mcsc时,tmds时钟速率是字符速率的1/4。

字符速率(TMDS character Rate):HDMI传输线上每个数据通道上10位字符传输的速率,字符速率的表述单位为Mega-characters/second/channel(Mcsc),

当编码方式为4:2:0时24的YCbCr时,字符速率等于0.5倍的像素时钟速率;

当编码方式为4:2:0时30的YCbCr时,字符速率等于0.625倍的像素时钟速率;

当编码方式为4:2:0时36的YCbCr时,字符速率等于0.75倍的像素时钟速率;

当编码方式为4:2:0时48的YCbCr,4:2:2YCbCr或者RGB4:4:4 24位时,字符速率等于1倍的像素时钟速率;

当编码方式为4:4:4时30的RGB时,字符速率等于1.25倍的像素时钟速率;

当编码方式为4:4:4时36的RGB时,字符速率等于1.5倍的像素时钟速率;

当编码方式为4:4:4时48的RGB时,字符速率等于2倍的像素时钟速率;

像素时钟速率(Pixel Clock Rate)视频时钟中的像素传输脉冲。当像素复制有效时也包括复制像素(比如,480p的单像素复制会产生一个54M的像素时钟)

当TMDS_Bit_clock_Ratio为1时,说明接收到的HDMI字符速率在大于340 Mcsc,这时实际的TMDS_CLK时钟是字符速率的四分之一,所以程序提供的计算

字符速率的方法是:

assign measure_for_compare = TMDS_Bit_clock_Ratio? {measure[21:0], 2'b00} : measure;当TMDS_Bit_clock_Ratio为1时说明,字符速率

大于340Mcsc,字符速率= TMDS_CLK*4。

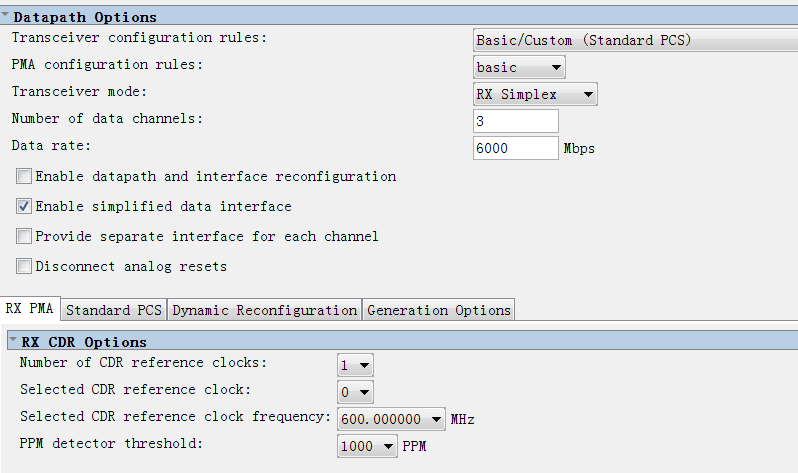

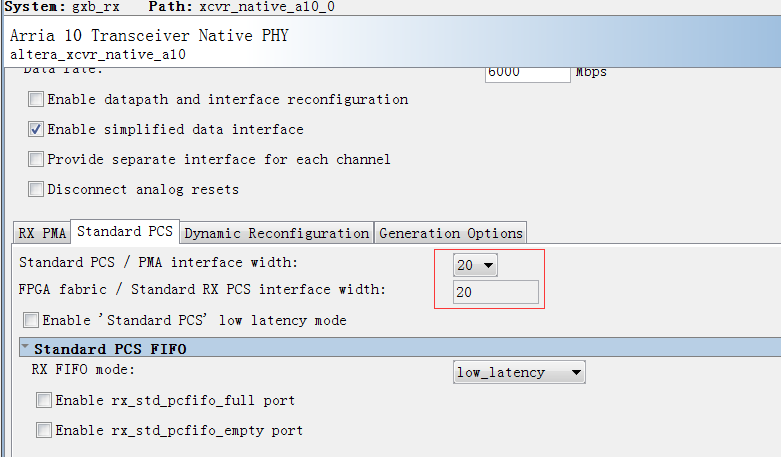

2、cdr_clk时钟的确定

cdr_clk时钟频率做为PMA部分中CDR的参考时钟,该时钟的大小与线速率有关的,如下图中的设置部分,设置Date Rate =6000Mbps,

cdr参考时钟频率为600M,而PAM与PCS之间的接口位宽为20。查看CDR的内部结构可以知道,CDR其实也是一个PLL,输出为高速串行时钟,该

高速串行时钟频率就是6000M,也就是说cdr对时钟进行了10倍频。当然如果cdr参考时钟为300M也是可以的,这样CDR就是进行20倍倍频,所以

CDR的参考时钟与ls_clk的时钟不是很明显,但是PCS部分接口位宽与线速率的倍数关系,刚好是串行时钟与ls_clk之间的关系。也就是说,

6000M/20=300M就是ls_clk的频率。但也有例外就是因为GXB只能接收1Gbps以前的数据速率,当数据速率低于1Gbps时要对数据进行过采样,

过采则要由CDR参考时钟及PLL配置来决定,举例说明:如果速率为500Mbps,参考时钟为500M,要满足不小于1Gbps的要求,则要把PLL倍频到1G

以前这里以1.5G为例,也就是PLL要三倍频,这样采到的串行数据是1.5Gbps,串转并以后,1.5G/20 = 75M,这个时钟就rx_clk的时钟,但不是

ls_clk的时钟,因为ls_clk对应的是实际的链路时钟,实际的链路上是500Mbps/20= 25M,也就是串转并之后再进行去过采样的结果。

4、ls_clk与vid_clk时钟的确定

|

DIM

|

TMDS_Bit_clock_Ratio

|

TMDS_CLK

|

CDR_CLK

|

LS_CLK

(2symbol)

|

VID_CLK

(2symbol)

|

|

8bpc

4k60fps

|

1

|

148.5

|

594

|

297

|

297

|

|

12bpc

4K30FPS

|

1

|

111.375

|

445.5

|

222.75

|

148.5

|

|

8bpc

4K30FPS

4K25fps

4k24fps

4k23fps

4k29fps

|

0

|

297

|

297

|

148.5

|

148.5

|

|

12bpc

1080p60fps

|

0

|

222.75

|

222.75

|

111.375

|

74.25

|

|

8bpc

1080P60fps,

1080p50fps

|

0

|

148.5

|

148.5

|

74.25

|

74.25

|

|

12bpc

1080p30fps

1080p24fps

1080p25fps

720p60fps

720p50fps

|

0

|

111.375

|

111.375

|

55.6875

|

37.125

|

|

8bpc

1080p30fps

1080p24fps

1080p25fps

720p60fps

720p50fps

|

0

|

74.25

|

371.25

(像素复制5倍)

74.25*5

|

37.125

|

37.125

|

|

8bpc

720p30fps

|

0

|

37.125

|

185.625

|

18.625

|

18.625

|

|

12bpc

720p30fps

|

0

|

55.6875

|

278.4375

|

27.9375

|

18.625

|

|

8bpc

720x576,50fps

720x480,60fps

|

0

|

27

|

135

|

13.5

|

13.5

|

|

12bpc

720x480,60fps

|

0

|

40.5(27*1.5)

|

202.7276(40.5*5)

|

10.125

|

13.5

|