8位同步码修改变4位同步码

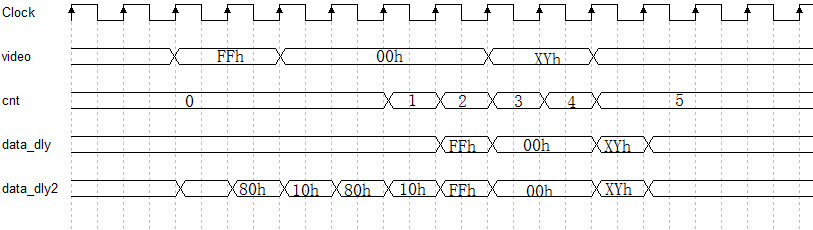

GV7704的1080p30及以下的分辨率同下码是这样的,每个同步码占用两个像素,而我们想要实现的是只占用一个像素。

实现方案:

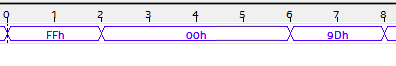

检测到FF后可以计数,如data_dly 问题是怎样清除video数据中的FFh.

第二种方案是,用一个长度为8的reg [7:0] data_dly2 [7:0]当检测到FFFF00000000XYXY时,就对这8个寄存器赋值成我们想要的数据。

module sync8_2_sync4(

input clk,

input [7:0] idata,

output [7:0] odata,

output h_out,

output v_out,

output sync_code

);

reg [7:0] din_buf [10:0] ;

reg [7:0] d_word_align = 0;

reg [1:0] v_h_buf =0;

reg [7:0] h_buf =0;

reg v_out_r=0;

reg h_out_r=0;

reg [3:0] cnt = 0;

reg sync_r = 1'b0;

always @( posedge clk )

begin

if( d_word_align[7:0] == 8'h7f || d_word_align == 8'hff) begin

din_buf[0] <= 8'h10;

din_buf[1] <= 8'h80;

din_buf[2] <= 8'h10;

din_buf[3] <= 8'h80;

din_buf[4] <= idata;

din_buf[5] <= 8'h00;

din_buf[6] <= 8'h00;

din_buf[7] <= 8'hff;

din_buf[8] <= din_buf[7];

end else if( &d_word_align[5:0] ) begin

din_buf[0] <= idata;

din_buf[1] <= 8'h00;

din_buf[2] <= 8'h00;

din_buf[3] <= 8'hff;

din_buf[4] <= 8'h10;

din_buf[5] <= 8'h80;

din_buf[6] <= 8'h10;

din_buf[7] <= 8'h80;

din_buf[8] <= din_buf[7];

end else begin

din_buf[0] <= idata;

din_buf[1] <= din_buf[0];

din_buf[2] <= din_buf[1];

din_buf[3] <= din_buf[2];

din_buf[4] <= din_buf[3];

din_buf[5] <= din_buf[4];

din_buf[6] <= din_buf[5];

din_buf[7] <= din_buf[6];

din_buf[8] <= din_buf[7];

end

end

always @( posedge clk )

begin

if( din_buf[5] == 8'hff )d_word_align[0] <= 1'b1;

else d_word_align[0] <= 1'b0;

end

always @( posedge clk )

begin

if( din_buf[4] == 8'hff )d_word_align[1] <= 1'b1;

else d_word_align[1] <= 1'b0;

end

always @( posedge clk )

begin

if( din_buf[3] == 8'h00 )d_word_align[2] <= 1'b1;

else d_word_align[2] <= 1'b0;

end

always @( posedge clk )

begin

if( din_buf[2] == 8'h00 )d_word_align[3] <= 1'b1;

else d_word_align[3] <= 1'b0;

end

always @( posedge clk )

begin

if( din_buf[1] == 8'h00 )d_word_align[4] <= 1'b1;

else d_word_align[4] <= 1'b0;

end

always @( posedge clk )

begin

if( din_buf[0] == 8'h00 )d_word_align[5] <= 1'b1;

else d_word_align[5] <= 1'b0;

end

always @( posedge clk )

begin

case(idata )

8'h80 :d_word_align[7:6] <= 2'b00;

8'h9d :d_word_align[7:6] <= 2'b01;

8'hab :d_word_align[7:6] <= 2'b10;

8'hb6 :d_word_align[7:6] <= 2'b11;

default :d_word_align[7:6] <= d_word_align[7:6];

endcase

end

always @( posedge clk )

begin

case(d_word_align[7:0])

8'h3f :v_h_buf <= 2'b00;

8'h7f :v_h_buf <= 2'b01 ;

8'hbf :v_h_buf <= 2'b10 ;

8'hff :v_h_buf <= 2'b11 ;

default :;

endcase

end

always @( posedge clk )

begin

case( cnt )

4'd0: if( (d_word_align[7:0] == 8'h3f) || (d_word_align[7:0] == 8'h7f) || (d_word_align[7:0] == 8'hbf) || (d_word_align[7:0] == 8'hff) )

cnt <= 1;

else cnt <= 0;

4'd1,4'd2,4'd3,4'd4: begin

cnt <= cnt + 1'b1;

if( v_h_buf[0] )

sync_r <= 1'b1;

else

sync_r <= 1'b0;

end

4'd5,4'd6,4'd7,4'd8: begin

cnt <= cnt + 1'b1;

if( v_h_buf[0] )

sync_r <= 1'b0;

else

sync_r <= 1'b1;

end

4'd9: begin

cnt <= 0;

sync_r <= 1'b0;

end

default:;

endcase

end

always @( posedge clk )

begin

h_buf[7:0] <= {h_buf[6:0],v_h_buf[0]};

end

always @( posedge clk )

begin

v_out_r <= v_h_buf[1];

h_out_r <= ~v_h_buf[0] ? h_buf[7] :v_h_buf[0];

end

assign odata = din_buf[8];

assign v_out = v_out_r;

assign h_out = h_out_r;

assign sync_code = sync_r;

endmodule