usb_ctrl

IFCLK应该是clkout,与数据同步

flagd就是就是slcs

FPGA的系统时钟用FX2LP的clkout时钟,个人觉得关键点在时钟是48M,别的异步时钟也是可以的。

模式配置

使用的模式是从设备FIFO。

从设备FIFO下的寄存器配置

FPGA代码架构

FPGA 代码的主要功能是监控从设备 FIFO 的满标志和空标

志,然后分别对 FIFO 进行读和写操作。

来自 FPGA 的接口时钟(IFCLK)需要转动 180 度,以满

足 FX2LP 的从设备 FIFO 接口建立时间的要求。

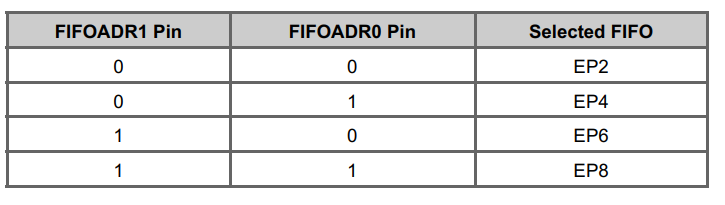

FIFOADR:地址控制端,选择CY7C68013A内部的四个FIFO。其中FIFOADR=2’b00时,对应端点2,即内部FIFO对应的地址。FIFOADR=2’b01,对应端点4,FIFOADR=2’b10对应端点6,FIFOADR=2’b11对应端口8。

PINFLAGSAB =0xe8; // FLAGA - fixed EP2EF(empty flag), FLAGB -fixed EP6FF(full flag)

SYNCDELAY; //FLAGA引脚,EP2空时为0,非空为1,FLAGB引脚,EP6满为0,非满为1。信号有效电平通过FIFOPINPOLAR寄存器设置,0为低有效,1为高有效,默认都为低有效。

PINFLAGSCD =0xac; // FLAGC - fixed EP2FF, FLAGD - fixed EP6EF

SYNCDELAY; //FLAGC引脚,EP2满时为0,非空为1,FLAGD引脚,EP6空为0,非满为1

EP2EF :endpoint empty flag

EP6FF : endpoint full flag

EZ-USB量子FIFO特点:当FIFO的空标志从1(空)到0(非空)时,FIFO的数据不是增加一个字节,而是一个USB数据包。

(1)FIFO设置

FIFO设置的过程包括节点,方向和缓存大小等

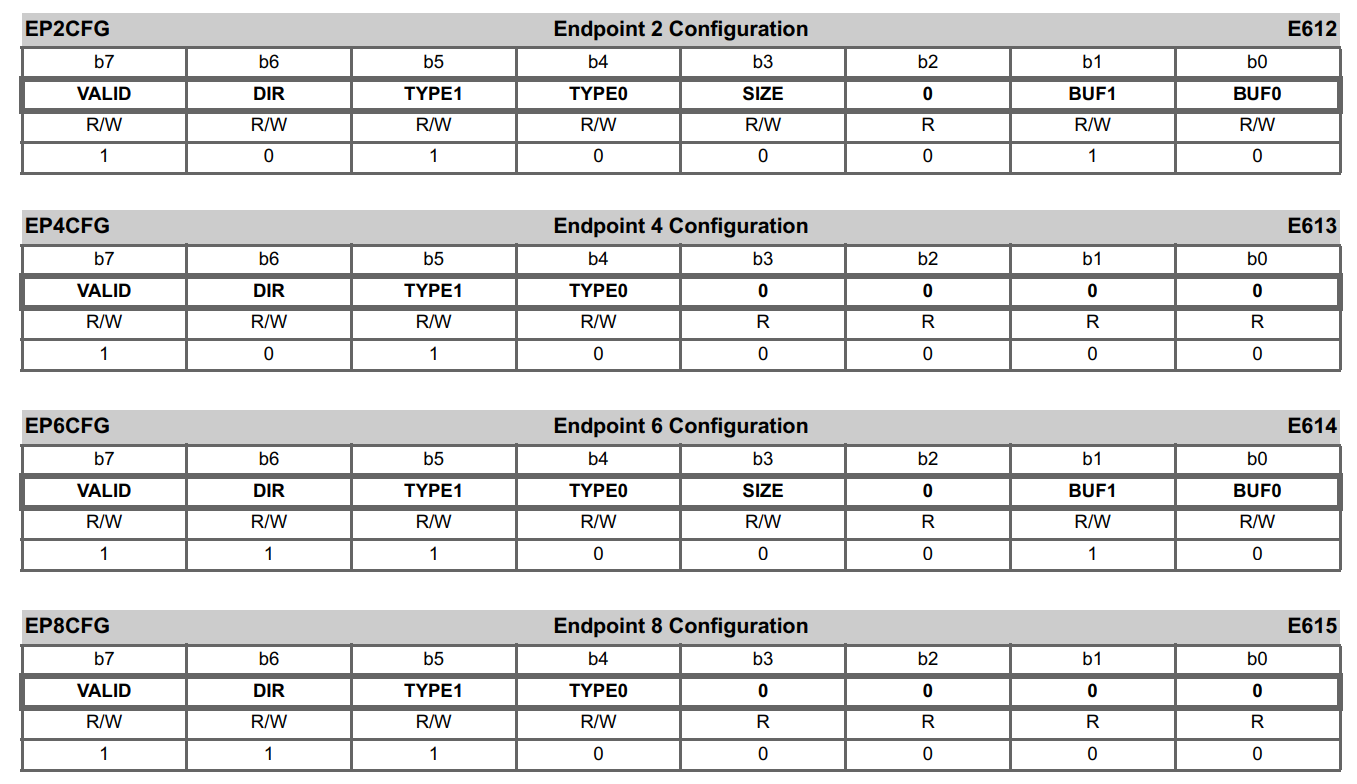

The bits in the EPxCFG registers control the following:

■ Valid. Set to ‘1’ (default) to enable the endpoint. A nonvalid endpoint does not respond to host IN or OUT packets.

■ Type. Two bits, TYPE1:0 (bits 5 and 4) set the endpoint

type.

❐ 00 = invalid

❐ 01 = ISOCHRONOUS (EP2,4,6,8 only)

❐ 10 = BULK (default)

❐ 11 = INTERRUPT

■ Direction. 1 = IN, 0 = OUT.

■ Buffering. EP2 and EP6 only. Two bits, BUF1:0 control

the depth of buffering.

❐ 00 = quad

❐ 01 = invalid

❐ 10 = double (default)

❐ 11 = triple

(2)flag标志。

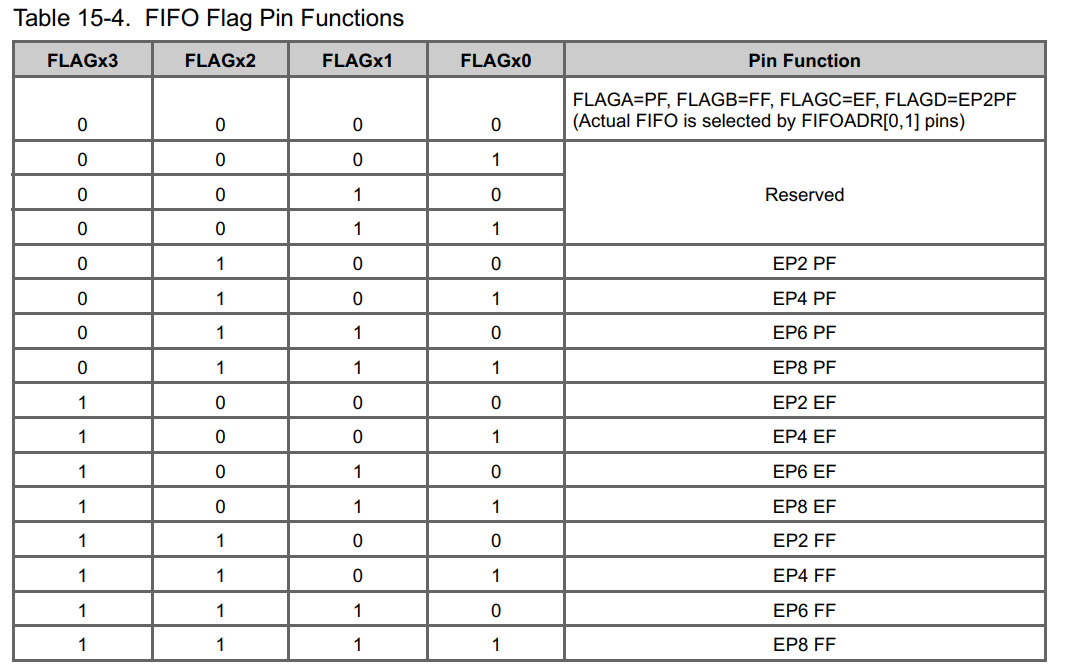

EZ-USB共有4 个标志flgaA,flagB,flagC,flagD。flagA ,flagB和flagC可以配置为索引模式和固定模式两种,而flagD只能配置成固定模式。

在索引模式下,

Flag pins configured for Indexed mode report the status of the FIFO currently selected by the FIFOADR[1:0] pins.

When configured for Indexed mode, FLAGA reports the programmable level status, FLAGB reports the ‘full’ status, and

FLAGC reports the ‘empty’ status

固定模式:

Flag pins configured for Fixed mode report one of the three conditions for a specific FIFO, regardless of the state of the

FIFOADR[1:0] pins. The condition and FIFO are userselectable.

空满标志极性:由FIFOPINPOLAR 寄存器设置。

The polarity of the ‘empty’ and ‘full’ flag pins defaults to

active-low but may be inverted via the FIFOPINPOLAR register.

PINFLAGSAB 寄存器配置flaga和flagb

PINFLAGSCD寄存器配置flagc和flagd

每个flag的4bit代表的意义:

对于0000的情况就是索引模式,在索引模式下标志信号对应的FIFO由FIFOADR1 和FIFOADR0来指示:

在非0000的情况就是固定模式。

flag

| flag | indexd | fixed | |||

| flagA | PF | ||||

| flagB | FF | ||||

| flagC | EF | ||||

| flagD | -- | ||||

| 由FIFOADR[1:0] 控制 |

与FIFOADR[1:0] 无关 |

| PIN | |||

| SLRD | slave read | 在同步模式,FIFO指针在IFCLK上升沿递增,在异步模式,FIFO指针在SLRD信号的断言到非断言跳变时增加 | |

| SLOE | slave output enable | 使能FD输出 | |

| SLWR | slave write | ||

| PKTEND |

Packet End | ||