VIP之CVI CVO

3、 VIP CVI CVO

在开始时,对于CVI和CVO是不知道应该怎样去调试的,就是不知道应该从哪里去确认是对还是错。

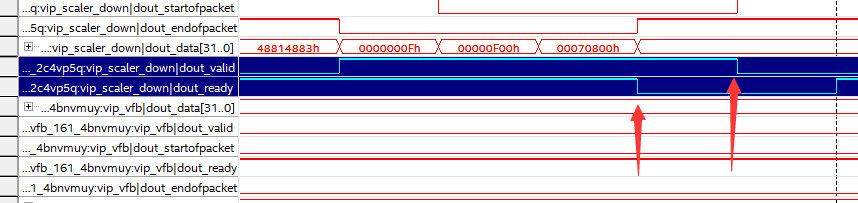

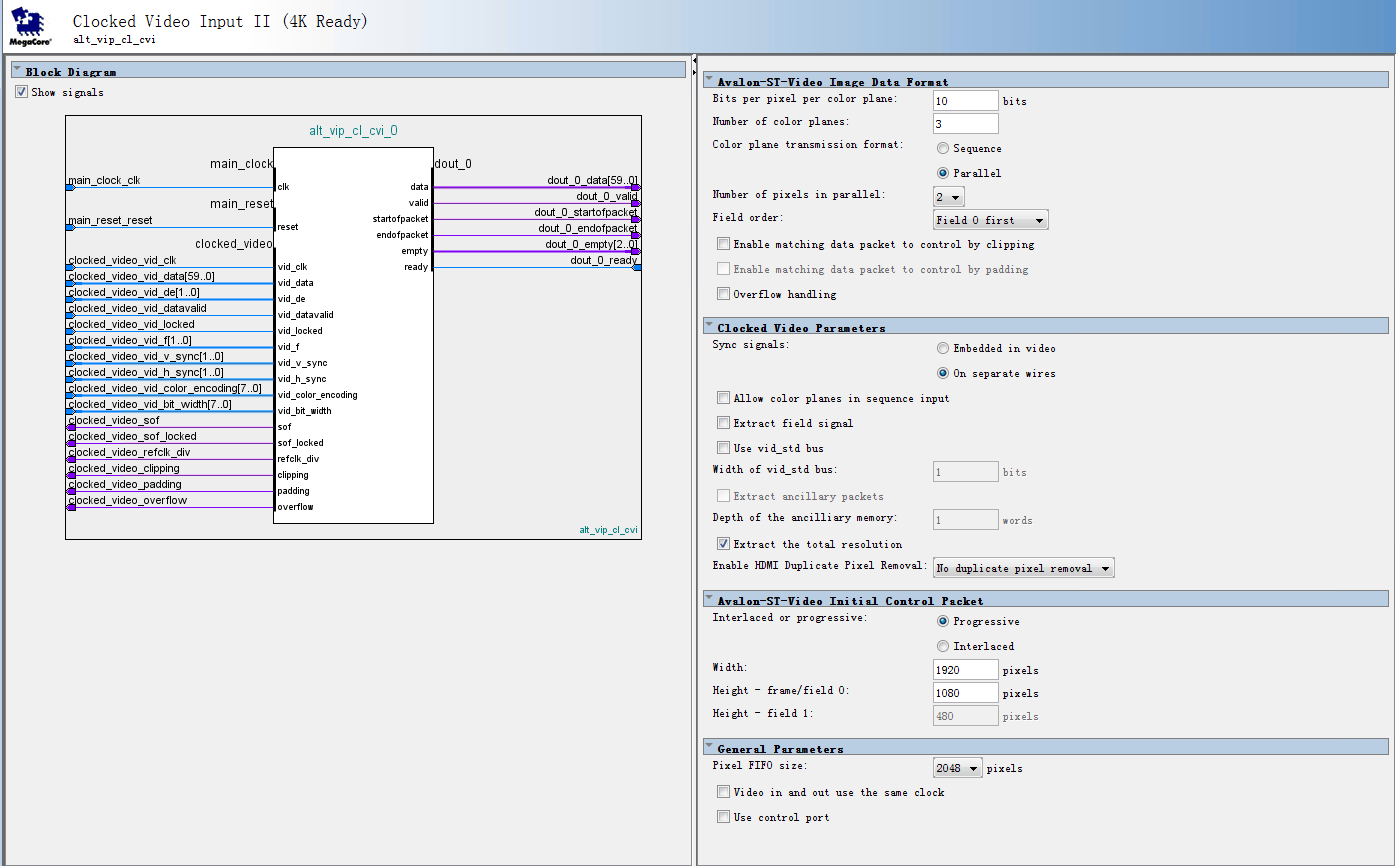

关于这一点从再次看到关于数据包的格式才明朗的。去分析CVI和输出数据包,发现存在控制数据包和视频数据包,其中

(1)控制数据包以00000000000000Fh开头的,后面是视频的分辨率(比如1920x1080),并且每个色彩面板只占用4位数据。在数据传输是两个像素并行传输,第个像素由3个色彩面板组成,所以每个数据由6个色彩面板组成。控制包的长度是13,所以只占用两个数据。

(2)视频数据包以00000000000000h开头,并且该包头数据对准SOF,视频数据一包的长度是一个帧,

懂得上述两点之后就知道怎样去调试了:在繁杂的数据中去找数据包,看看正确与否。

=============================================================

ready 信号的处理

=============================================================

在分析的过程中,发现ready信号明显与正确的程序中ready信号不一样。我的ready信号很少拉高,对此是有点手足无措的,对low latency mode选项设置为1,没想到就正确了。要说明的是valid信号只在检测到ready信号为高电平时,输入到CVI的数据才是有效的。

现在想来cvo的din_rdy信号拉高也没有什么玄乎的。只中CVO能处理数据就应该把din_rdy给拉高啊。同时也有必要对low latency mode 选项好好研究下。

=============================================================

想让CVI和CVO吐数据,最简单的设置是什么?

=============================================================

事实证明,只要打开go位,就能打开CVI。。。

CVO其实也应该是一样的,但是如果有问题的话,加上SET_MODE_1080p (VIP_HDMI_CVO_BASE, 0)

程序可能会更保险,不然hdmi_hpd_n可能会出现信号翻转也说不定哦。

==================================================================

CVI CVO的行场极性是怎样的?

==================================================================

==================================================================

CVI CVO时钟域是怎样的?

==================================================================

在调试过程中,因为用错了时钟,所以分析数据包时总是找不到SOF和EOF,所以在分析过程中要注意时钟域。