视频信号分辨率与帧率检测

(1)分辨率的检测

我是有看到别人提到用de信号去检测的,其实我以为,所有

的检测方式都大同小异,或者万变不离其宗:检测第一行有效的

像素数,检测每一帧有效的行数。

个人现在处理方式是,把所有接收到的信号,无论是行场同

步或者内嵌同步,都修改为行场同步,且跳变沿对齐有效数据。

所以检测行内像素数目即检测H信号下降沿(低电平指示有效)到

上升沿之间的时钟数即可。对于行数则检测从V信号下降沿到上升

沿之间有多少H上升(或者下降沿)沿即可。

(2)帧率检测

帧率检测就是通过计数器计时1s,再计数1s内V的上升沿与下降

沿的数目。为防止检测出错,可以可以限制1s内帧数的最大与最小

值,小于最小值与大于最大值都认为是不合理的值。帧率检测如果用

系统时钟会稍有偏差,所以最好用源时钟。但是源时钟会随分辨率及

帧率的不同而变化,那1s的计数值也会变化,这就要求用一个固定不

变的量才能锚定1s的计数值应该是多少,所以还是要用到系统时钟或者

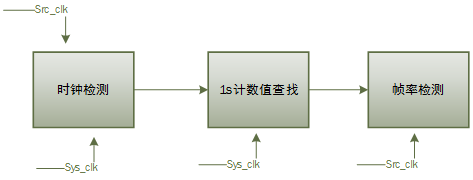

一个固定的时钟才行。以下是实现帧率检测用到的框图:

(1)时钟检测模块。该模块用系统时钟(sys_clk)去检测源时钟(src_clk)

时钟频率的大小,所以要求sys_clk为一个固定值,而src_clk时钟频率

可变,当两个时钟同时计数10ms时,可以通过两个计数值得出src_clk大小

(2)1s计数值查找模块。时钟检测模块检测到的时钟肯定是有偏差的,所有

一定要进行校正。具体不同的分辨率会有什么样的时钟要从相关文档上查找。

(3)帧率检测模块。既然从1s计数什查找模块可以确定1s计数的最大值,

那就在这1s内统计或者说计数有多少帧即可。