Quartus调用modelsim

1、Quartus 调用modelsim

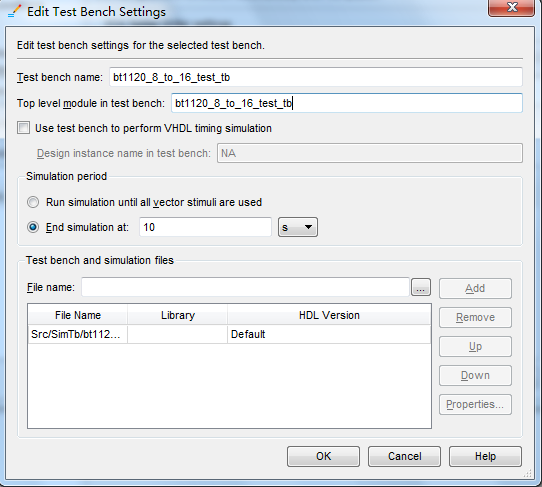

Test Bench Name :是test bench的文件名

Top Level module in test bench:test bench文件内的module名

2、Quartus 为什么每次调用modelsim都要重新编译一次

如果要仿真的文件不是顶层文件,就是把所有的文件都添加到Test Bench And Simulation Files下面:

在应用过程中我们会注意到,在每次调用modelsim的时候都会进行一次库的编译,非常耗时间,那怎样才能跳过每次的编译过程呢?

其实与xilinx的做法是相似的。

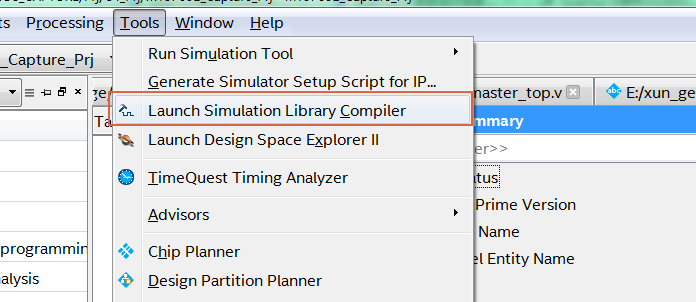

首先,编译所有的库。在Quartus中Tools菜单下找到Launch Simulation Library Compiler,点击进入

在EDA Simulation Library Compiler界面,设置以下选项。

其中Executable location是仿真器软件的路径,我这里选择modelsim,所以路径是modelsim的路径。

output directory是编译库的输出路径。

设置完成后点击start compilation

进入设置界面

点击more NativeLink Settings...

在location of user compiled simulation libray 选项中选择刚才编译的库路径。

这样,再启动仿真时就不会编译库文件了。

另外一个问题是添加用户脚本用于仿真:

当Quartus调用modelsim时会在工程文件下生成一个simulation文件夹,在该路径的modelsim文件下会生成一个xxx_run_msim_rtl_verilog.do,xxx表示工程名。

这个.do文件是在运行modelsim的一定会调用的,它用于执行所需要的库及源文件的的编译,并且随时会修改的,所以不能在内部做编辑。如果想要在运行完这个.do文件之后

想要执行用户自己的一些操作,可以在上图中选择勾选Use scrpt to set up simulation选项,添加自己的文件,这个文件可以为.do文件也可以为.tcl文件。

一定要记住的是用户的文件也会被xxx_run_msim_rtl_verilog.do文件调用。所以会在xxx_run_msim_rtl_verilog.do文件最后一句看到下面的一句:

do F:/VXP_8K/software/matrix_sim/simulation/modelsim/sim.tcl

那在自己的tcl文件中添加那些功能合适呢?我们可以添加wave保存的文件及run命名等。