FPGA FIFO笔记

FPGA FIFO笔记

ISE scope重新设置?怎么处理?必须重新设置cdc文件!

本章节内容,是我学习本课程感到最难以学会的章节。主要是卡在FIFO的两种模式:标准模式和FWFT模式的异同。

最终调试OK,原因就在于标准模式和FWFT模式的异同!

目前我的代码,输出第一行是对的,下面就不对了,明显是逻辑错了

学习方法改进:对于太复杂逻辑的项目,按照以下顺序学习,否则会造成反复,且效果不佳。

需要先通读一遍代码!以及原理!这是第一步,

然后再快速看一遍视频,

然后画出逻辑流程图!

根据流程图,自己撸一遍代码!

这个过程收获是巨大的!

对于复杂的逻辑,一定要使用modelsim仿真!仿真没有问题,综合后才有可能没有问题!复杂的逻辑一般是绝对不会一次性OK的。

readmemb语法和用法:

verilog中$readmemb和$readmemh的使用_m0_38037810的博客-CSDN博客 https://blog.csdn.net/m0_38037810/article/details/79598647

具体到本FIFO乒乓读写,包含IP核,包含多模块编程的体会:

1.需要把每个IP核输入的参数,都要有逻辑语句对应。always@()语句对应控制。IP输出的信号,用到的就用到,用不到的,reg声明一个参数丢进去不必管他了!

2.条件一致的,可以把参数合并

测试调试Ok,大工告成!

以下是FIFO学习遇到的问题:

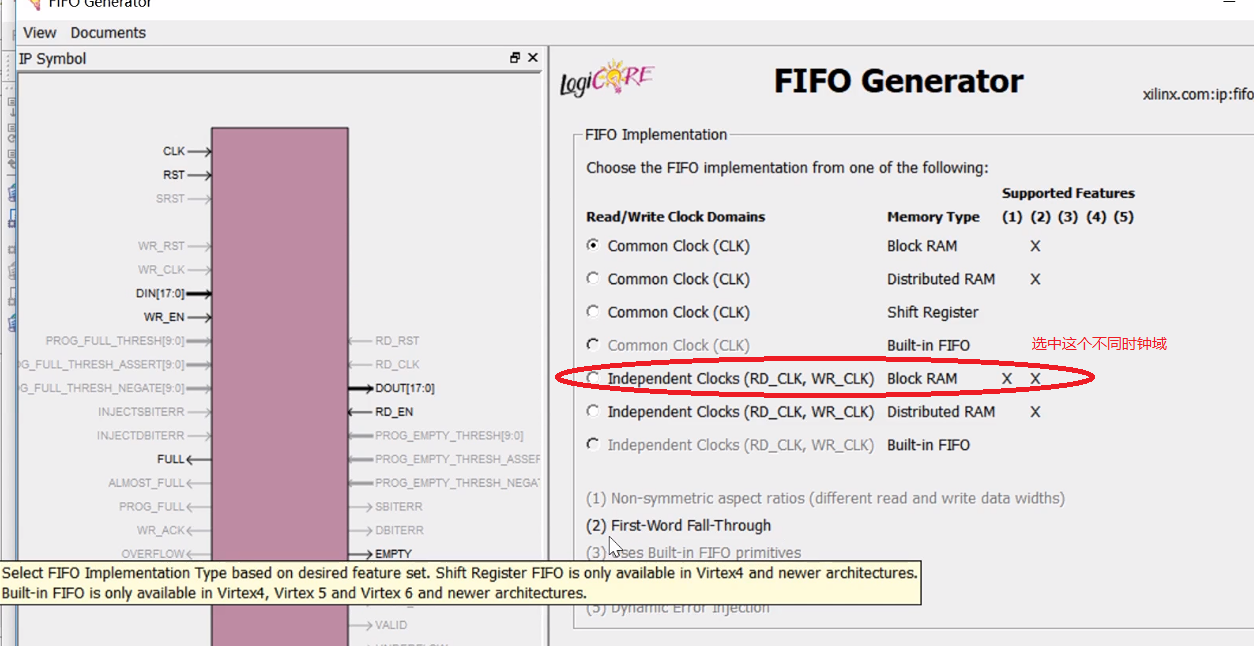

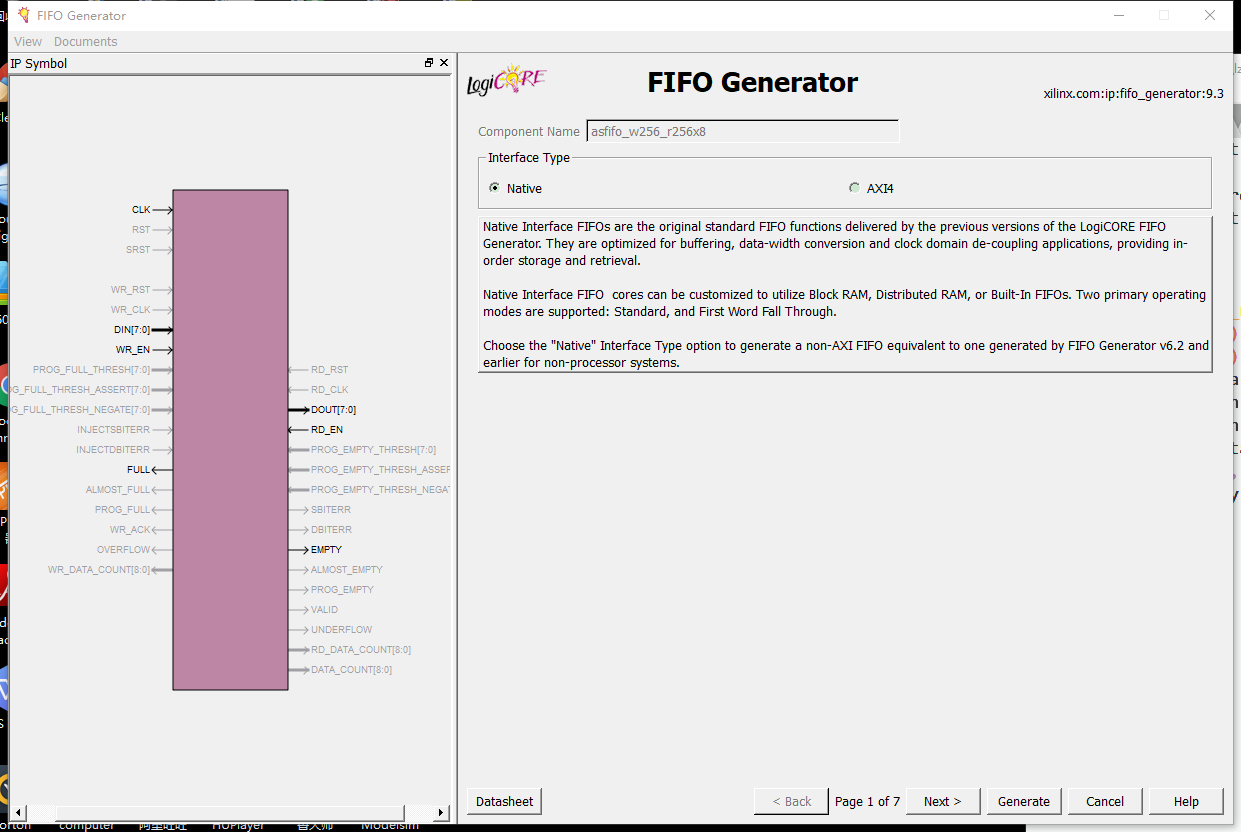

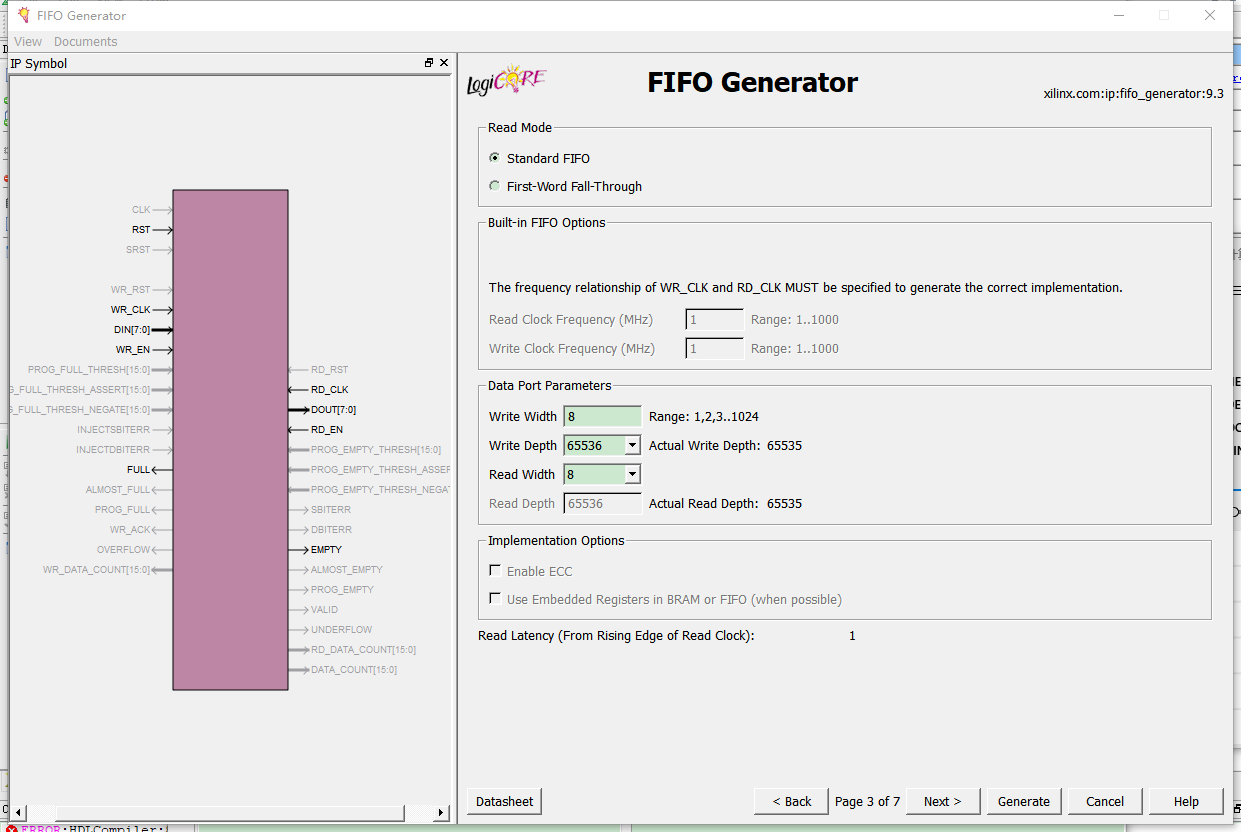

1.为什么我的FIFO核clk是单独一个,没有WR_CLK,和rd_clk

讲课内容:

2.什么情况下需要打一拍?比如下面这个

asfifo_w256x8_r256x8 fifo_inst (

.empty(empty) // output empty

。。。

);

always @(posedge clk) begin

empty_dly <= {empty_dly[0],empty};

//shift reg empty_dly == 2'b10 negedge

end

3.写时序,fifo_full这个信号,为什么没有使用到,是不需要。

4.xlinx的fpga的移位寄存器不能写复位 rst信号 敏感触发的

具体来说就是,不能使用组合{data[1],data[2:4]} = {};,不能使用 <<,>>移位操作!

//下面是读操作

always @(posedge clk) begin

empty_dly <= {empty_dly[0],empty};//shift reg empty_dly == 2'b10 negedge

end

是不是说,rst_n复位信号触发后,不能立即进行移位操作?clk打拍后才可以?

5.学到3个新技能:

5.1sublime右键,点击instancetian module 实例化,自动生成实例化模板,在模板上面修改下就可以使用

5.2ModuleSim软件在修改**.v后,使用命令行命令可以重新编译,

VSIM 5>do tb*****.fto

5.3 IP核的输入输出与reg,wire类型,IP输出要使用wire,输入一般使用reg。如下是ip输出:

wire [7 : 0] a_dout;//声明的时候,必须使用wire

fifo_a256x8_b256x8 tb_fifo (

.dout(a_dout), // output [7 : 0] dout

);

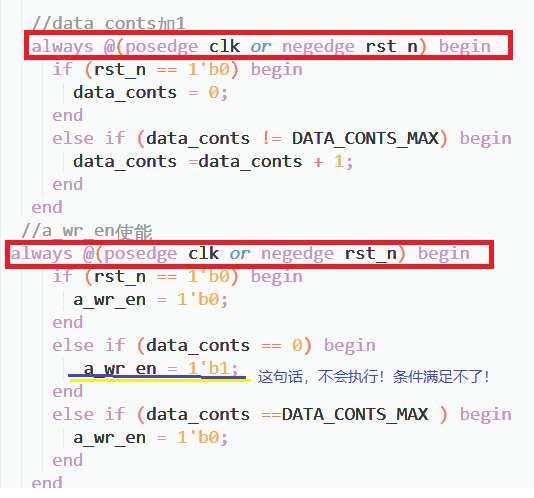

6.惊呆了!所有的always也不是绝对同步执行的,也有顺序的!

犯了错误!应该全部改为非阻塞赋值!!就可以了!

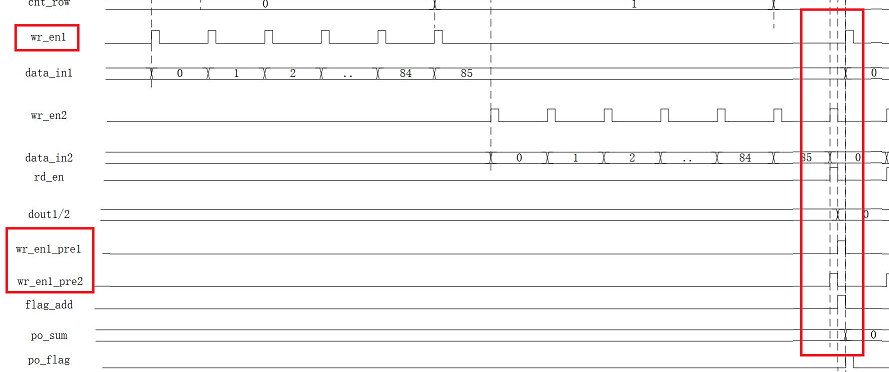

这个wr_en1,为什么要打2拍?wr_en2反而没有打2拍?为了对齐时序.

浙公网安备 33010602011771号

浙公网安备 33010602011771号