DRAM channel>DIMM>rank>chip>bank>row/column

一、DRAM的存储结构

channel>DIMM>rank>chip>bank>row/column

1、channel 和 DIMM,DIMM和RANK

SIMM----->DIMM

2、rank 和 chip

现在市场上的DIMM条一般都有2个RANK。rank 指的是连接到同 一个CS(Chip Select)的chip,内存控制器能对同 一 rank 的 chip 进行读写操作。

Rank

CPU与内存之间的接口位宽是64bit,也就意味着CPU在一个时钟周期内会向内存发送或从内存读取64bit的数据。可是,单个内存颗粒的位宽仅有4bit、8bit或16bit,个别也有32bit的。因此,必须把多个颗粒并联起来,组成一个位宽为64bit的数据集合,才可以和CPU互连。生产商把64bit集合称为一个物理BANK(Physical BANK),简写为P-BANK。为了和逻辑BANK相区分,也经常把P-BANK称为RANK或Physical RANK,把L-BANK则简称为BANK。如果每个内存颗粒的位宽是8bit,应该由8个颗粒并联起来,组成一个RANK(64bit);同理,如果颗粒的位宽是16bit,应该由4个颗粒组成一个RANK。由此可知:Rank其实就是一组内存颗粒位宽的集合,也可以叫Chips,在PCB上,往往把一面上的内存颗粒组成一个Rank,另一面是另外一个Rank(假若有的话),这样也可以将Rank理解内存条的Side(面)。具体说,当颗粒位宽×颗粒 数=64bits时,这个模组就是有一个RANK。为了保证和CPU的沟通,一个模组至少要有一个RANK。但是,为了保证有一定的内存容量,目前,DDR2内存,经常是采用一个模组两个RANK的架构。“模组构成”中的“R”“RANK”的意思。“2R”是说组成模组的RANK数(Number of ranks of memory installed)是2个。有“1R”和“2R”两种;“模组构成”中的“×8”是颗粒的位宽(bit width),有×4、×8和×16三种.

理论上,完全可以做出一个位宽为 64bit 的芯片来满足 P-Bank 的需要,但这对技术的要求很高, 在成本和实用性方面也都处于劣势。所以芯片的位宽一般都较小。台式机市场所用的 SDRAM 芯片位宽 最高也就是 16bit,常见的则是 8bit。这样,为了组成 P-Bank 所需的位宽,就需要多颗芯片并联工 作。对于 16bit 芯片,需要 4 颗(4×16bit=64bit)。对于 8bit 芯片,则就需要 8 颗了。

Chip(Memory)

存储芯片,又叫内存颗粒。真正提供存储的器件。

3、chip 和 bank

chip 往下拆分為 bank,如图所示,一个chip有8个bank。

4、bank 和 row/column

bank 往下拆就是 1 個個的儲存單元,橫向 1 排稱之為 row,直向 1 排稱之為 column,每排 column 的下方都有個 row buffer,用以暫存讀出來的 row 排資料。

一般來說橫向選擇排數的線路稱為 row(row enable、row select、word line),直向負責傳遞訊號的線路為column(bitline),每組 bank 的下方還會有個 row buffer(sense amplifier),負責將獨出的 row 資料暫存,等待 column 位址送到後輸出正確的位元,以及判斷儲存的逻辑值是 0 還是 1。

二、内存的读写

内存控制器和DIMM之间的线路连接如下:

一个bank的读操作如下:

一个bank的写操作如下:

读操作时,首先内存控制器會將 1 組地址由位址線傳到内存上,控制線跟著傳送控制訊號;如果是多 rank 的安裝情形,CS 也會送出對應的訊號選擇目標 rank。接著由於每個 rank 由許多 chip 組成,1 個 chip 僅負責部分的資料讀取,chip 接收到位址訊號後,將位址丟入內部的 row/column 解碼器找出相對應的 bank 位址(每家每款產品的內部 bank 組合有可能不同,因此對應也會有所不同),接著開啟 row 線,同 1 排 row 的內部資料就會流到 row buffer 內部,row buffer 判斷訊號為 0 或是 1 之後就輸出資料。

写操作时,除了地址数据外,还会传送欲写入的数据至晶片內部的 input buffer,同樣的也是依照 row/column 解碼器找出對應位置之后再写入。

问题:Rank, 位宽,行列的关系;

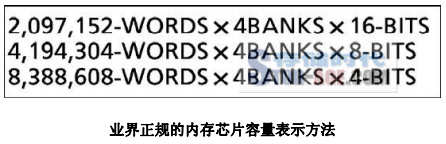

我们可以计算一下,结果可以发现这三个规格的容量都是 128Mbits,只是由于位宽的变化引起 了存储单元的数量变化。从这个例子就也可以看出,在相同的总容量下,位宽可以采用多种不同的设 计。所以相同的一个矩阵,可以通过不同的方式划分,以满足不同的需求;

为什么常用的是X4,X8,X16?

高位宽的芯片可以让 DIMM 的设计简单一些(因为所用的芯片少),但在芯片容量相同时,这种 DIMM 的容量就肯定比不上采用低位宽芯片的模组,因为后者在一个 P- Bank 中可以容纳更多的芯片。 比如上文中那个内存芯片容量标识图,容量都是 128Mbit,合 16MB。如果 DIMM 采用双 P-Bank+16bit 芯 片设计,那么只能容纳 8 颗芯片,计 128MB。但如果采用 4bit 位宽芯片,则可容纳 32 颗芯片,计 512MB。 DIMM 容量前后相差出 4 倍,可见芯片位宽对 DIMM 设计的重要性。

因此,8bit 位宽芯片是桌面台式机上容量与成本之间平衡性较好的选择,所以在市场上也最为 普及,而高于 16bit 位宽的芯片一般用在需要更大位宽的场合,如显卡等,至于 4bit 位宽芯片很明 显非常适用于大容量内存应用领域,基本不会在标准的 Unbuffered 模组设计中出现。

不同的位宽,如何控制引脚?

在一个容量标准下,SDRAM 的引脚/信号标准不能只考虑一种位宽的设计,而是要顾及多种位宽,然后尽量给出一个通用的标准, 小位宽的芯片也许会空出一些引脚,但高位宽的芯片可能就全部用上了。不过容量不同时,设计标准 也会有所不同,一般的容量越小的芯片所需要的引脚也就越小。

1、首先,我们知道内存控制器要先确定一个 P-Bank 的芯片集合,然后才对这集合中的芯片进 行寻址操作。因此要有一个片选的信号,它一次选择一个 P-Bank 的芯片集(根据位宽的不同,数量 也不同)。被选中的芯片将同时接收或读取数据,所以要有一个片选信号。

2、接下来是对所有被选中的芯片进行统一的 L-Bank 的寻址,目前 SDRAM 中 L-Bank 的数量最 高为 4 个,所以需要两个 L-Bank 地址信号。

3、最后就是对被选中的芯片进行统一的行/列(存储单元)寻址。地址线数量要根据芯片的组织 结构分别设计了。但在相同容量下,行数不变,只有列数会根据位宽的而变化,位宽越大,列数越少, 因为所需的存储单元减少了。

4、找到了存储单元后,被选中的芯片就要进行统一的数据传输,那么肯定要有与位宽相同数量 的数据 I/O 通道才行,所以肯定要有相应数量的数据线引脚。现在我们就基本知道了内存芯片的一些 信号引脚,下图就是一个简单的 SDRAM 示意图,大家可以详细看看。

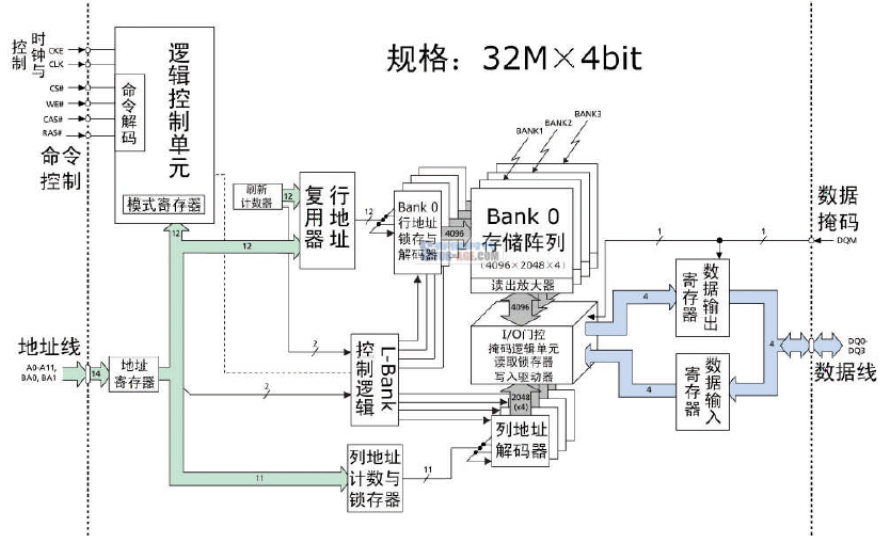

两个DRAM 晶片的内部功能图如下所示: