aarch64 VMSA - VA PA translation regime

参考:Arm Architecture Reference Manual for A-profile architecture

Chapter D5 The AArch64 Virtual Memory System Architecture

本文只从里面摘取,使用 AArch64 模式时的相关信息。

address type

VA Virtual address

PA physical address

IPA Intermediate physical address [ 用虚拟机跑操作系统,使用两层地址转换,第一层转换输出地址叫 IPA ]

VA 地址的长度

VA 最大长度(芯片设计后不可配置修改)

三下面3选1

(注:按个人理解,这儿是 architecture reference 里面的,是指 芯片实现时,可以 3 选 1 。而当芯片设计实现后,比如A53芯片,它的 最大VA 长度 是 确定 的 )

48

52 实现了 FEAT_LVA 并且以 64K 作为页大小,

52 实现了FEAT_LPA2, 并且 TCR_ELx.DS == 1 ,并且 使用 4K 或 16K 作为 页大小。

MMU translation输入VA 的长度(芯片使用中软件可配置)

translation regime 可以通过寄存器配置,支持 比 最大VA 长度 小的 VA 地址范围。

TCR_ELx.TxSZ

VA 地址长度为 64-TxSZ.

TxSZ 为 6 bits ,可以取值为 0 ~ 64. 取 16时, 地址转换单元的 输入 VA 为 64 - 16 = 48 bits.

PA 地址长度

PA 地址最大长度(芯片确定后不可配置修改)

ID_AA64MMFR0_EL1.PARange 反映了 芯片 实现的 PA 地址长度。芯片 设计后不可配置修改。

0000 - 32 bits

0001 - 36 bits

0010 - 40 bits

0011 - 42 bits

0100 - 44 bits

0101 - 48 bits

0110 - 52 bits

MMU translation output PA 地址长度(可配置)

TCR_ELx.{I}PS 配置决定

000 - 32 bits

001 - 36 bits

010 - 40 bits

011 - 42 bits

100 - 44 bits

101 - 48 bits

110 - 52 bits

address bits above the output address size set to zero

MMU 把高于 配置地址 size 的 bit 设为0;

translation stage - translation regime 地址转机制

有两类:

single stage translation - 单步 地址转换机制

two stage translation - 两步地址转换机制(只在 虚拟机+客户操作系统 这样的场景中使用到 )。

translation stage 对VA 的支持(以 48bits 长度的VA 为例,52 bits 长度的 VA 同理)

可以只支持 一段 VA 地址范围。 VA 范围必须为 0x0000 0000 0000 0000 到 0x0000 ffff ffff ffff ffff

可以支持 两段 VA 地址范围。一段VA 地址范围必须是在 64bits 地址范围的 最低端,另外一段VA 范围 必须在 64bits 地址范围的 最高端。

Bottom VA range: 0x0000 0000 0000 0000 到 0x0000 ffff ffff ffff

top VA range: 0xffff 0000 0000 0000 到 0xffff ffff ffff ffff ;

(芯片)如果没有 实现 FEAT_VHE ,只有 EL1 & 0 Translation regime 的 stage 支持 两段 VA 地址范围。

(芯片)如果 有 实现 FEAT_VHE ,HCR_EL2.E2H == 1, 时,EL2 translation regime 的 stage1 , EL2&0 translation regime 也 支持 两段 VA 地址范围。

address tag

TCR_ELx.TBI 控制 是否启用 address tag.

启用了 address tag, VA 地址的高 8 bits 会被 忽略。 bit[63 62 61 60 59 58 57 56]被忽略。

bit[55] 决定 使用 TCR_ELX.TBI{0 or 1} 来控制,是否启用 address tag.

VA 的 bit[55] 来决定了使用 TTBR{0 or 1}_ELx 来加载 translation table 的基地址

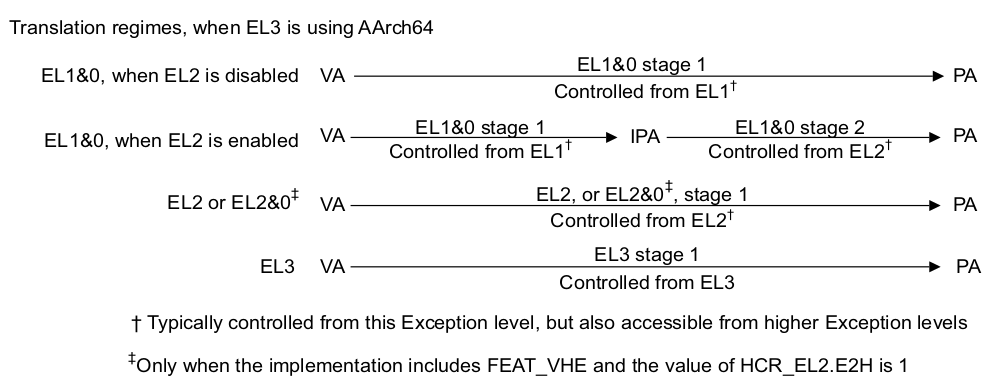

armv8 架构 定义的 地址转换机制

芯片实现时,可以 只实现 其中的一部分。

转换机制介绍

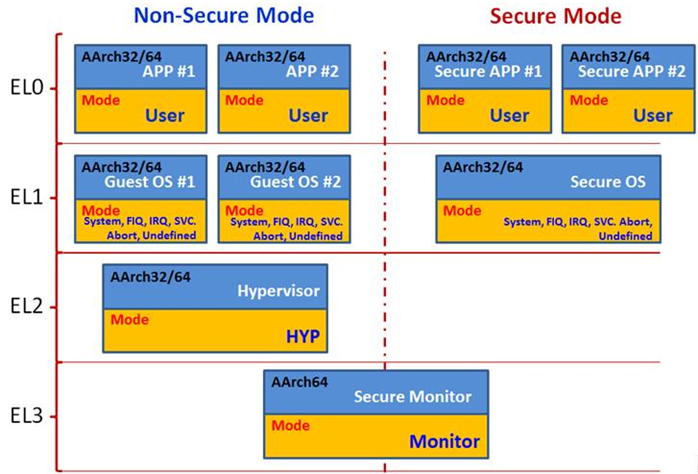

从下向上看,

EL3 stage 1 转换机制。 是一个 single stage 的转换机制。

EL2 or EL2 & 0 转换机制,是一个 single stage 的转换机制。 EL2 & 0 转换机制,只有当 芯片实现了 FEAT_VHE 特性,并且 HCR_EL2.E2H == 1 是才启用。

EL1 & 0 【EL2 启用状态下的】转换机制。如下图, EL2 启用,则说明有 Hypervisor在运行,EL1 的 OS kernel 相当于运行在一个虚拟机里面, 虚拟地址到 物理地址,则需要进行 两次转换。

EL1 & 0 【EL2 关闭状态下的】转换机制。EL2 没有启用,则说明 EL1 的 OS kernel 运行在 物理板子上面,虚拟地址到 物理地址,需要进行一次转换即可。

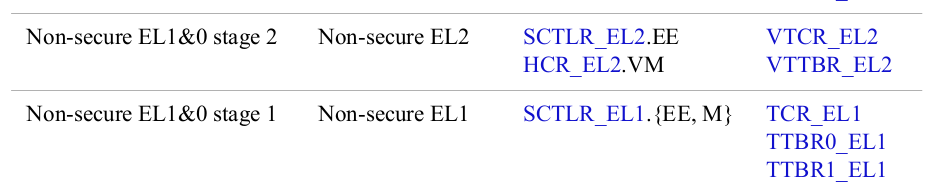

转换机制控制(寄存器)

linux kernel 如果运行在 物理板子上面,使用 TCR_EL1 & TTBR0_EL1 & TTBR1_EL1 & SCTRL_EL1 寄存器 即可控制地址转换。

hypervisor (虚拟机)想要 管理 客户机 linux kernel 的地址转换,则设置 VTCR_EL2 & VTTBR_EL2 & HCR_EL2 & SCTLR_EL2 寄存器。