Basis that U have to know

FPGA design flow

1. design specification

2. architecture design

3. HDL design entry & test environment design

4. behavior simulation

5. synthesis, HDL to netlist

6. Implementation, place, route and layout

7. Timing analysis

8. programming to device

ASIC design flow

1. SPECIFICATION

2. MODELLING

3. LOGIC DESIGN

4. SYNTHESIS

5. VERIFICATION

6. TEST GENERATION

7. Mapping

8. Place & Route

9. Configuration data

10. PROTO VERIFICATION

Verilog HDL 抽象级别

1. Behavioral level

2. RTL level

3. Gate level

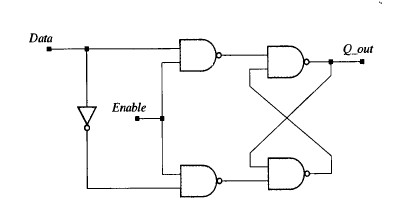

Data Latch

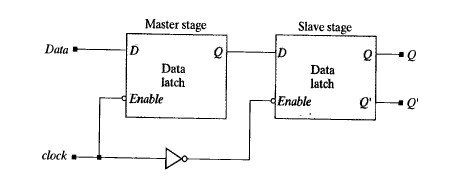

D flip-flop

四级流水线

• 取指级(IF):从存储器取指令,每个周期取出一条指令。PC加4

• 译码级(DE):译出所要执行的指令的功能并识别出所需的资源,这些资源包括通用寄存器、总线和功能部件,提供流水线控制互锁,并从寄存器读出操作数。

• 执行级(EX):完成指令功能。

• 写回级(WB):用来将结果或存储器读出的数据写入寄存器。

常用加法器

• 行波进位加法器

• 先行进位加法器

• 选择进位加法器

gi = ai · bi

pi = ai Å bi

ci+1 = gi + pi · ci

si = ai Å bi Å ci

eg。 c4= g3+p3g2+p3p2g1+p3p2p1g0+p3p2p1p0c0

posted on 2009-12-28 17:03 Homography Matrix 阅读(169) 评论(0) 编辑 收藏 举报