verilog-"10101"状态机序列检测器的设计

首先,画出状态转移图

代码:

module xulie10101 #(

parameter S0 = 3'b000,//状态定义

parameter S1 = 3'b001,

parameter S2 = 3'b010,

parameter S3 = 3'b011,

parameter S4 = 3'b100

)

(

input in,

input clk,

input reset,

output out

);

input clk,reset,in;//输入输出

output reg out;

reg [2:0] state;

reg [2:0] next_state;//寄存状态

always @ (posedge clk)//状态切换

if(reset)

state <= S0;

else

state <= next_state;

always @ (in or state)

begin

case(state)

S0:

begin

if (in)

begin

next_state <= S1;

out = 1'b0;

end

else

begin

next_state <= S0;

out = 1'b0;

end

end

S1:begin

if (in) begin

next_state <= S1;

out = 1'b0;

end

else begin

next_state <= S2;

out = 1'b0;

end

end

S2:begin

if (in) begin

next_state <= S3;

out = 1'b0;

end

else begin

next_state <= S0;

out = 1'b0;

end

end

S3:begin

if (in) begin

next_state <= S1;

out = 1'b0;

end

else begin

next_state <= S4;

out = 1'b0;

end

end

S4:begin

if (in) begin

next_state <= S1;

out = 1'b1;

end

else begin

next_state <= S0;

out = 1'b0;

end

end

endcase

end

endmodule

测试代码:

module xulie10101_tb();

wire out;

wire state,next_state;

reg in;

reg clk,reset;

initial

begin //time

clk = 0;

forever #50 clk = ~clk;

end

initial

begin

in = 0;

reset = 1;

#200 reset = 0;

#50 in = 1;#100 in = 0;#100 in = 1;

#100 in = 0;#100 in = 1;#100 in = 0;

#100 in = 1;#100 in = 1;#100 in = 1;

#100 in = 1;#100 in = 0;#100 in = 1;

#100 in = 1;#100 in = 1;#100 in = 1;

#100 in = 1;#100 in = 0;#100 in = 1;

#100 in = 0;#100 in = 1;#100 in = 0;

end

xulie10101 m( .in(in),

.out(out),

.clk(clk),

.reset(reset));

endmodule

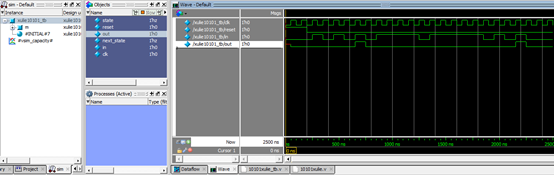

仿真结果:

越是憧憬,越要风雨兼程