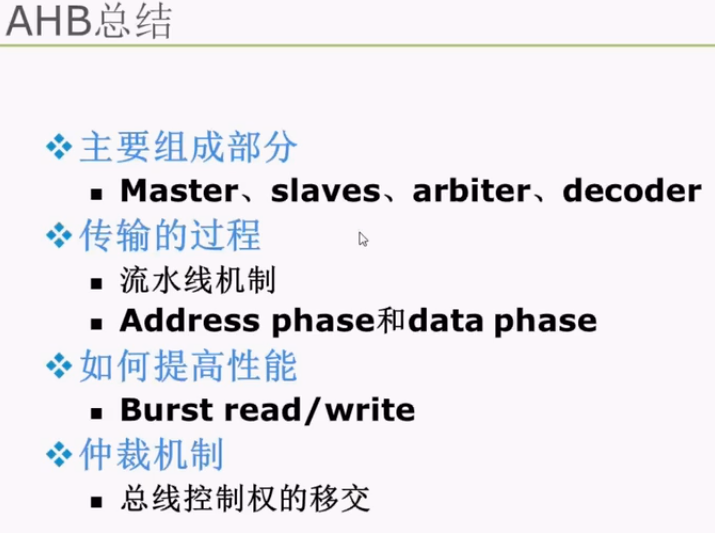

AHB

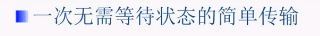

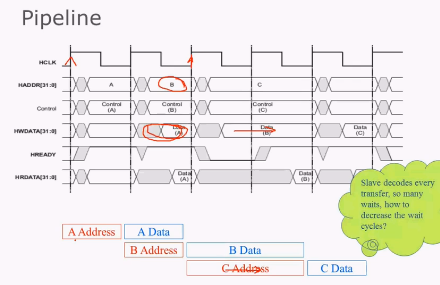

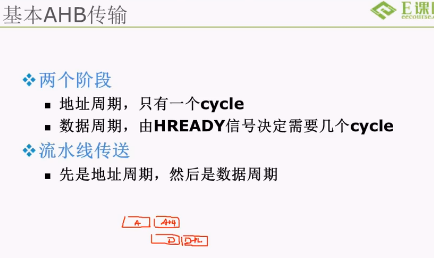

AHB bus上面 一次完整的transfer可以分为两个阶段:

address phase 传送 address、control signal

data phase 传送 write/read data、response signal

在T1上升沿,Master给出了address和control

在T2上升沿,如果是写操作,Slave采样address和control,即从主设备写到从设备,体现为HWDATA上出现数据

在T3上升沿,如果是读操作,Master采样data,即从从设备读到主设备,体现将HRDATA上的数据送给Master

T1 T2 T3

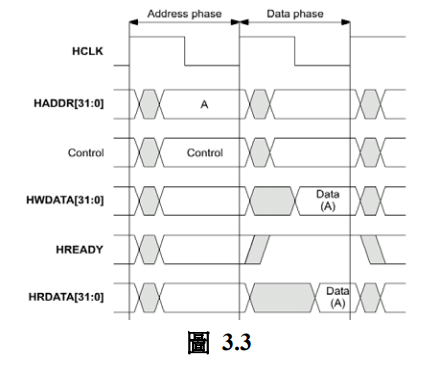

如果向从设备写数据的时候发现Slave没有准备好怎么办?

第一个时钟上升沿,主设备给出了address和control

第二个时钟上升沿,?把数据发送到HWDATA

第三个时钟上升沿,?发现HREADY为低,于是Master知道此时Slave是busy的,于是继续在HWDATA上面发送data

第四个时钟上升沿,HREADY依然为低,继续发送DATA

第五个时钟上升沿,HREADY为高,该写入从设备的就写入。同时对于HRDATA上的数据,该主设备读走就读走。

一拍数据一拍地址这样比较低效率。

一次transfer需要两个phase,为了增加bus的性能,引入流水线:

slave一直在响应

------------------------------------------------------------------------------------------------------------------------------

------------------------------------------------------------------------------------------------------------------------------

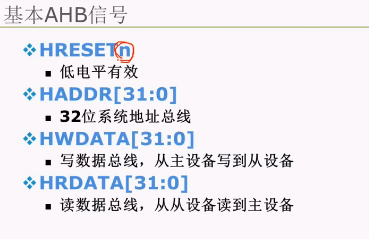

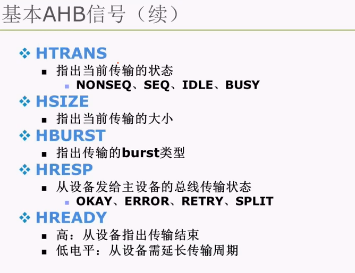

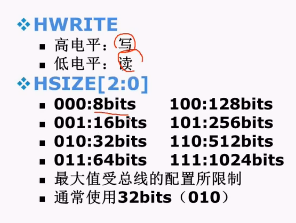

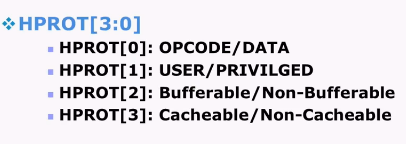

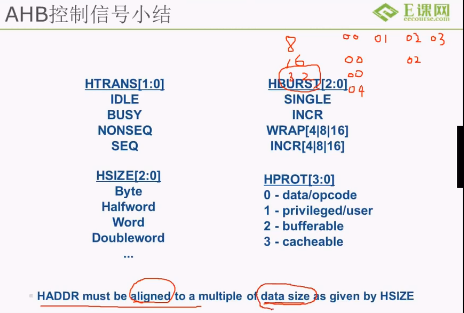

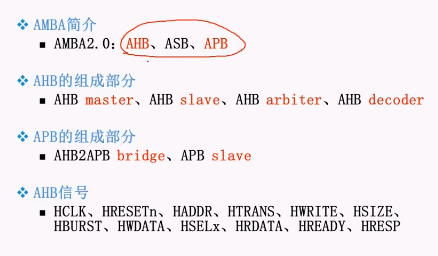

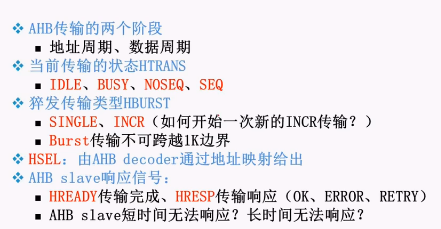

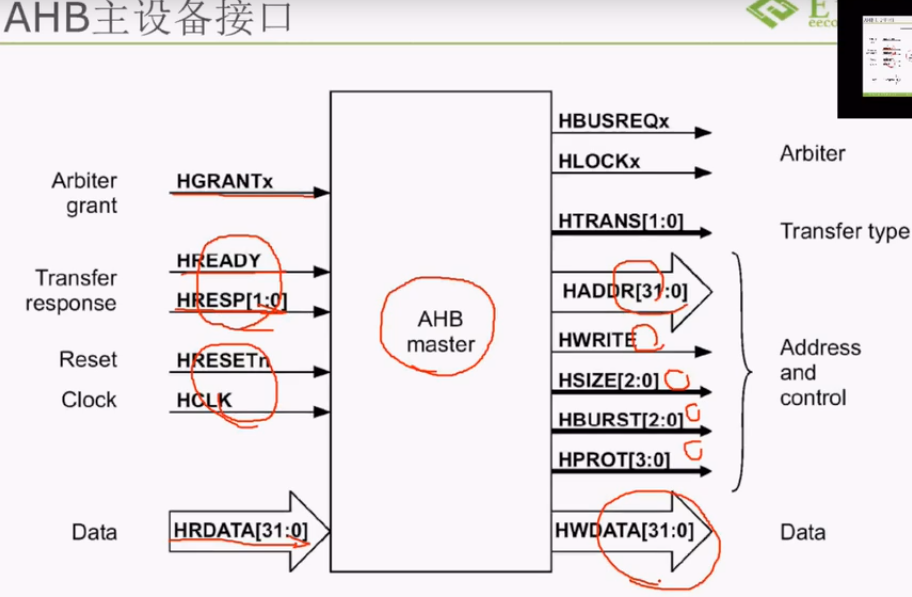

AHB上的control signal:

control选择器的输出信号会连接到Slave和Abiter(HTRANS HBURST)

control选择器的输入信号来自Master

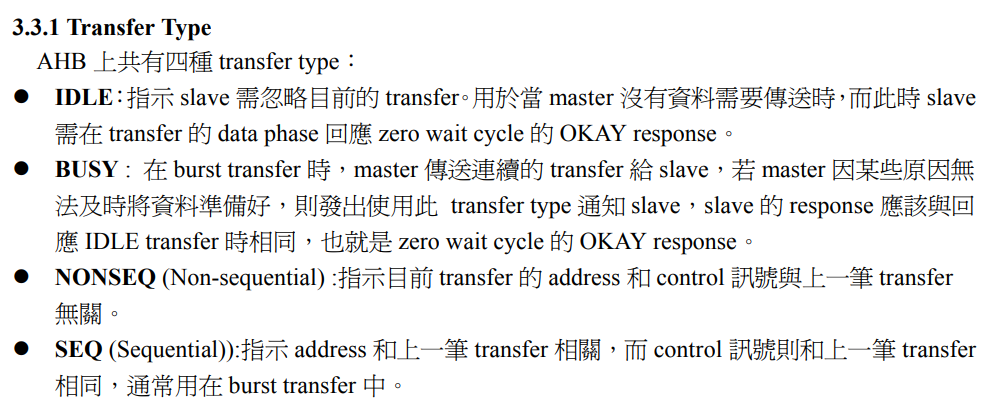

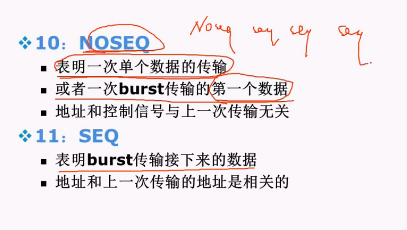

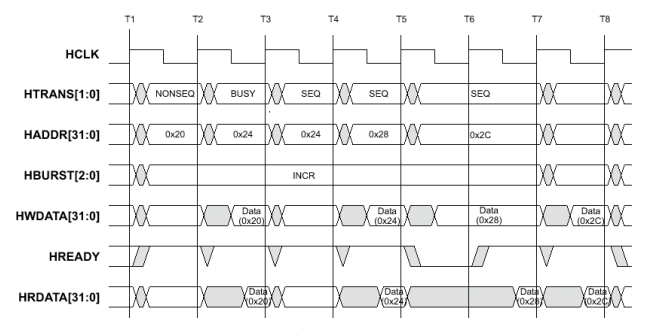

传输类型举例 配合HTRANS\HBURST:

第一个时钟周期,HTRANS根据协议规定发送NOSEQ

第二个时钟周期,假设HTRANS发送BUSY,表示主设备busy;HWDATA/HRDATA出现第一个地址的数据

第三个时钟周期,假设HTRANS发送SEQ,表示burst传输接下来的数据

因为采样到BUSY的原因,这一时钟周期的HWDATA/HRDATA出现第二个地址的数据是无效的

第四个时钟周期,假设HTRANS发送SEQ,表示burst传输接下来的数据;HWDATA/HRDATA出现第三个地址的数据

第五个时钟周期,假设HTRANS发送SEQ,表示burst传输接下来的数据;HWDATA/HRDATA出现第四个地址的数据

第六个时钟周期,因为在这一周期的时钟上升沿,HREADY为低,主设备知道从设备busy,于是延长HTRANS / HADDR / HWDATA / HRDATA

第七个时钟周期,HWDATA/HRDATA出现第五个地址的数据

这个针对cpu,通知外设 的行为

这个针对cpu,通知外设 的行为

----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------

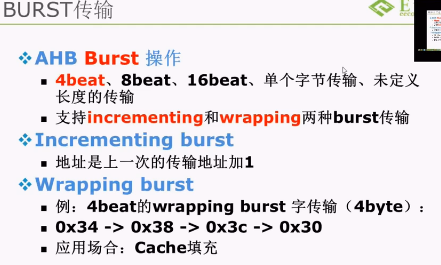

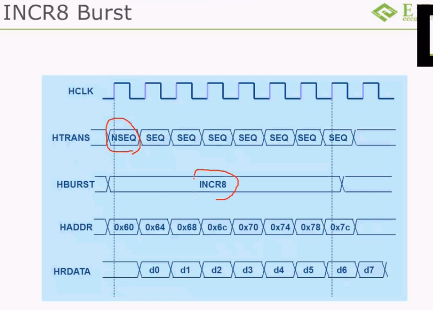

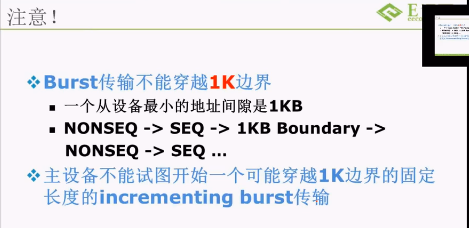

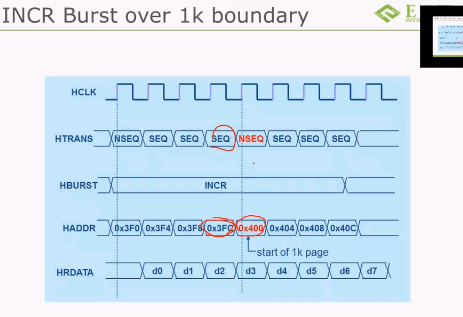

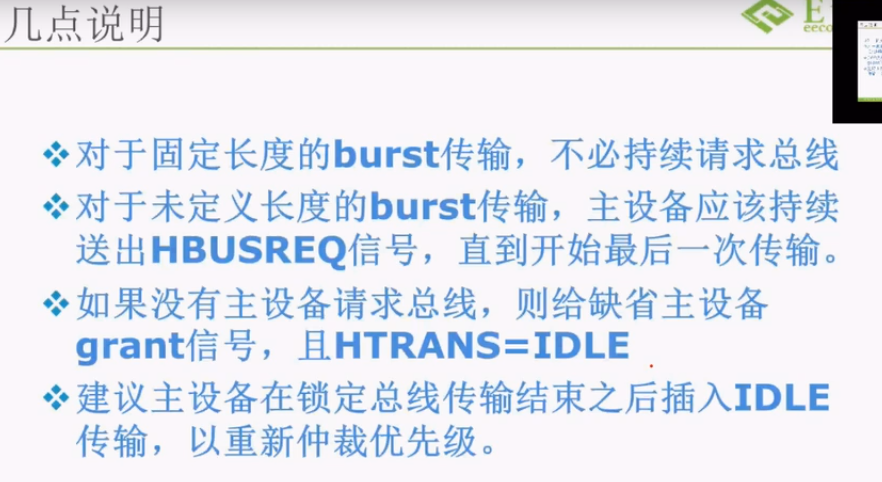

AHB BURST传输

除了cpu(cache填充)之外很少有wrapping burst

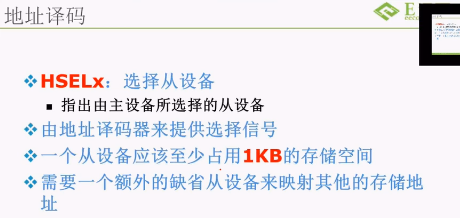

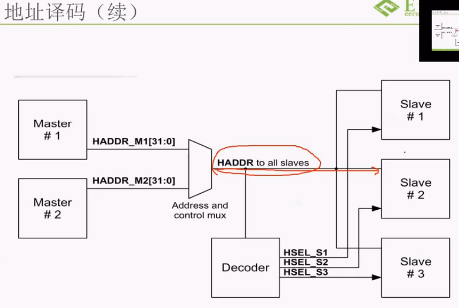

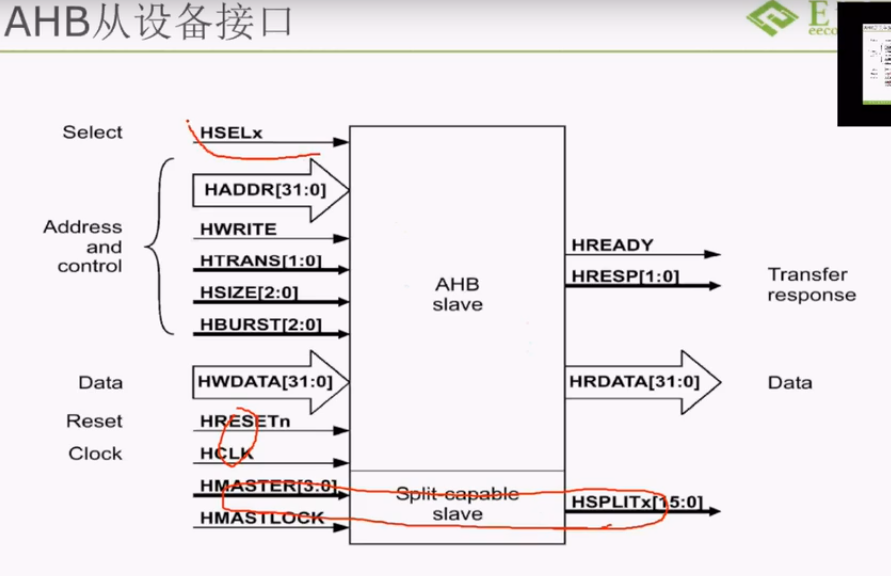

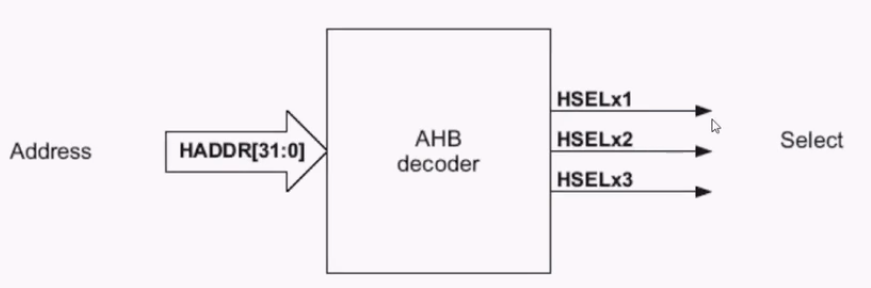

每一个slave都会都到地址,但哪一个会做处理取决于HESL_

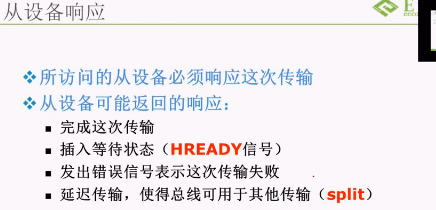

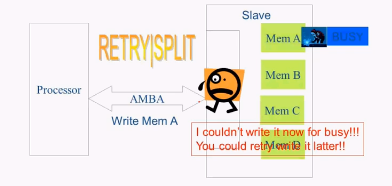

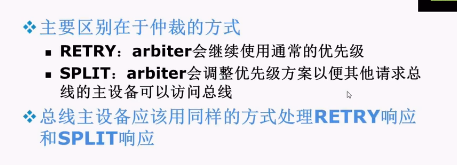

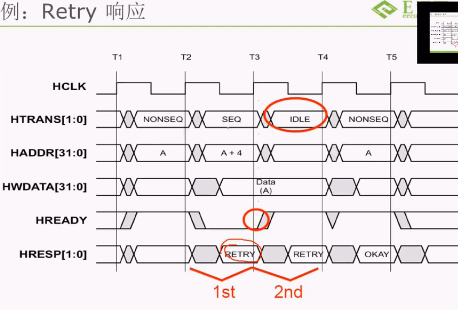

发现retry后 插idle

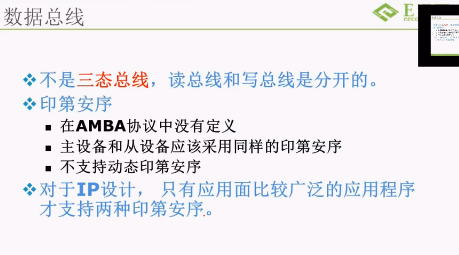

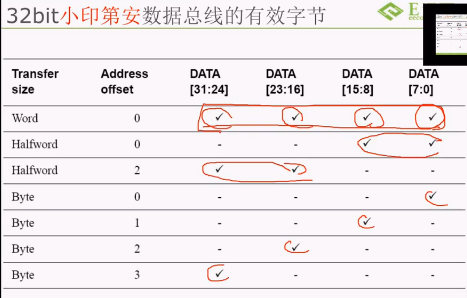

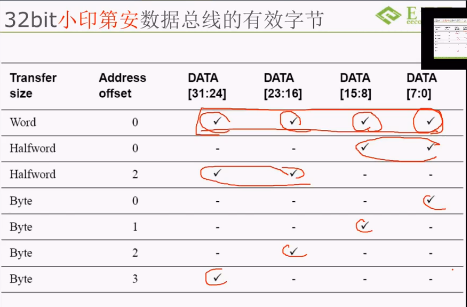

印第安序指大小端,本时序系统使用小印第安序

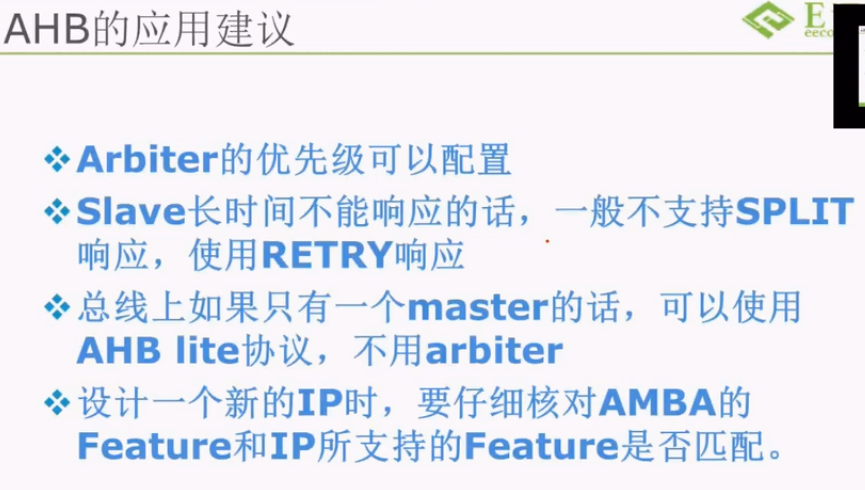

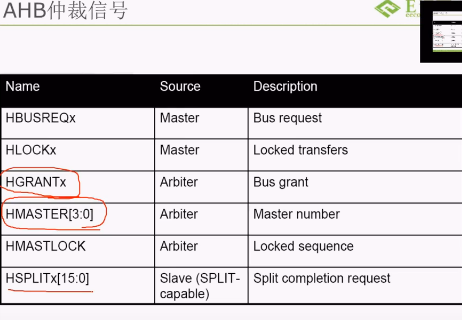

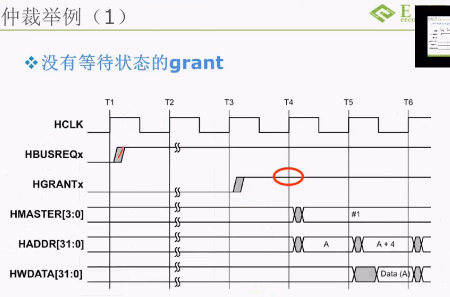

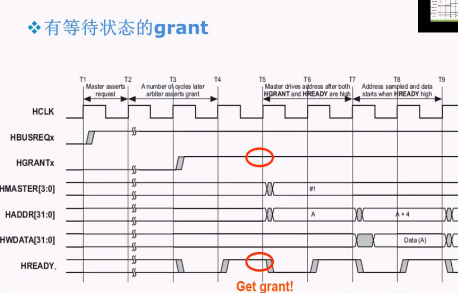

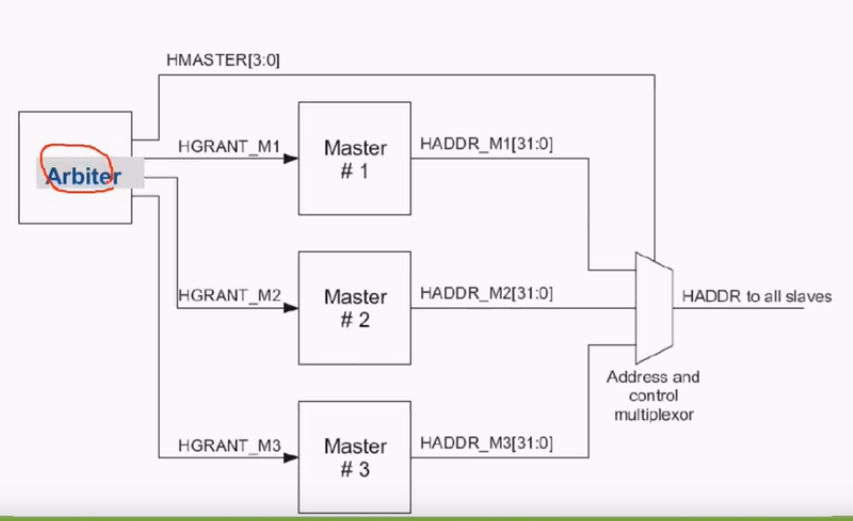

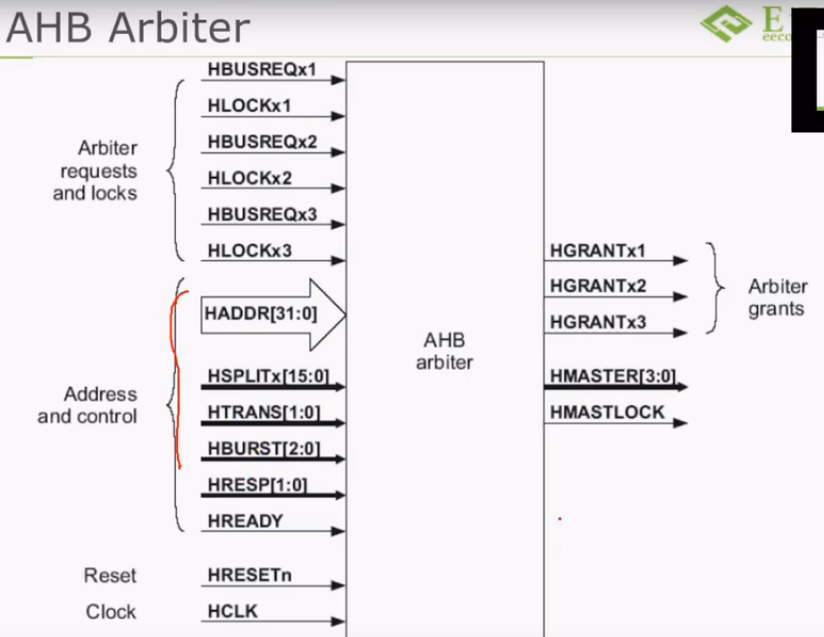

多个主设备的时候需要仲裁器:

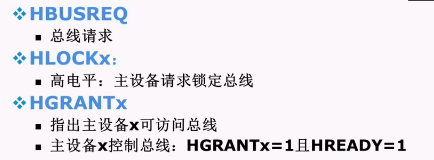

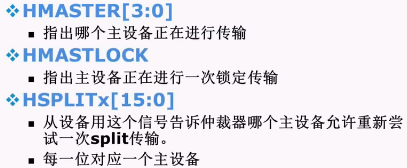

总线看到HGRANT,所以主设备开始传输地址和数据

总线看到HGRANT,所以主设备开始传输地址和数据

因为HREADY为低所以执行了两拍

因为HREADY为低所以执行了两拍

第一个周期主设备M1请求,第三个周期主设备M2请求,第五个时钟个周期HGRANT有个一交接;

但是要允许M1做一个收尾,HREADY下拉,允许M1再多传输一个时钟周期:

spilt传输不讲 很少遇到

----------------------------------------------------------------------------------------------------------------------------------------------------------------

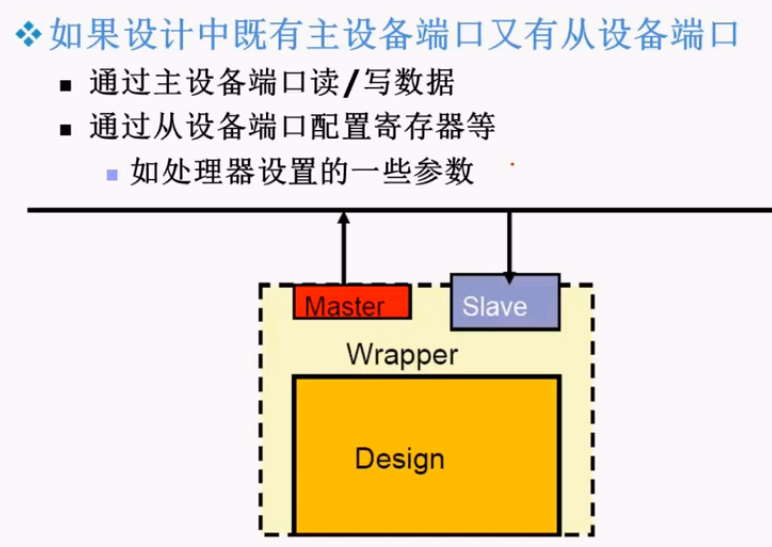

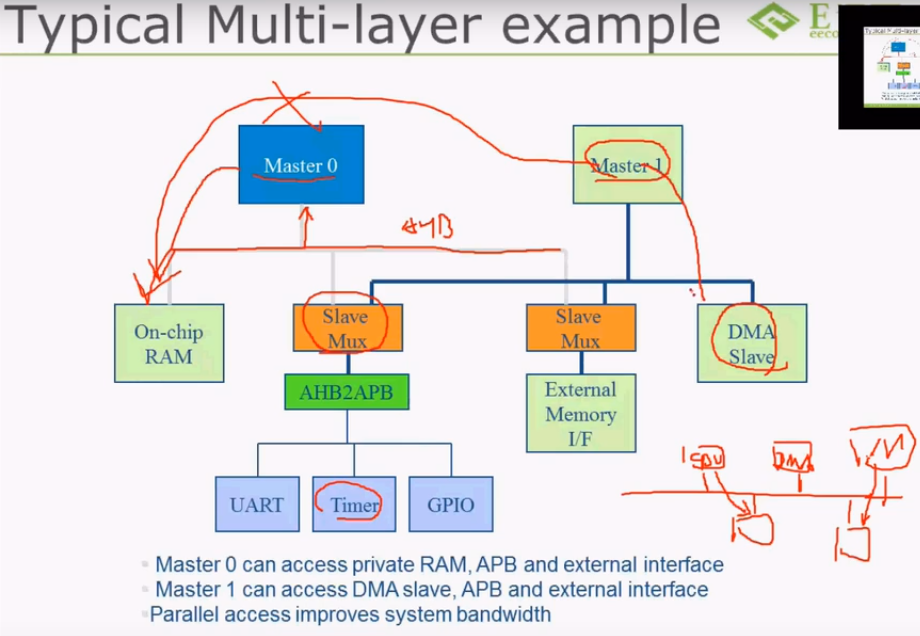

多层bus结构,好处是不同master对不同slave的访问可以并发进行:

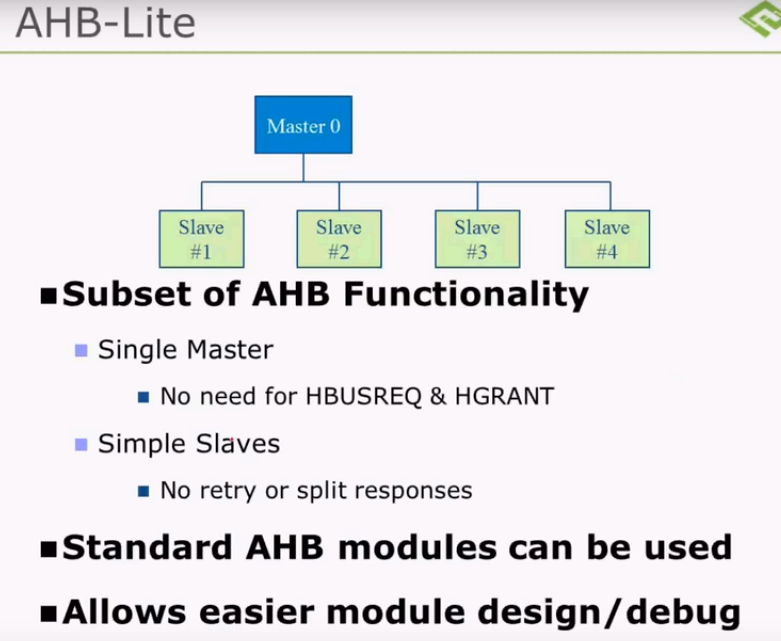

AHB-Lite是AHB功能的子集,它规定总线上只有一个Master:

就不存在仲裁器,自然也没有hgrant和hmaster,使用类似上面buss的结构生成一个类似矩阵的结构