STA基础chapter2

又回到最初的起点hhhhhhh

静态时序分析那本厚厚的英文pdf被我搞来了,超级厚!不想看!但是,集成电路的女人不能认输!

一点点来吧~

跳过章节1

chapter2 sta原则

2.1cmos逻辑设计

2.1.1基本mos结构

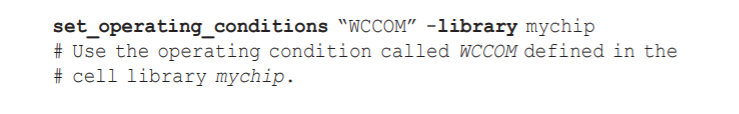

0.25um技术允许制作沟道长度大于等于0.25um的mos晶体管。沟道长度:channel length

2.1.2cmos逻辑门

经典的反相器例子:

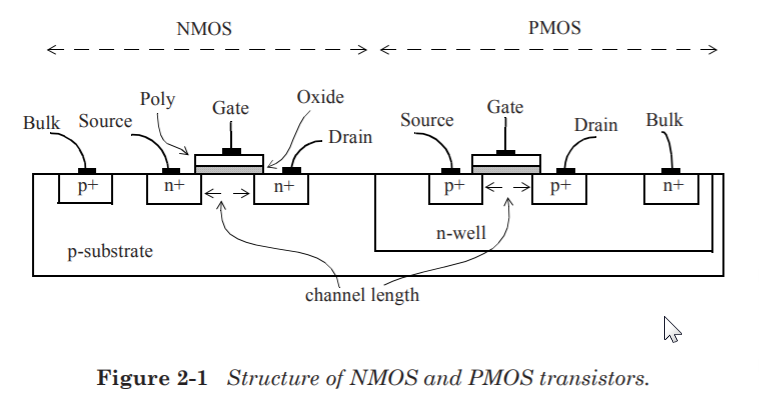

经典的与非门:AB都是逻辑1的时候noms晶体管打开,电容放电,输出电位拉低。

2.1.3标准单元

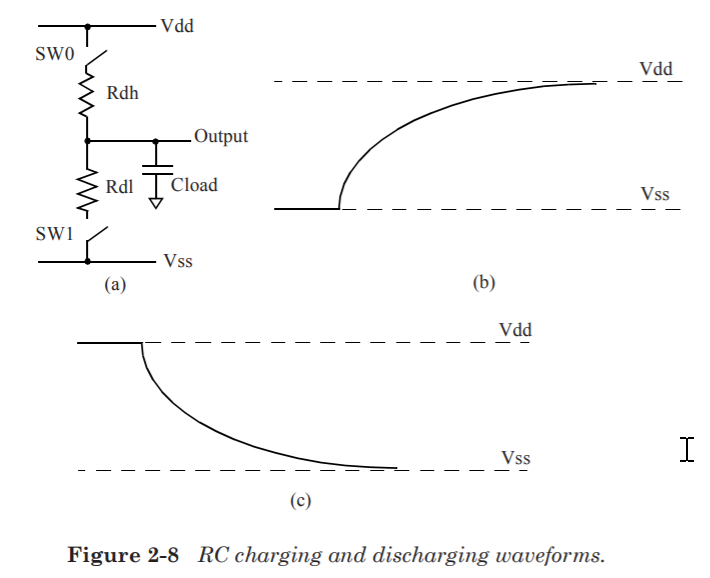

反复强调的一句话:对于所有的数字cmos单元,当输入处于稳定的逻辑状态时,不存在从电源中提取的电流(除了泄露电流)。因此电路大部分功耗与设计中的开关活动有关,是由于设计中cmos单元输入的充放电引起的。

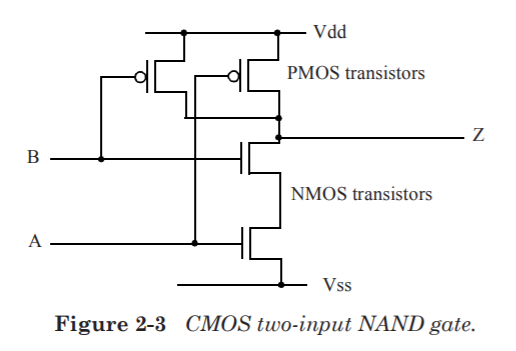

对于逻辑1、逻辑0的界定:

2.2 cmos单元模型

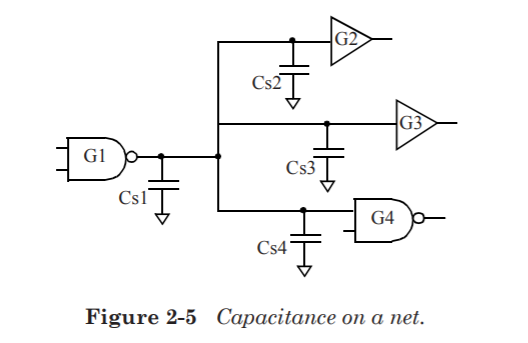

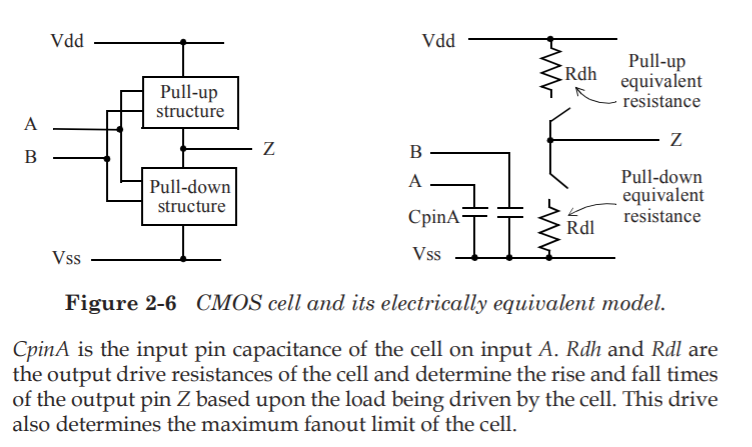

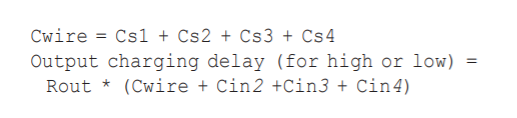

扇出:单元引脚上的总电容 = 所驱动单元的所有输入电容之和 + 连线上所有线段的电容 + 驱动单元本身输出电容。

电容负载会影响G1的时序。

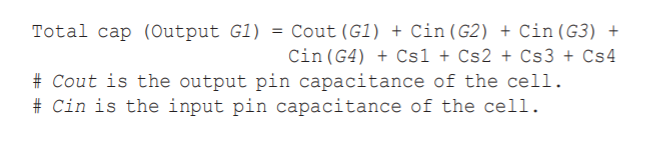

单元的开关速度取决于输出负载电容充电放电的速度。注意:沟道会对输出充放电路径构成阻力。充放电路径上的电阻是决定cmos开关速度的主要因素。电阻的倒数就是驱动能力。一定沟道长度下,沟道宽度越大,电阻越小,驱动能力越强。

再次总结一下:单元能够承受的最大电容负载决定了最大扇出数,即可以驱动多少其他单元,较高的输出驱动对应着较低的输出上拉下拉电阻,这允许输出引脚为更大的负载电容充电和放电。

对单元的输出输入进行建模:

和2.5对比看:

Rout是Rdh或者Rdl

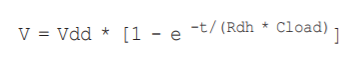

2.3 开关波形

输出端电压公式(0->1):

图a 上拉下拉电阻同时导通

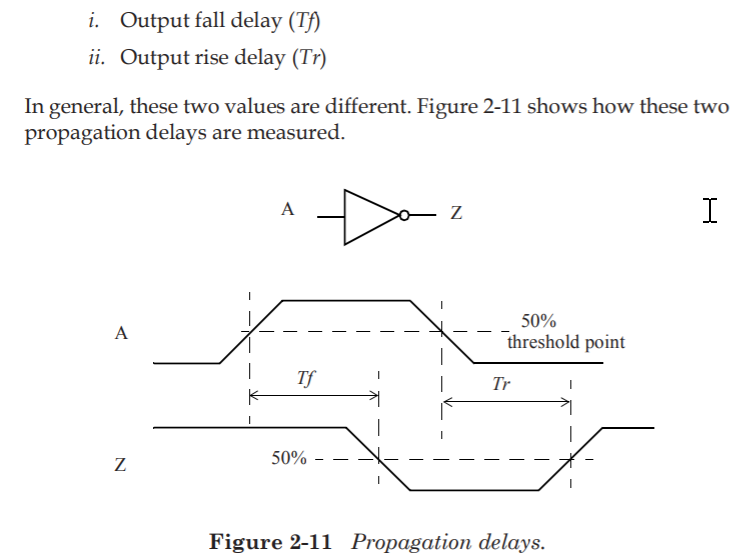

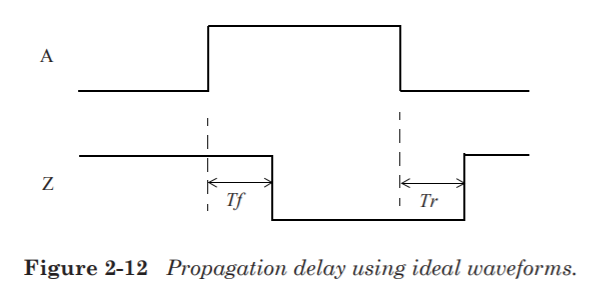

2.4 传播延时

以cmos反相器单元为例,以50%为阈值点

下图为理想情况:

2.5 波形翻转

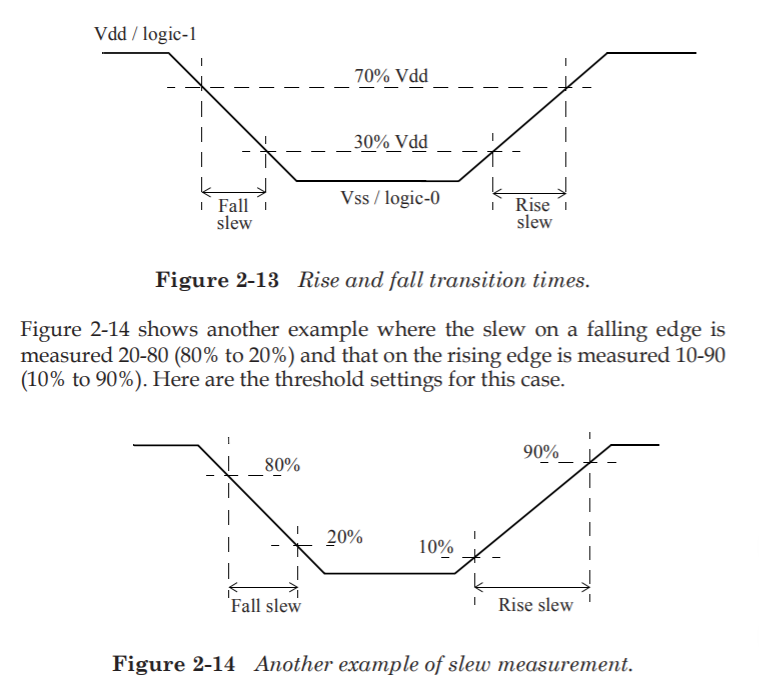

翻转阈值举例:

2.6 信号偏斜

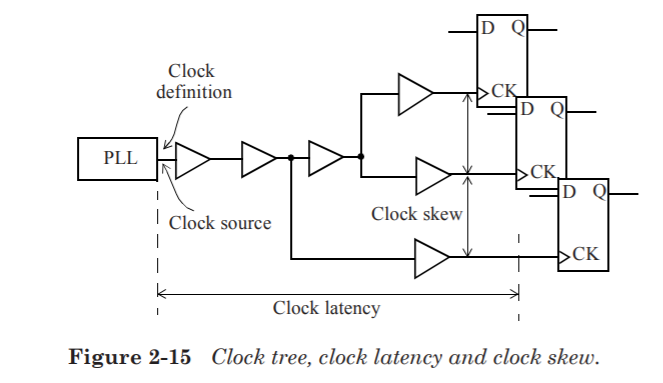

skew偏斜:指的是两个或多个信号之间的时序差异,数据或者时钟。

如果clock skew = 50ps,意味着最长和最短时钟路径之间的延迟差异是50ps。

clock latency时钟延迟:时钟源点到终点的总时间。

为时钟树建模:

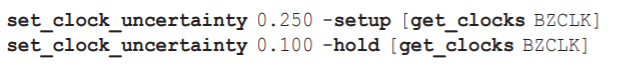

时钟不确定性 包含时钟抖动jitter和用于时序验证的额外边距。

最好把它看做最后松懈计算的一种抵消。

2.7 时序弧与unateness

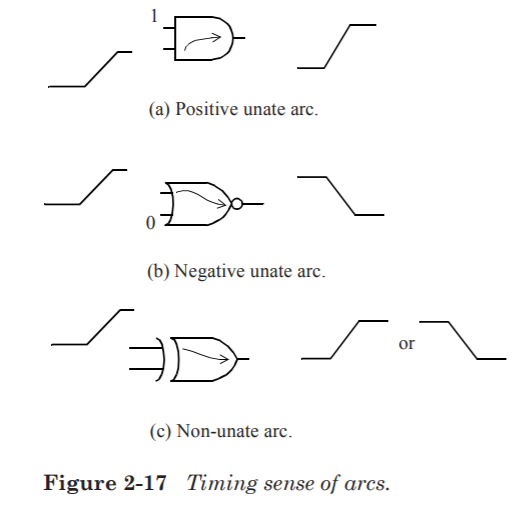

每一个单元都有多个时序弧;从每个输入到输出。

正时序弧:如果输入上升引起输出上升或不变,输入下降引起输出下降或不变。

负时序弧:如果输入上升引起输出下降或不变,输入下降引起输出上升或不变。

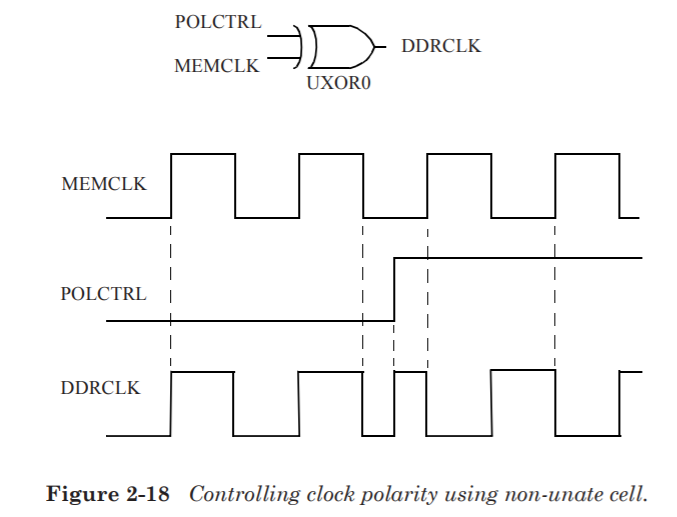

non-unate:输出转换不能仅仅由输入的变化方向来确定,还取决于其他输入的状态。例如异或门。

如图所示:

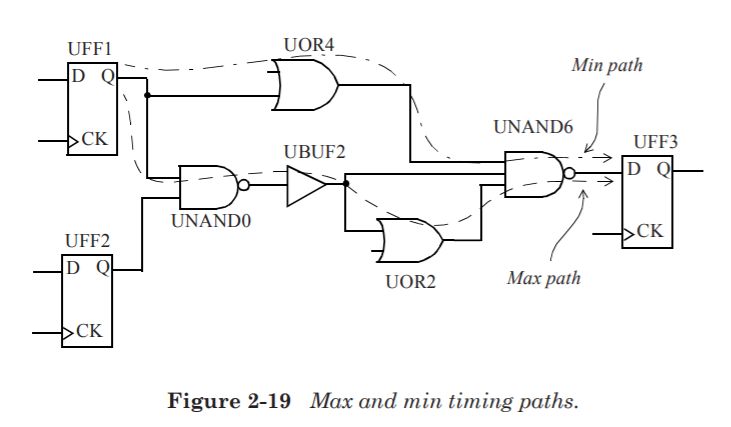

最大路径叫late path,最小路径early path

2.8最大最小时序路径

逻辑通过逻辑路径的总延时称为路径延时。通常,逻辑可以通过多条路径传播到所需的目标点,实际路径取决于沿逻辑路径的其他输入状态。

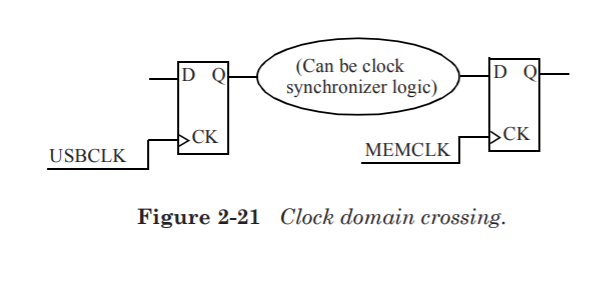

2.9时钟域

同步设计中,时钟域可能不止一个。

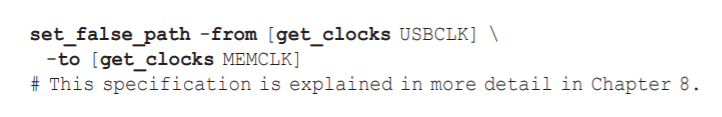

时钟域是关联的还是独立的?取决于是否有“从一个时钟域开始并在另一个时钟域中结束的数据路径”,如果是关联的,需要判断路径的真假。

留坑

2.10工作环境

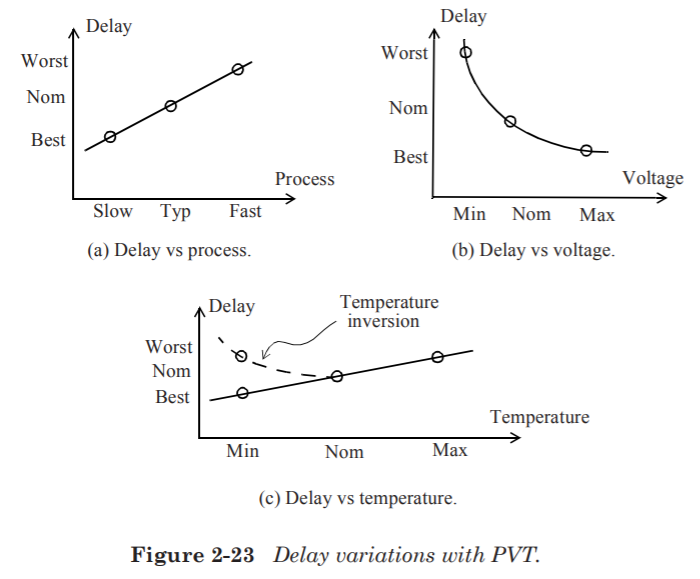

工艺电压温度 对延时的影响:

功率分析下的工作环境:

最大泄露电流:工艺-快(面积大),温度高,电压高。对应着最大的动态功耗。

典型泄露电流:工艺典型,温度高,电压正常。正常工作中,功耗大,温度随之升高的情况。

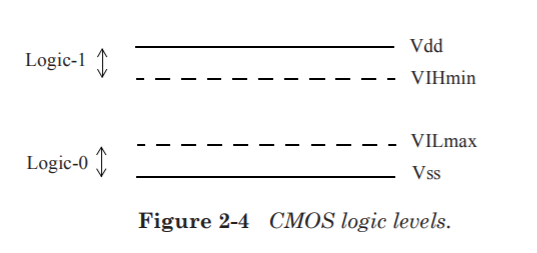

sta中可以用如下命令指定工作环境:按工艺库中提供的信息来。