XILINX FPGA 1/4/8通道PCIe DMA控制器IP,高性能版本IP介绍应用

Multi-Channel PCIe QDMA&RDMA IP

1 介绍

基于PCI Express Integrated Block,Multi-Channel PCIe QDMA Subsystem实现了使用DMA地址队列的独立多通道、高性能Continous或Scather Gather DMA,提供FIFO/AXI4-Stream用户接口。

基于PCI Express Integrated Block,Multi-Channel PCIe RDMA Subsystem实现了使用DMA Ring缓冲的独立多通道、高性能/超低延时/超低抖动Continous Ring DMA,提供FIFO/AXI4-Stream用户接口。

1.1 特性

- 支持Ultrascale+,Ultrascale,7 Series的PCI Express Integrated Block

- 支持64,128,256,512-bit数据路径

- 64-bit源地址,目的地址,和描述符地址

- 多达8个独立的host-to-card(H2C/Read)数据通道或H2C DMA

- 多达8个独立的card-to-host(C2H/Write)数据通道或C2H DMA

- AXI4-Stream/FIFO用户接口(每个通道都有自己的AXI4-Stream/FIFO接口)

- 每个DMA引擎支持DMA地址队列,队列深度可达32

- 每个DMA引擎支持DMA Ring缓冲,Ring缓冲深度和个数可配置

- RDMA的超低延时和超低抖动性

- H2C DMA支持视频显示定时时序输入控制

- AXI4-Lite Master接口允许PCIe通信绕过DMA引擎

- Scather Gather描述符列表支持无限列表大小

- 每个描述符的最大传输长度为4GB

- MSI中断

- 连续描述符的块获取

- 中断或查询模式

1.2 应用

本内核体系结构支持广泛的计算和通信目标程序应用,强调性能、成本、可扩展性、功能可扩展性和关键任务可靠性。典型应用包括:

● 数据通信网络

● 电信网络

● 宽带有线和无线应用

● 网络接口卡

● 用于各种应用程序的服务器add-in card

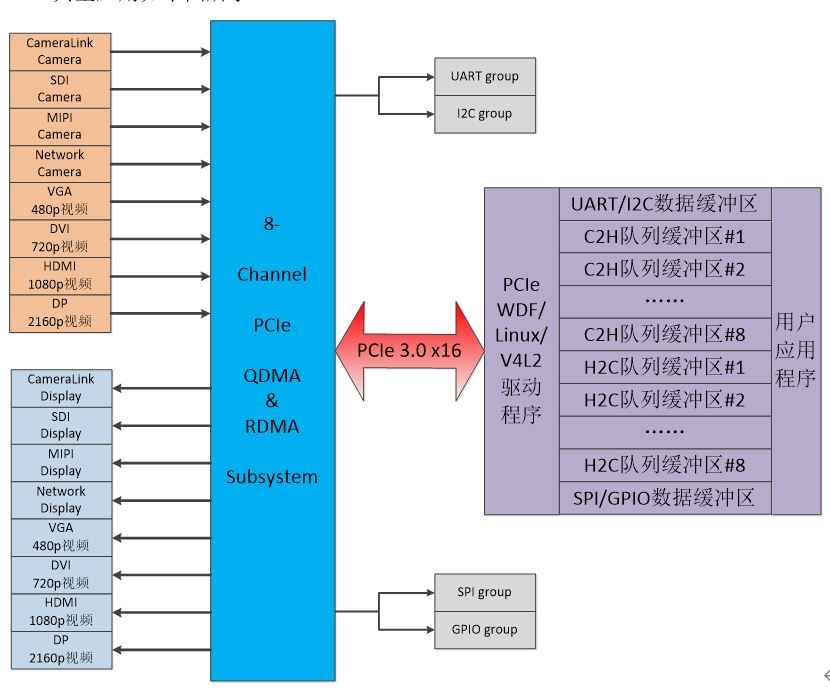

典型应用如下图所示:

图 1 Multi-Channel PCIe QDMA&RDMA Subsystem典型应用:8通道视频采集和视频显示

2 概述

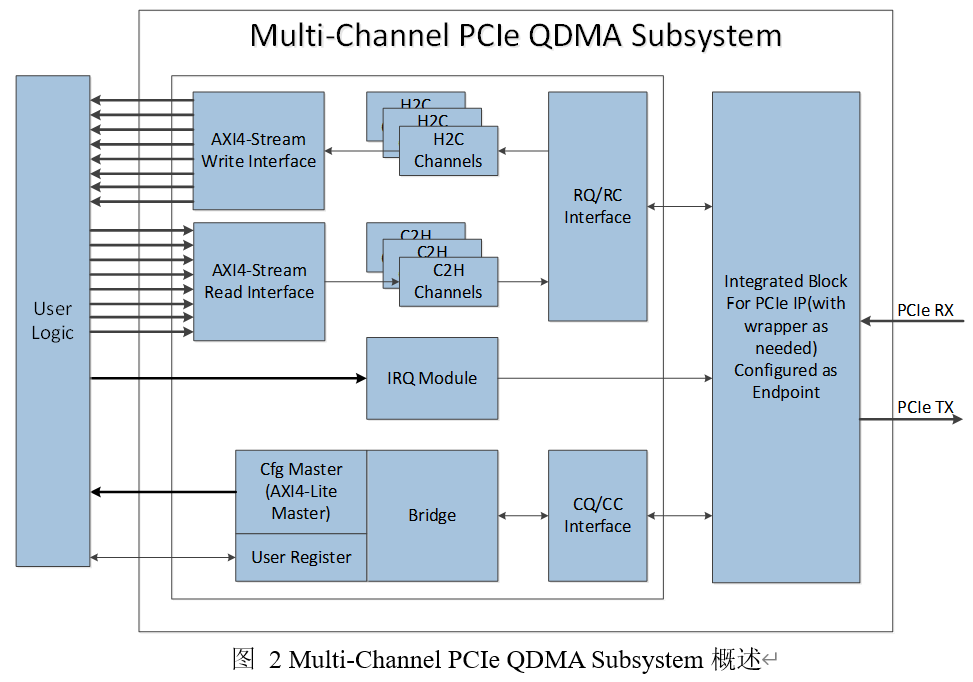

Multi-Channel PCIe QDMA&RDMA Subsystem作为一个高性能DMA数据搬移器,内核通过AXI4-Stream/FIFO接口直接连接RTL逻辑。使用提供的字符驱动程序,AXI4-Stream/FIFO接口可用于PCIe地址空间和AXI地址空间之间的高性能数据搬移。除了基本的DMA功能,DMA支持多达8个独立的upstream和downstream通道,每个通道支持深度为32的DMA地址队列,以及深度和个数可配置的DMA Ring缓冲,另外还允许PCIe通信绕过DMA引擎。

图 2 Multi-Channel PCIe QDMA&RDMA Subsystem概述

2.1 特性概要

基于描述符提供的信息:源地址,目的地址和传输数据长度,Multi-Channel PCIe QDMA&RDMA Subsystem实现Host存储器和PCIe DMA子系统之间的数据搬移。这些DMA可以同时是Host to Card(H2C)和Card to Host(C2H)传输。每个DMA通道对应各自的AX4-Stream/FIFO接口,DMA从Host存储器获取并解析描述符链表,基于描述符链表信息完成自己通道的数据传输,然后使用MSI中断发出描述符完成或错误的信令。内核也提供多达16个输出到Host的用户中断信号。

主机可以通过以下2个接口访问用户逻辑:

- AXI4-Lite Master配置接口:这个接口是一个固定的32-bit端口,用于对性能要求不高的用户配置和状态寄存器的访问

- User Register:这个接口是多个32-bit向量信号和1-bit信号,这些信号来自对应DMA通道数据搬移过程中产生的控制或状态信号

3 产品规格

结合Integrated Block for PCI Express IP,Multi-Channel PCIe QDMA&RDMA Subsystem为PCIe提供了一个高性能的DMA解决方案。

3.1 性能

Endpoint配置参数:

- Max Payload Size=256-byte

- Max Read Request Size=512-byte

- DMA Transfer Length = 4MB

C2H & H2C DMA性能:

- PCIe 3.0 x16,C2H DMA和H2C DMA速度大于13.5GB/s

- PCIe 3.0 x8,C2H DMA和H2C DMA速度大于7GB/s

- PCIe 2.0 x8,C2H DMA和H2C DMA速度大于3.6GB/s

- PCIe 2.0 x4,C2H DMA和H2C DMA速度大于1.7GB/s

3.2 资源

表1 PCIe 3.0 x16 DMA Subsystem资源(8通道)

|

|

LUTs |

FFs |

BRAMs |

PCIe |

|

资源 |

44272 |

99014 |

165.5 |

1 |

表2 PCIe 3.0 x8 DMA Subsystem资源(8通道)

|

|

LUTs |

FFs |

BRAMs |

PCIe |

|

资源 |

26356 |

51523 |

93 |

1 |

表3 PCIe 2.0 x8 DMA Subsystem资源(8通道)

|

|

LUTs |

FFs |

BRAMs |

PCIe |

|

资源 |

26614 |

33766 |

70 |

1 |

表4 PCIe 2.0 x4 DMA Subsystem资源(8通道)

|

|

LUTs |

FFs |

BRAMs |

PCIe |

|

资源 |

20466 |

29623 |

106 |

1 |

表5 PCIe 3.0 x16 DMA Subsystem资源(1通道)

|

|

LUTs |

FFs |

BRAMs |

PCIe |

|

资源 |

22353 |

55492 |

37 |

1 |

表6 PCIe 3.0 x8 DMA Subsystem资源(1通道)

|

|

LUTs |

FFs |

BRAMs |

PCIe |

|

资源 |

8113 |

21656 |

17 |

1 |

表7 PCIe 2.0 x8 DMA Subsystem资源(1通道)

|

|

LUTs |

FFs |

BRAMs |

PCIe |

|

资源 |

11074 |

16221 |

10 |

1 |

表8 PCIe 2.0 x4 DMA Subsystem资源(1通道)

|

|

LUTs |

FFs |

BRAMs |

PCIe |

|

资源 |

6270 |

8588 |

29 |

1 |

3.3 驱动程序

(1) Windows WDF (Queue or Non-Queue,Ring)

(2) Linux (Queue or Non-Queue,Ring)

(3) V4L2

4 交付清单

可交付资料:

1. 详细的用户手册

2. 设计文件:源代码或网表

3. 时序约束

4. 测试或Demo工程

5. 技术支持:邮件,电话,现场,培训服务

6. Email:neteasy163z@163.com

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· DeepSeek 开源周回顾「GitHub 热点速览」

· 物流快递公司核心技术能力-地址解析分单基础技术分享

· .NET 10首个预览版发布:重大改进与新特性概览!

· AI与.NET技术实操系列(二):开始使用ML.NET

· 单线程的Redis速度为什么快?