基于FPGA的SATA3.0主机控制器IP

SATA3.0 Host Controller IP

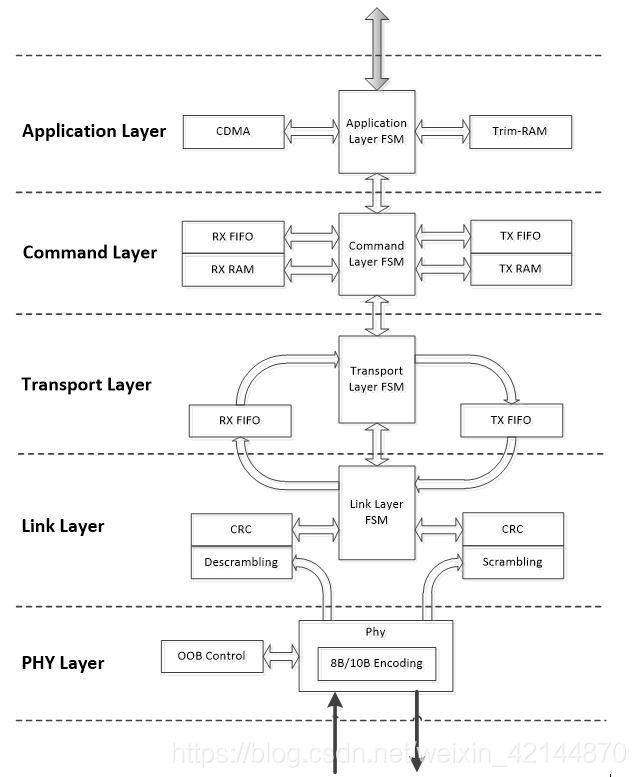

SATA3.0 Host IP不仅实现了SATA协议的PHY(物理层)、Link(链路层)和TRN(传输层),并且实现了CMD(命令层)和APP(应用层),支持1.5、3和6Gbps传输速率,和SATA规范完全兼容。

SATA3.0 Host IP给用户使用SATA存储设备提供一种高效且易于使用的接口。无需用户干预,SATA3.0 Host IP自动完成连接、诊断、识别以及初始化SATA存储设备,输出SATA设备的Identify Data Structure。SATA3.0 Host IP内置DMA控制器,用户不但可以通过IO接口访问SATA存储设备,还可以使用DMA接口高效读写SATA存储设备。

SATA3.0 Host IP不局限连接SATA存储设备的个数,即连接SATA存储设备的数量是可编程的。

内核特性:

- 与SATA 1.5Gbps、3.0Gbps以及6.0Gbps业界规范完全兼容

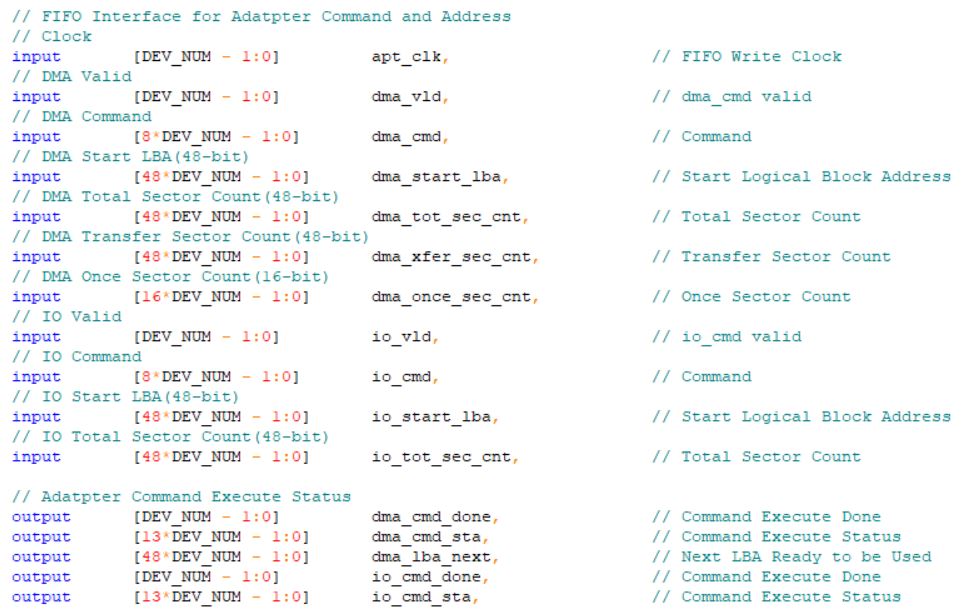

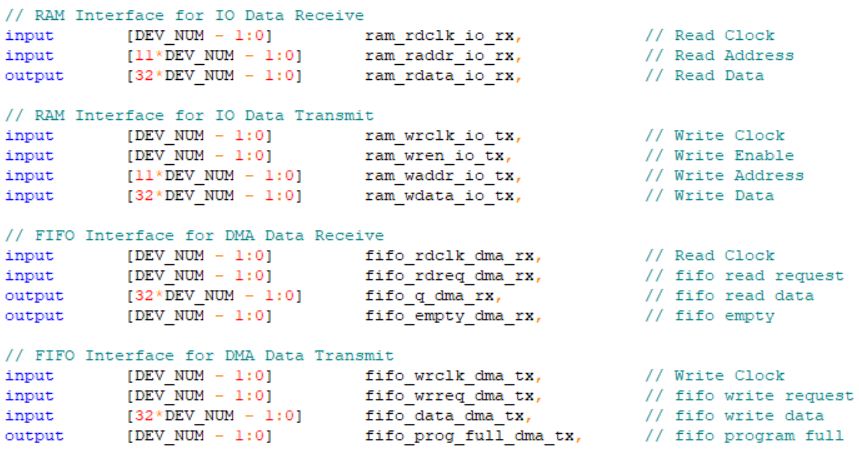

- AXI-Lite或应用寄存器(ARI)接口,同时支持IO(包括PIO和Trim)和DMA操作

- IO数据接口采用RAM设计,DMA数据接口采用AXI-Stream或FIFO设计

- 支持SerDes接口,并且SerDes接口个数可编程(即可连接的SATA存储设备的数量是可编程的,数量取决于FPGA的GT个数)

- 支持SATA存储设备带电热插拔

- 支持Xilinx器件:Spartan-6,Virtex-5,Virtex-6,Artix-7,Kintex-7,Virtex-7,Kintex Ultrascale,Kintex Ultrascale+,Virtex Ultrascale,Virtex Ultrascale+

- 易于集成的同步、可综合Verilog设计

- 通过完全验证的SATA3.0 IP

对外接口:

- AXI-Lite或应用寄存器(ARI)接口

- AXI-Stream或FIFO流式数据总线

- RAM块式数据总线

性能指标:

- SATA 3.0 Core:连续写入速度大于530MB/s,连续读取速度大于550MB/s

- SATA 2.0 Core:连续写入速度大于240MB/s,连续读取速度大于250MB/s s

1通道(连接1个SATA存储设备)SATA3.0 IP资源使用(XC7K325为例):

- LUTs:3850,FFs:4630,BRAM:16,GT:1

4通道(连接4个SATA存储设备)SATA3.0 IP资源使用(XC7K325为例):

- LUTs:15363,FFs:18468,BRAM:64,GT:4

8通道(连接8个SATA存储设备)SATA3.0 IP资源使用(XC7K325为例):

- LUTs:30763,FFs:37011,BRAM:128,GT:8

可交付资料:

- 详细的用户手册

- Design File:Post-synthesis EDIF netlist or RTL Source

- Timing and layout constraints,Test or Design Example Project

- 技术支持:邮件,电话,现场,培训服务

联系方式:

Email:neteasy163z@163.com

SATA3.0 Host IP Block Diagram

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· .NET Core 中如何实现缓存的预热?

· 从 HTTP 原因短语缺失研究 HTTP/2 和 HTTP/3 的设计差异

· AI与.NET技术实操系列:向量存储与相似性搜索在 .NET 中的实现

· 基于Microsoft.Extensions.AI核心库实现RAG应用

· Linux系列:如何用heaptrack跟踪.NET程序的非托管内存泄露

· TypeScript + Deepseek 打造卜卦网站:技术与玄学的结合

· Manus的开源复刻OpenManus初探

· .NET Core 中如何实现缓存的预热?

· 阿里巴巴 QwQ-32B真的超越了 DeepSeek R-1吗?

· 如何调用 DeepSeek 的自然语言处理 API 接口并集成到在线客服系统