随笔分类 - FPGA技术分享

分享FPGA方面的技术和经验

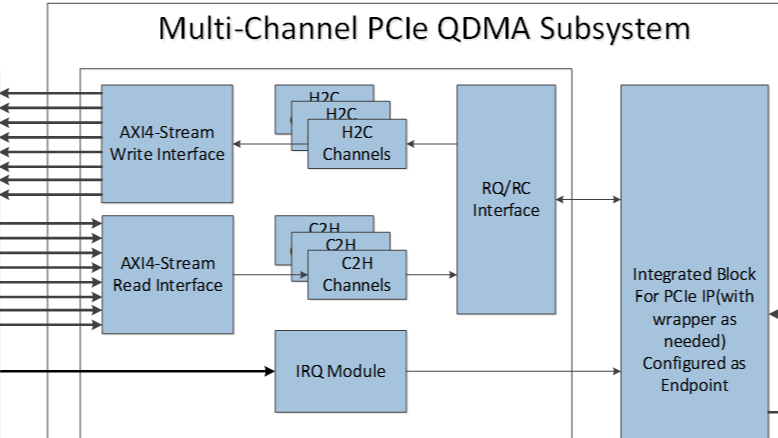

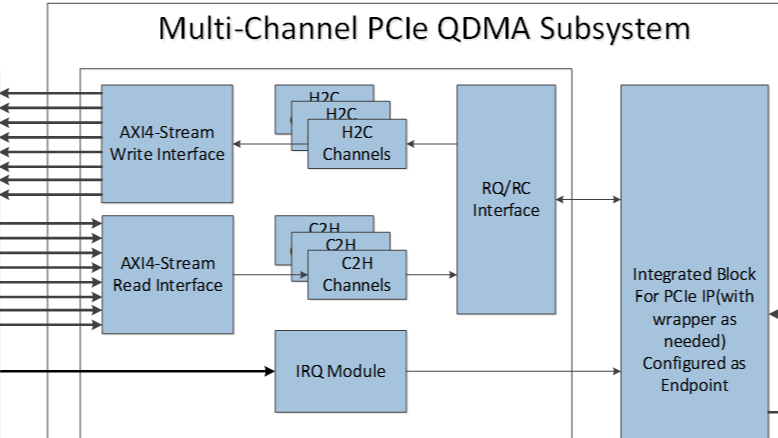

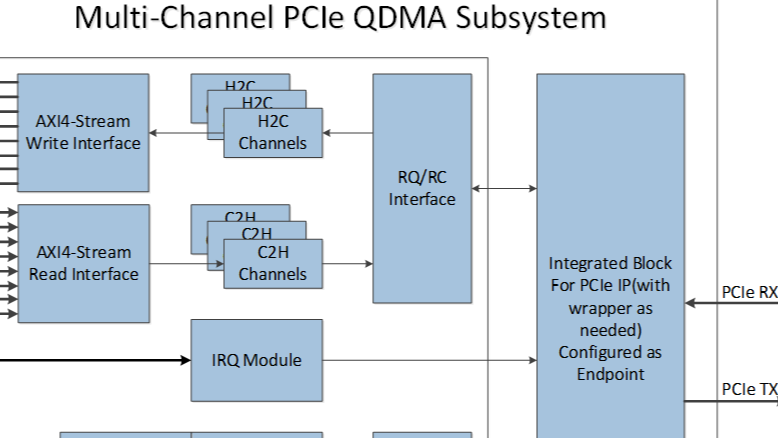

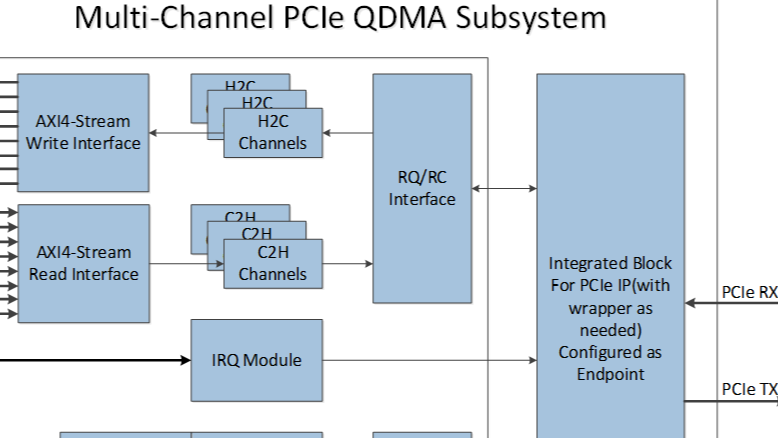

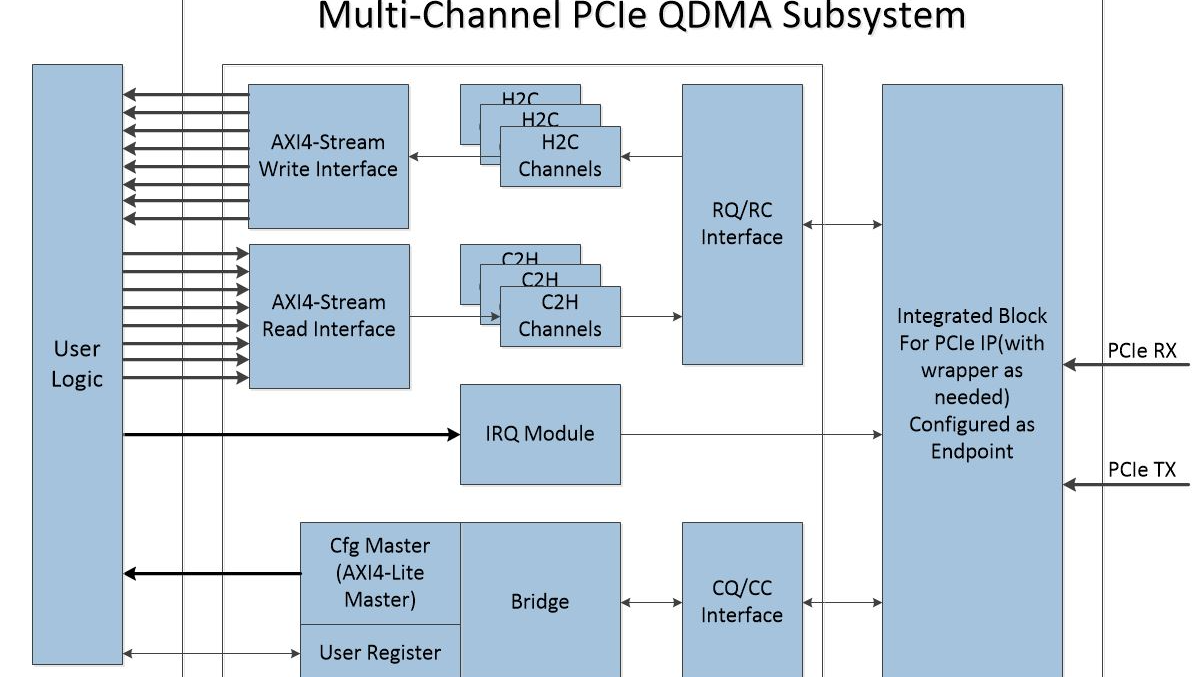

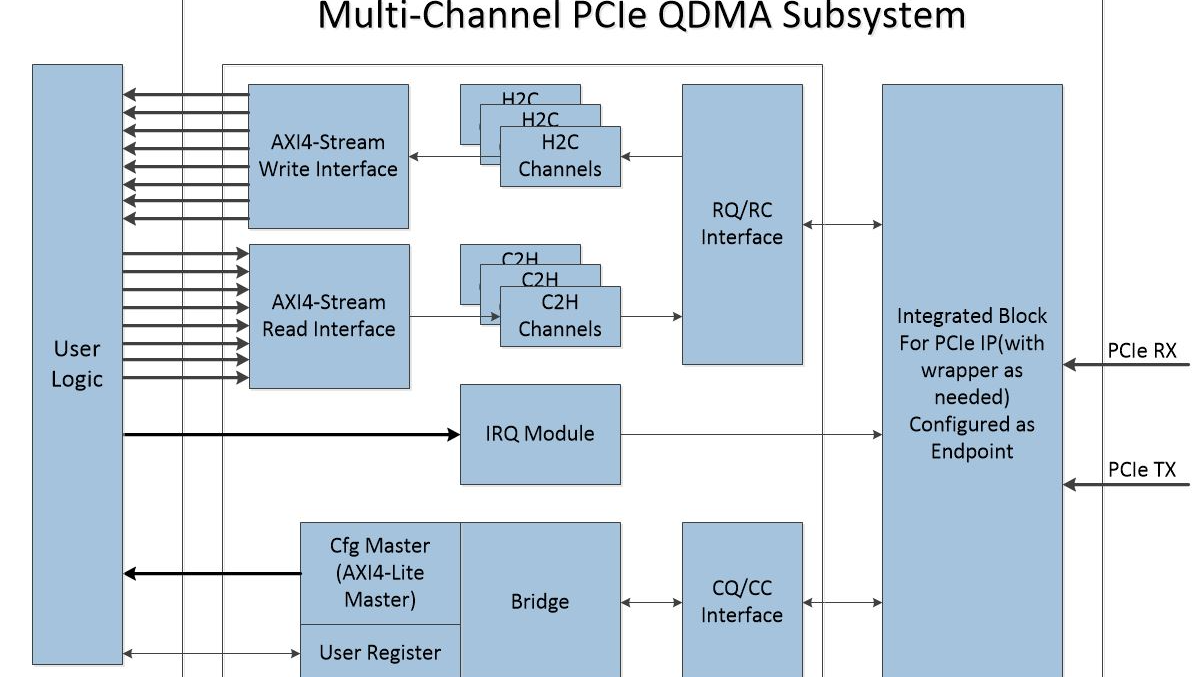

摘要: Multi-Channel PCIe QDMA&RDMA IP 1 介绍 基于PCI Express Integrated Block,Multi-Channel PCIe QDMA Subsystem实现了使用DMA地址队列的独立多通道、高性能Continous(CDMA)或Scather Gat

阅读全文

Multi-Channel PCIe QDMA&RDMA IP 1 介绍 基于PCI Express Integrated Block,Multi-Channel PCIe QDMA Subsystem实现了使用DMA地址队列的独立多通道、高性能Continous(CDMA)或Scather Gat

阅读全文

Multi-Channel PCIe QDMA&RDMA IP 1 介绍 基于PCI Express Integrated Block,Multi-Channel PCIe QDMA Subsystem实现了使用DMA地址队列的独立多通道、高性能Continous(CDMA)或Scather Gat

阅读全文

Multi-Channel PCIe QDMA&RDMA IP 1 介绍 基于PCI Express Integrated Block,Multi-Channel PCIe QDMA Subsystem实现了使用DMA地址队列的独立多通道、高性能Continous(CDMA)或Scather Gat

阅读全文

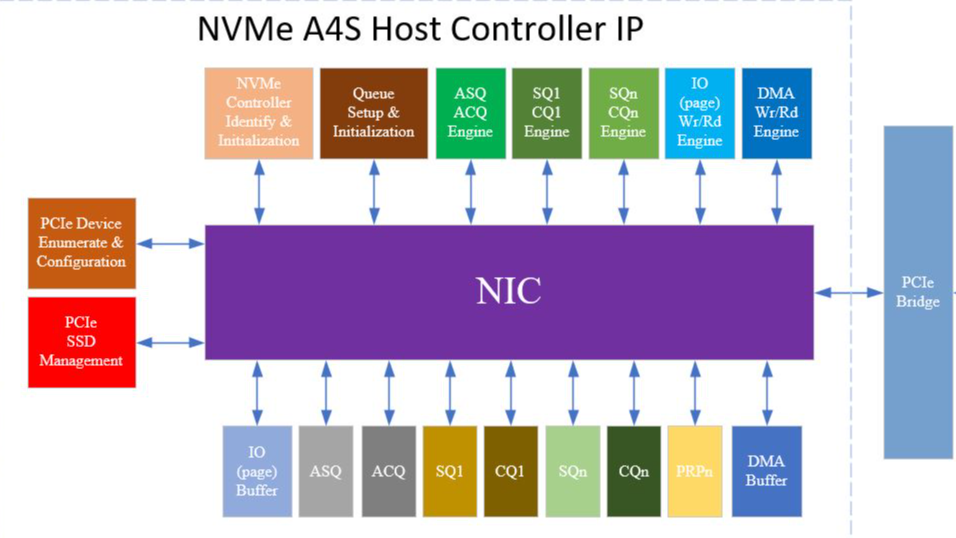

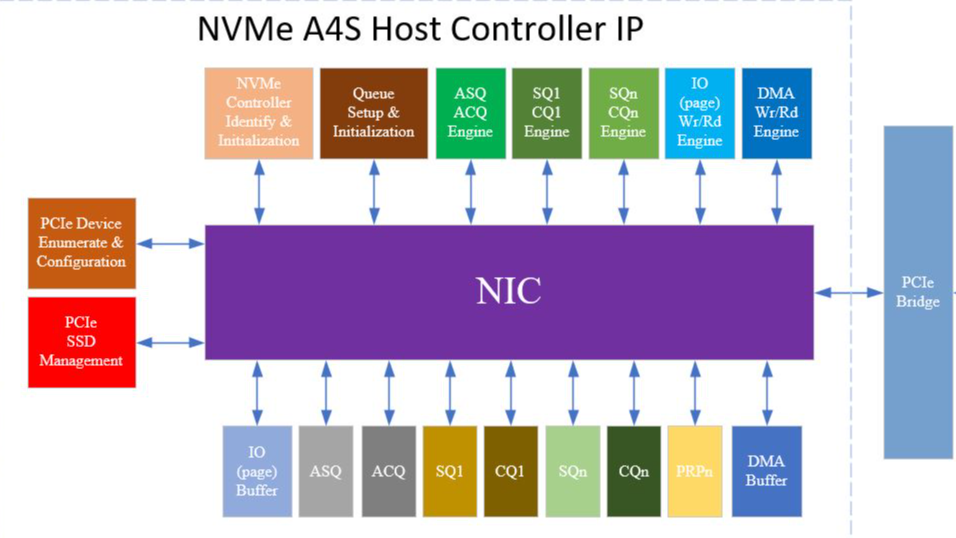

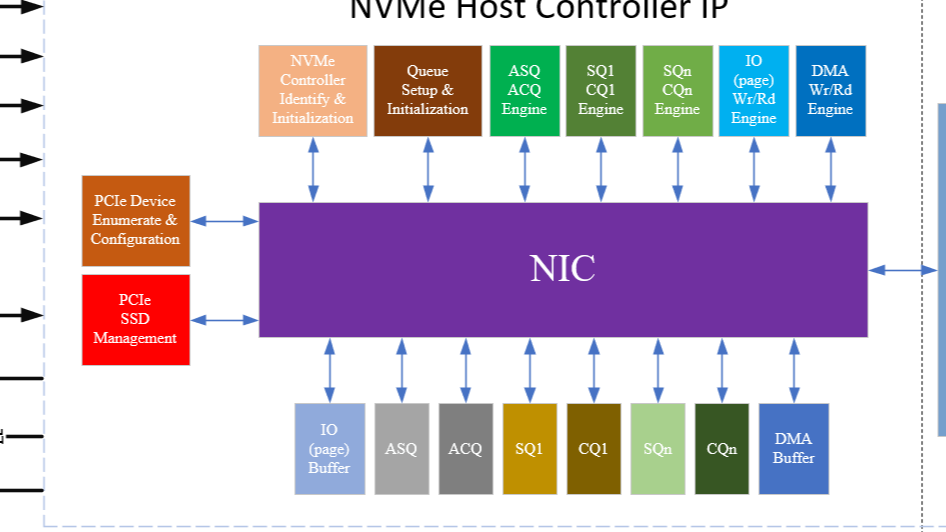

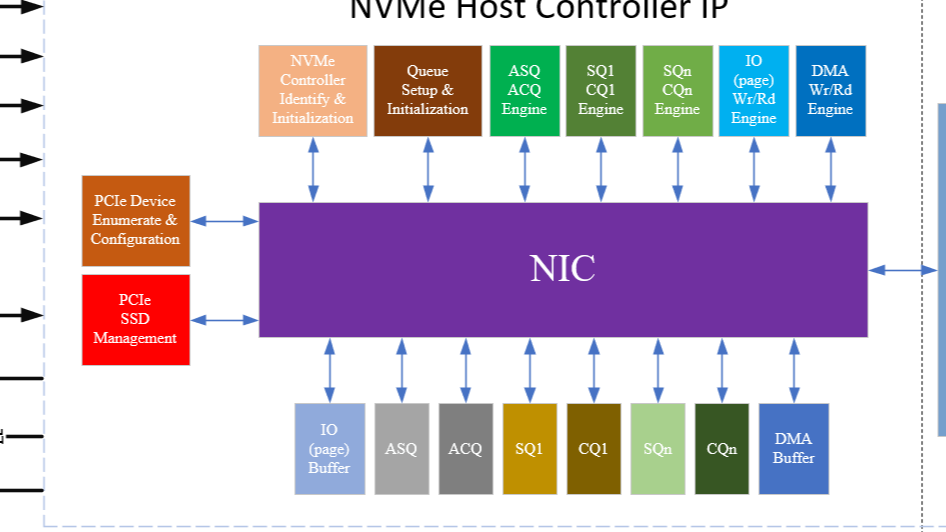

摘要: NVMe A4S Host Controller IP 1 介绍 NVMe A4S Host Controller IP可以连接高速存储PCIe SSD,无需CPU和外部存储器,自动加速处理所有的NVMe协议命令,具备独立的数据写入AXI4-Stream/FIFO接口和数据读取AXI4-Stream

阅读全文

NVMe A4S Host Controller IP 1 介绍 NVMe A4S Host Controller IP可以连接高速存储PCIe SSD,无需CPU和外部存储器,自动加速处理所有的NVMe协议命令,具备独立的数据写入AXI4-Stream/FIFO接口和数据读取AXI4-Stream

阅读全文

NVMe A4S Host Controller IP 1 介绍 NVMe A4S Host Controller IP可以连接高速存储PCIe SSD,无需CPU和外部存储器,自动加速处理所有的NVMe协议命令,具备独立的数据写入AXI4-Stream/FIFO接口和数据读取AXI4-Stream

阅读全文

NVMe A4S Host Controller IP 1 介绍 NVMe A4S Host Controller IP可以连接高速存储PCIe SSD,无需CPU和外部存储器,自动加速处理所有的NVMe协议命令,具备独立的数据写入AXI4-Stream/FIFO接口和数据读取AXI4-Stream

阅读全文

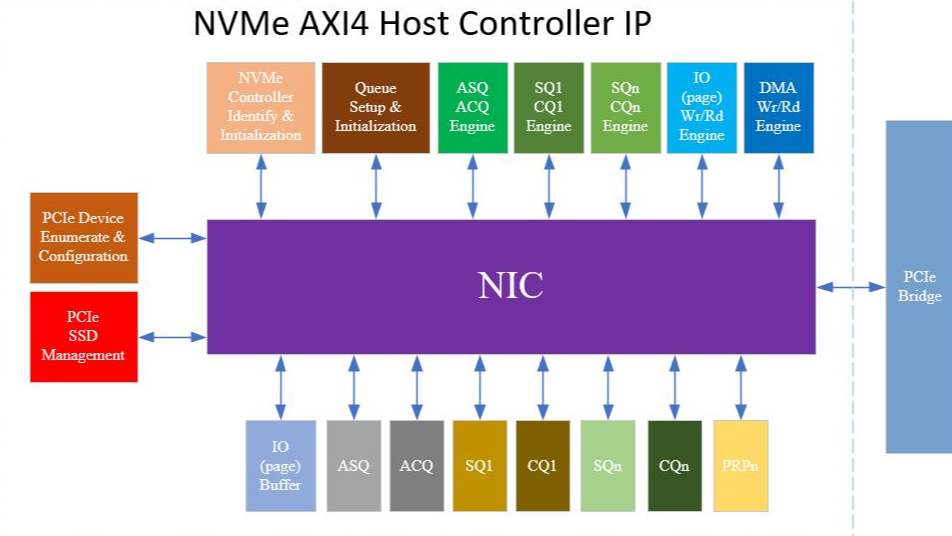

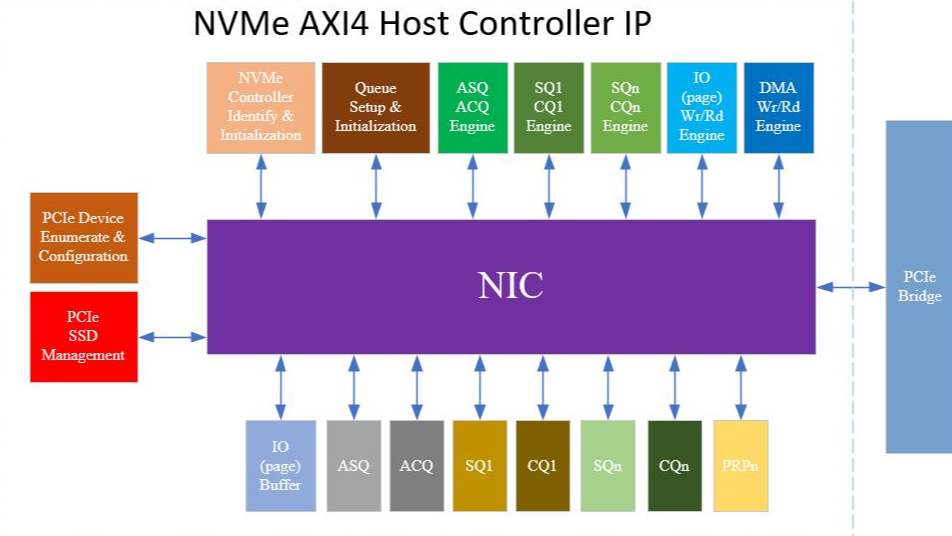

摘要: NVMe AXI4 Host Controller IP可以连接高速存储PCIe SSD,无需CPU,自动加速处理所有的NVMe协议命令,具备独立的数据写入和读取AXI4接口,不但适用高性能、顺序访问的应用,也适用于随机访问的应用,同时结合外部存储器(比如DDR),使得Host端的数据访问管理更加灵活。

阅读全文

NVMe AXI4 Host Controller IP可以连接高速存储PCIe SSD,无需CPU,自动加速处理所有的NVMe协议命令,具备独立的数据写入和读取AXI4接口,不但适用高性能、顺序访问的应用,也适用于随机访问的应用,同时结合外部存储器(比如DDR),使得Host端的数据访问管理更加灵活。

阅读全文

NVMe AXI4 Host Controller IP可以连接高速存储PCIe SSD,无需CPU,自动加速处理所有的NVMe协议命令,具备独立的数据写入和读取AXI4接口,不但适用高性能、顺序访问的应用,也适用于随机访问的应用,同时结合外部存储器(比如DDR),使得Host端的数据访问管理更加灵活。

阅读全文

NVMe AXI4 Host Controller IP可以连接高速存储PCIe SSD,无需CPU,自动加速处理所有的NVMe协议命令,具备独立的数据写入和读取AXI4接口,不但适用高性能、顺序访问的应用,也适用于随机访问的应用,同时结合外部存储器(比如DDR),使得Host端的数据访问管理更加灵活。

阅读全文

摘要: Multi-Channel PCIe QDMA&RDMA IP 1 介绍 基于PCI Express Integrated Block,Multi-Channel PCIe QDMA Subsystem实现了使用DMA地址队列的独立多通道、高性能Continous或Scather Gather DM

阅读全文

Multi-Channel PCIe QDMA&RDMA IP 1 介绍 基于PCI Express Integrated Block,Multi-Channel PCIe QDMA Subsystem实现了使用DMA地址队列的独立多通道、高性能Continous或Scather Gather DM

阅读全文

Multi-Channel PCIe QDMA&RDMA IP 1 介绍 基于PCI Express Integrated Block,Multi-Channel PCIe QDMA Subsystem实现了使用DMA地址队列的独立多通道、高性能Continous或Scather Gather DM

阅读全文

Multi-Channel PCIe QDMA&RDMA IP 1 介绍 基于PCI Express Integrated Block,Multi-Channel PCIe QDMA Subsystem实现了使用DMA地址队列的独立多通道、高性能Continous或Scather Gather DM

阅读全文

摘要: NVMe Host Controller IP可以连接高速存储PCIe SSD,无需CPU和外部存储器,自动加速处理所有的NVMe协议命令,具备独立的数据写入AXI4-Stream/FIFO接口和数据读取AXI4-Stream/FIFO接口,非常适合于超高容量和超高性能的应用。此外,NVMe Host Controller IP支持RAID存储,从而可实现更高存储性能和存储容量。

阅读全文

NVMe Host Controller IP可以连接高速存储PCIe SSD,无需CPU和外部存储器,自动加速处理所有的NVMe协议命令,具备独立的数据写入AXI4-Stream/FIFO接口和数据读取AXI4-Stream/FIFO接口,非常适合于超高容量和超高性能的应用。此外,NVMe Host Controller IP支持RAID存储,从而可实现更高存储性能和存储容量。

阅读全文

NVMe Host Controller IP可以连接高速存储PCIe SSD,无需CPU和外部存储器,自动加速处理所有的NVMe协议命令,具备独立的数据写入AXI4-Stream/FIFO接口和数据读取AXI4-Stream/FIFO接口,非常适合于超高容量和超高性能的应用。此外,NVMe Host Controller IP支持RAID存储,从而可实现更高存储性能和存储容量。

阅读全文

NVMe Host Controller IP可以连接高速存储PCIe SSD,无需CPU和外部存储器,自动加速处理所有的NVMe协议命令,具备独立的数据写入AXI4-Stream/FIFO接口和数据读取AXI4-Stream/FIFO接口,非常适合于超高容量和超高性能的应用。此外,NVMe Host Controller IP支持RAID存储,从而可实现更高存储性能和存储容量。

阅读全文

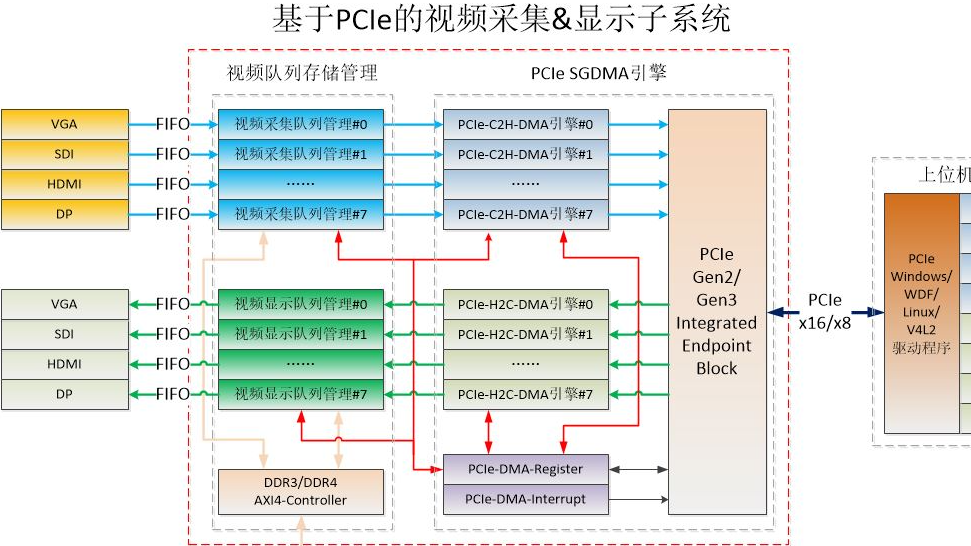

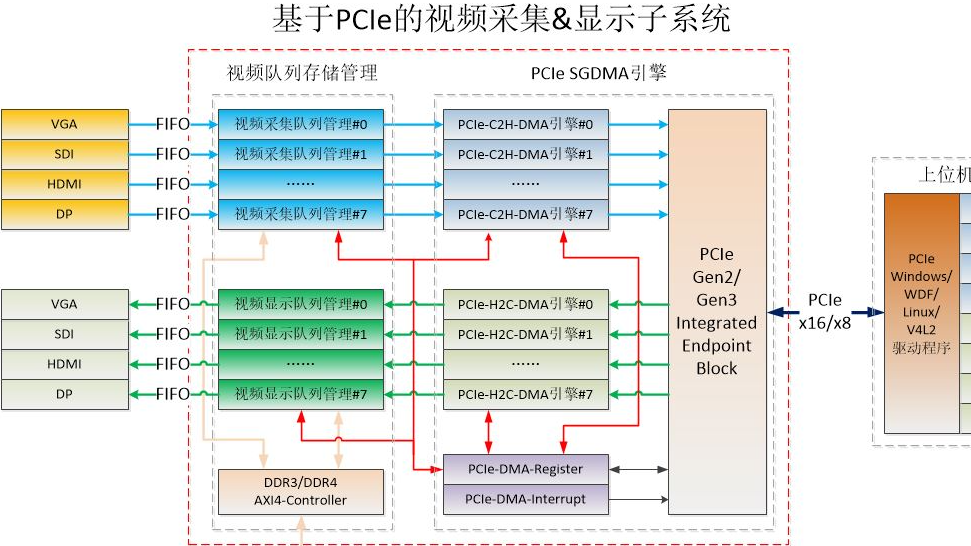

摘要: 基于PCIe的多路视频采集与显示子系统 1 概述 视频采集与显示子系统可以实时采集多路视频信号,并存储到视频采集队列中,借助高效的硬实时视频帧出入队列管理和PCIe C2H DMA引擎,将采集到的视频帧实时传递到上位机采集缓冲区。 视频采集与显示子系统使用高效的PCIe H2C DMA引擎读取上位机

阅读全文

基于PCIe的多路视频采集与显示子系统 1 概述 视频采集与显示子系统可以实时采集多路视频信号,并存储到视频采集队列中,借助高效的硬实时视频帧出入队列管理和PCIe C2H DMA引擎,将采集到的视频帧实时传递到上位机采集缓冲区。 视频采集与显示子系统使用高效的PCIe H2C DMA引擎读取上位机

阅读全文

基于PCIe的多路视频采集与显示子系统 1 概述 视频采集与显示子系统可以实时采集多路视频信号,并存储到视频采集队列中,借助高效的硬实时视频帧出入队列管理和PCIe C2H DMA引擎,将采集到的视频帧实时传递到上位机采集缓冲区。 视频采集与显示子系统使用高效的PCIe H2C DMA引擎读取上位机

阅读全文

基于PCIe的多路视频采集与显示子系统 1 概述 视频采集与显示子系统可以实时采集多路视频信号,并存储到视频采集队列中,借助高效的硬实时视频帧出入队列管理和PCIe C2H DMA引擎,将采集到的视频帧实时传递到上位机采集缓冲区。 视频采集与显示子系统使用高效的PCIe H2C DMA引擎读取上位机

阅读全文

摘要: 基于PCI Express Integrated Block,Multi-Channel PCIe QDMA Subsystem实现了基于DMA地址队列的高性能Continous或Scather Gather DMA,提供FIFO/AXI4-Stream用户接口。

阅读全文

基于PCI Express Integrated Block,Multi-Channel PCIe QDMA Subsystem实现了基于DMA地址队列的高性能Continous或Scather Gather DMA,提供FIFO/AXI4-Stream用户接口。

阅读全文

基于PCI Express Integrated Block,Multi-Channel PCIe QDMA Subsystem实现了基于DMA地址队列的高性能Continous或Scather Gather DMA,提供FIFO/AXI4-Stream用户接口。

阅读全文

基于PCI Express Integrated Block,Multi-Channel PCIe QDMA Subsystem实现了基于DMA地址队列的高性能Continous或Scather Gather DMA,提供FIFO/AXI4-Stream用户接口。

阅读全文

摘要:基于Camera Link和PCIe DMA的多通道视频采集和显示系统 在主机端PCIe驱动的控制和调度下,视频采集与显示系统可以同时完成对多个Camera Link接口视频采集以及Camera Link接口视频回放驱动工作,既可采用行缓存机制(无需帧缓存,无需DDR),也可采用帧缓存机制(使用DD

阅读全文

摘要:基于JESD204B和PCIe DMA的多通道数据采集和回放系统 在主机端PCIe驱动的控制和调度下,数据采集与回放系统可以同时完成对多个JESD204B接口AD数据的采集以及JESD204B接口DA回放驱动工作,既可采用行缓存机制(无需帧缓存,无需DDR),也可采用帧缓存机制(需要DDR),使用P

阅读全文

摘要:SATA3.0 Host Controller IP SATA3.0 Host IP不仅实现了SATA协议的PHY(物理层)、Link(链路层)和TRN(传输层),并且实现了CMD(命令层)和APP(应用层),支持1.5、3和6Gbps传输速率,和SATA规范完全兼容。 SATA3.0 Host I

阅读全文

摘要:Programmable AES Encryption/ Decryption IP 可编程AES加解密IP 可编程AES加解密IP提供了加解密算法功能,兼容美国国家标准与技术研究院(NIST)发布的高级加密标准(AES):FIPS PUB 197。结合FIPS 197分组加密算法,可编程AES加解

阅读全文

摘要:LZOAccel-D LZO Data Decompression Core/无损数据解压缩IP Core LZOAccel-D是一个无损数据解压缩引擎的FPGA硬件实现,兼容LZO 2.10标准。 Core接收压缩的输入数据块,产生解压缩后的数据块。Core分析数据块的头和尾,检查输入数据块的错误

阅读全文

摘要:LZOAccel-C LZO Data Compression Core/无损数据压缩IP Core LZOAccel-C是一个无损数据压缩引擎的FPGA硬件实现,兼容LZO 2.10标准。 Core接收未压缩的输入数据块,产生压缩后的数据块。Core使用合适的头和尾封装了压缩后的数据载荷,所以用户

阅读全文

摘要:基于PCIe DMA的多通道数据采集和回放IP 在主机端PCIe驱动的控制和调度下,数据采集与回放IP Core可以同时完成对多个通道数据的采集以及回放驱动工作,既可采用行缓存机制(无需帧缓存,无需DDR),也可采用帧缓存机制(需要DDR),使用PCIe接口和主机进行数据的传输,设备端内嵌多通道DM

阅读全文

摘要:基于PCIe DMA的8通道视频采集&显示IP,兼容V4L2 Video Capture&Display IP for V4L2 在主机端视频设备内核驱动V4L2 的控制和调度下,Video Capture&Display IP Core可以同时完成对8个视频通道数据的采集以及8个视频通道数据的显示

阅读全文