关于STM32Fx部分引脚不可以正常输出高低电平的解决办法(不可以正常使用)

一、概述

在一次电路版测试中,发现stm32的部分引脚不可以正常的输出高低电平,刚开始以为是板子没有焊接好所以导致的经过多次的测试,发现电路版没问题。当时就想不清楚了,后面就问学长,还有实验室的学长一起测试。刚开始我们经过测试,认为是SCL的问题,认为在某个地方该引脚被占用了,导致引脚冲突后面就一直在程序上面早关于SPI在了里。因为我们怀疑是因为该引脚是SPI的SCL的引脚所以在程序的某地方开启了SPI,所以导致引脚冲突导致不可以正常使用。经过后面的检查和网上早了一些相关的资料,发现并不是我认为的SPI的SCL导致的问题。在网上突然发现PB3、PB4、PA15、PA14、PA15这几个引脚默认被 JTAG 调试时使用,所以直接使用这个几个引脚作为输出引脚是不可以的。

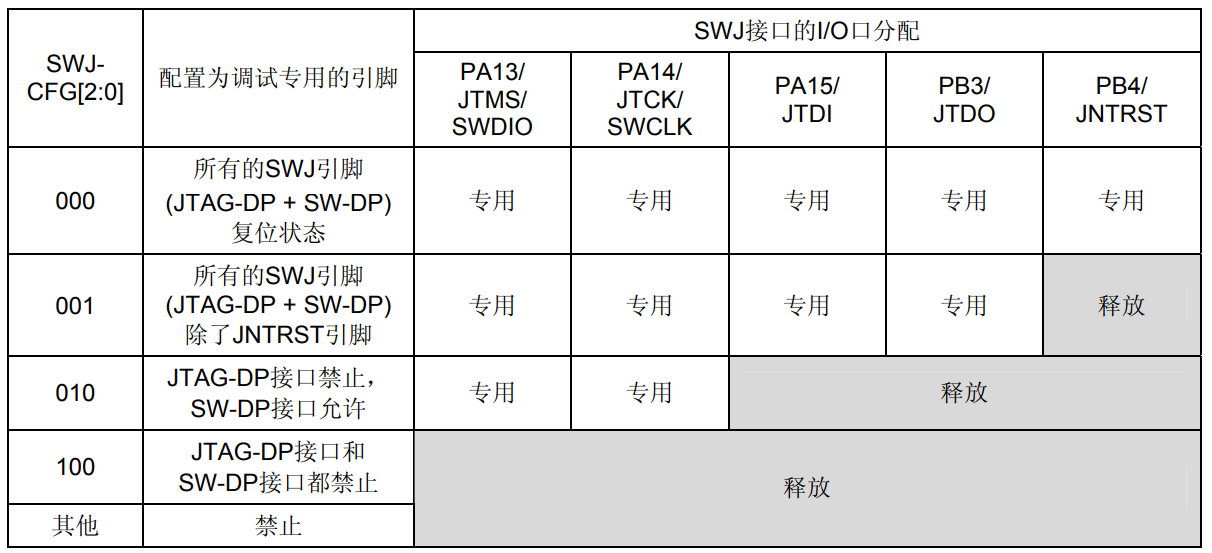

二、SWJ-DP脚分配

下图就是关于这几个引脚相关的配置问题

开始我使用的是PB3、PB4发现不可以正常使用通过上面的图片不难看出来,在默认情况下PB3、PB4、PA15、PA14、PA15这几个引脚上后都有默认的功能。所以导致我们使用他们作为普通GPIO使用的时候不可以正常使用。所以我们如果要正常使用他们只需要在开启时钟后关闭该默认功能。

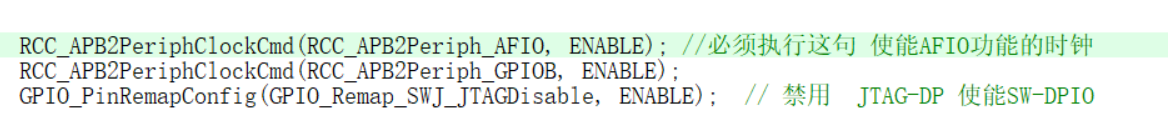

具体方法如下面

//首先开启AFIO时钟

RCC_APB2Per iphClockCmd(RCC_APB2Per iph_AFIO,ENABLE);

//然后关闭JTAG保留SWD的功能

GPIO_PINRemapConfyg(GPIO_Remap_SWJ_JTAGDisable,ENABLE);

这样就可以解决了。