SignalTap导致PCIe Read/Write卡死

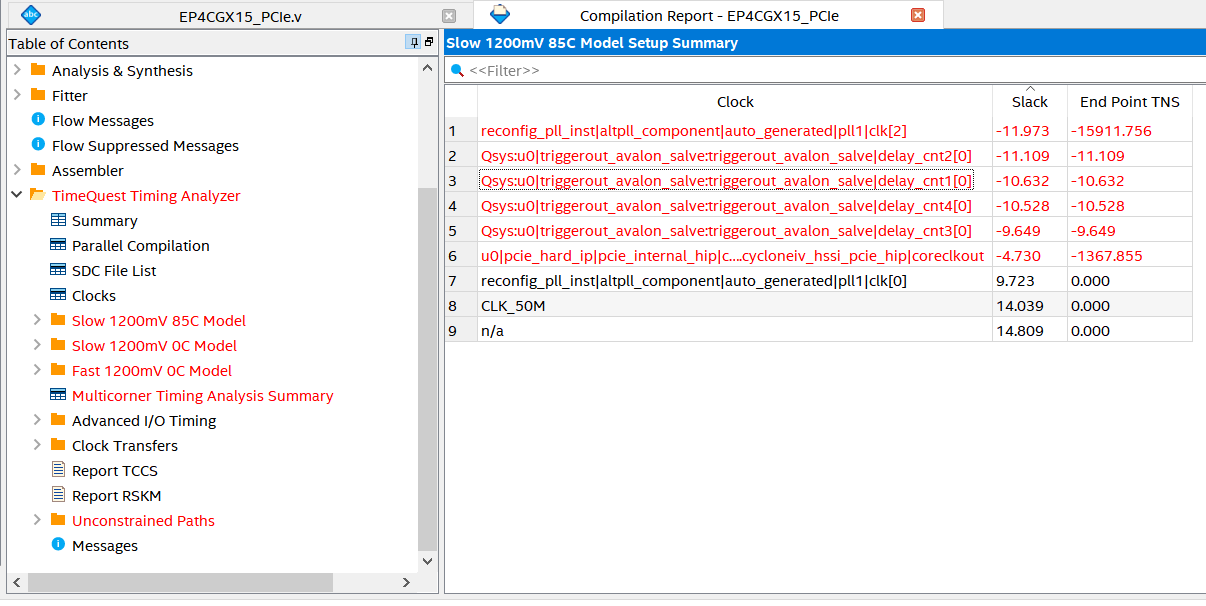

/********************************************************************** * SignalTap导致PCIe Read/Write卡死 * 说明: * 调试PCIe的过程中当FPGA逻辑资源使用率上来之后,发现使用SignalTap * 会导致PCIe读写卡死的问题,经测试,逻辑资源尽量不要超过70%,或者单个IP

* 进行测试。 * * 2018-10-31 深圳 宝安西乡 曾剑锋 *********************************************************************/ 一、参考文档 1. FPGA加入signaltap出现工程不稳定现象。 https://bbs.csdn.net/topics/392065119 二、可能原因: 估计资源用到70%以上了,先砍一些模块下去做signaltap的抓波形。搞完了再把signaltap 去掉模块加回来。他吃资源多了里面的布线就不行了。

浙公网安备 33010602011771号

浙公网安备 33010602011771号