基于FPGA的74ls148设计

1 74ls148简介

74ls148是8线-3线优先编码器,将 8 条数据线(0-7)进行 3 线(4-2-1)二进制(八进制)优先编码,即对最高位数据线进行译码。利用选通端(EI)和输出选通端(EO)可进行八进制扩展。

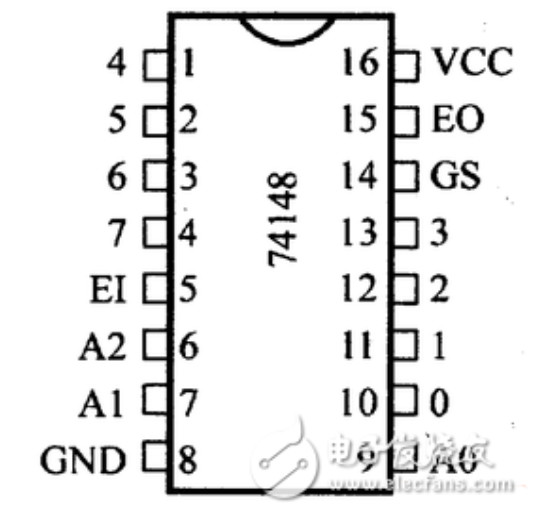

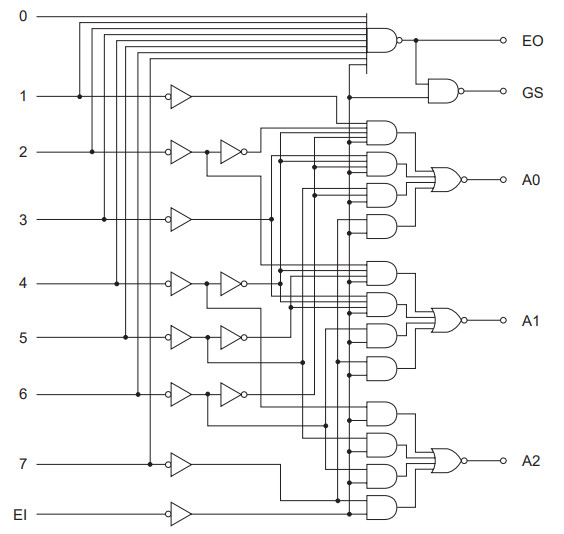

2 74ls148管脚图和逻辑图

管脚介绍

0-7 编码输入端(低电平有效)

EI 选通输入端(低电平有效)

A0、A1、A2 三位二进制编码输出信号即编码输出端(低电平有效)

GS 片优先编码输出端即宽展端(低电平有效)

EO 选通输出端,即使能输出端

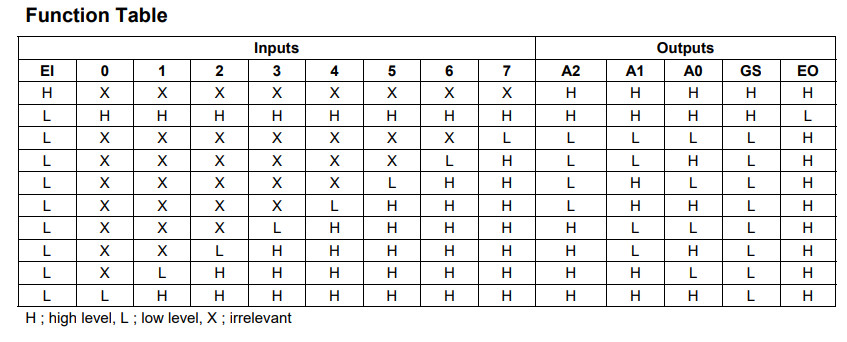

3 74ls148真值表

4 74ls148工作原理

该编码器有8个信号输入端,3个二进制码输出端。此外,电路还设置了输入使能端EI,输出使能端EO和优先编码工作状态标志GS。当EI=0时,编码器工作;而当EI=1时,则不论8个输入端为何种状态,3个输出端均为高电平,且优先标志端和输出使能端均为高电平,编码器处于非工作状态。这种情况被称为输入低电平有效,输出也为低电来有效的情况。当EI为0,且至少有一个输入端有编码请求信号(逻辑0)时,优先编码工作状态标志GS为0。表明编码器处于工作状态,否则为1。

5 74ls148的Verilog设计

1 module ttl_74148( 2 input wire D0,D1,D2,D3,D4,D5,D6,D7, //输入信号,低电平有效 3 input wire EI, //输入使能 4 output reg A0,A1,A2, //输出信号, 5 output reg GS, //优先编码工作状态标志,0表示工作状态 6 output reg EO //输出使能 7 ); 8 9 always@(*)begin 10 if(EI) 11 begin {A2,A1,A0} = 3'b111; GS = 1'b1; EO = 1'b1; end 12 else if({D7,D6,D5,D4,D3,D2,D1,D0} == 8'b1111_1111) 13 begin {A2,A1,A0} = 3'b111; GS = 1'b1; EO = 1'b0; end 14 else if(!D7) 15 begin {A2,A1,A0} = 3'b000; GS = 1'b0; EO = 1'b1; end 16 else if(!D6) 17 begin {A2,A1,A0} = 3'b001; GS = 1'b0; EO = 1'b1; end 18 else if(!D5) 19 begin {A2,A1,A0} = 3'b010; GS = 1'b0; EO = 1'b1; end 20 else if(!D4) 21 begin {A2,A1,A0} = 3'b011; GS = 1'b0; EO = 1'b1; end 22 else if(!D3) 23 begin {A2,A1,A0} = 3'b100; GS = 1'b0; EO = 1'b1; end 24 else if(!D2) 25 begin {A2,A1,A0} = 3'b101; GS = 1'b0; EO = 1'b1; end 26 else if(!D1) 27 begin {A2,A1,A0} = 3'b110; GS = 1'b0; EO = 1'b1; end 28 else 29 begin {A2,A1,A0} = 3'b111; GS = 1'b0; EO = 1'b1; end 30 end 31 32 endmodule

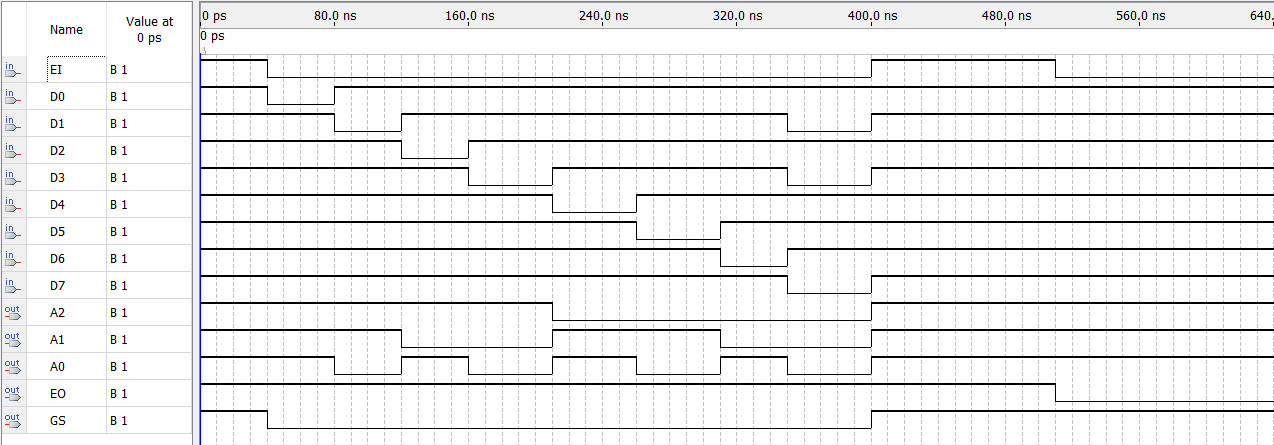

6 波形仿真测试结果

参考资料:

(1)优先编码器74ls148引脚图及功能介绍(工作原理,逻辑图及应用电路) - 电子常识 - 电子发烧友网 (elecfans.com);

浙公网安备 33010602011771号

浙公网安备 33010602011771号