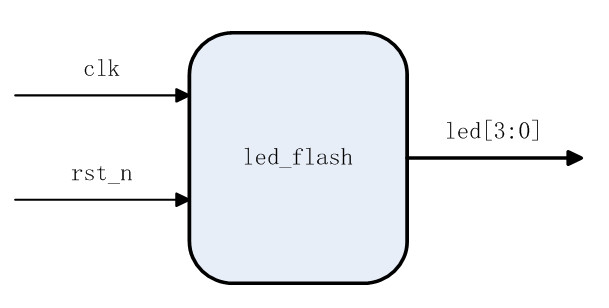

基于FPGA的LED闪烁灯设计

1. 项目介绍

在FPGA上最简单的应用就是点亮一盏闪烁的LED。学过软件的朋友一般都写过“Hello world”,因为这个是最简单的程序。

2. 设计要求

LED灯以2s的周期闪烁,LED灯亮、灭,每1s取反一次,如此循环,不断取反。从而实现LED灯的不断闪烁。

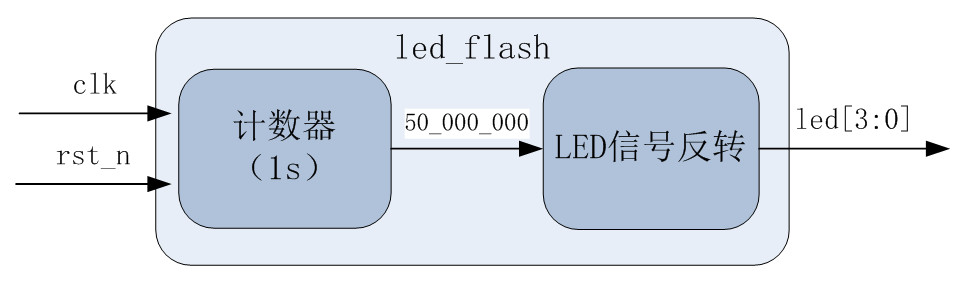

3. 设计分析

从外部晶振(50M)时钟输入,利用计数器去计数1s,然后每隔1s改变一下LED输出引脚的电平状态。 因为开发板晶振为50M,所以一个时钟周期为20ns(1/50MHz),因此计数器cnt通过对50MHz系统时钟计数,计时到1s,需要累加1s/20ns=5000_0000次。

4.具体设计

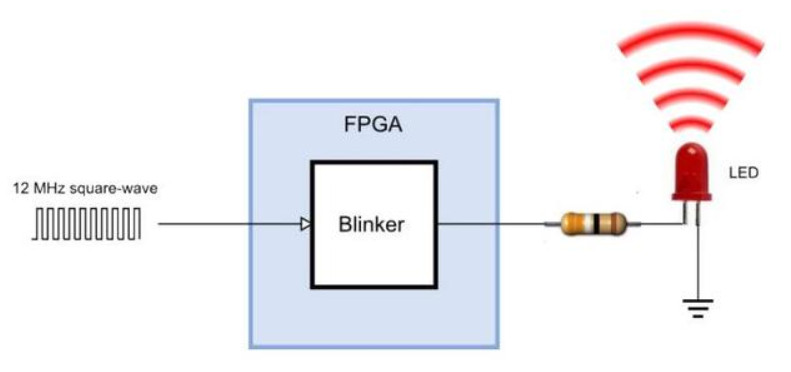

4.1 硬件连接示意图

4.2 架构设计

5. 设计实现

1 module led_flash( 2 input wire clk, 3 input wire rst_n, 4 5 output reg [3:0] led 6 ); 7 8 parameter T_1S = 26'd50_000_000; 9 10 reg [25:0] cnt; 11 12 always@(posedge clk or negedge rst_n)begin 13 if(rst_n == 1'b0) 14 cnt <= 26'd0; 15 else 16 if(cnt < T_1S - 1'b1) 17 cnt <= cnt + 1'b1; 18 else 19 cnt <= 26'd0; 20 end 21 22 always@(posedge clk or negedge rst_n)begin 23 if(rst_n == 1'b0) 24 led <= 4'b0000; 25 else 26 if(cnt == T_1S - 1'b1) 27 led <= ~led; 28 else 29 led <= led; 30 end 31 32 endmodule

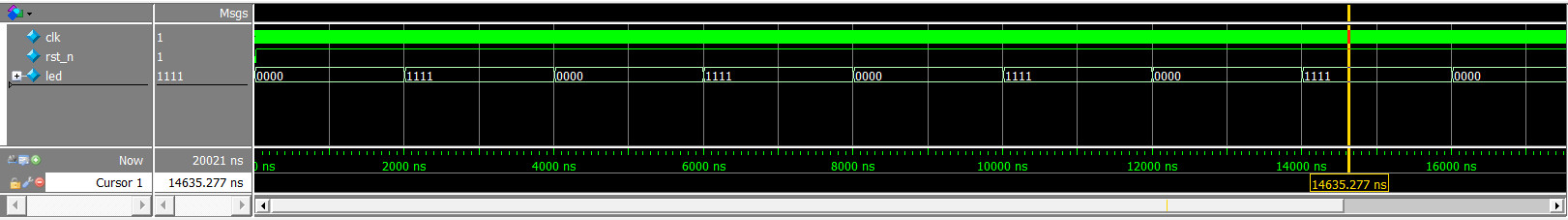

6. 仿真验证

1 `timescale 1ns/1ps 2 3 module led_flash_tb(); 4 5 reg clk; 6 reg rst_n; 7 8 wire [3:0] led; 9 10 defparam led_flash_inst.T_1S = 7'd100; 11 12 led_flash led_flash_inst ( 13 .clk (clk), 14 .rst_n (rst_n), 15 16 .led (led) 17 ); 18 19 initial begin 20 while(2)begin 21 clk = 1'b0; #10; 22 clk = 1'b1; #10; 23 end 24 end 25 26 initial begin 27 rst_n = 1'b0; 28 #21; 29 rst_n = 1'b1; 30 #(2000*10); //必须加括号, 31 $stop; 32 end 33 34 endmodule

7 参考资料

浙公网安备 33010602011771号

浙公网安备 33010602011771号