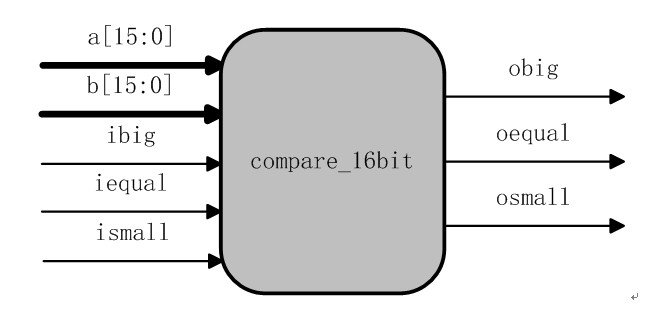

基于FPGA的16位带级联信号数值比较器设计

1.项目介绍

数值比较器就是对两数A、B进行比较,以判断其大小的逻辑电路。

2. 设计要求:

(1)设计一个16位比较器,比较两个数a和b的大小,有三个输出端(大于、小于或等于)。当a大于b,则obig=1,其余为0;当a小于b,则osmall=1,其余为0;当a等于b时,则oequal=1,其余为0。

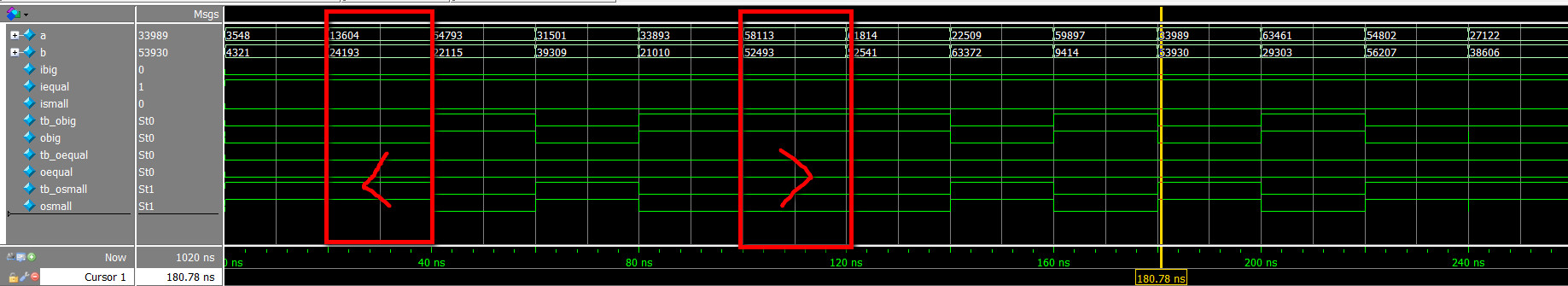

(2)写出测试模块,随机产生两个16位输入数据,每隔20ns产生两个新的随机数,观察仿真波形,并对仿真波形做分析,说明设计的正确性。

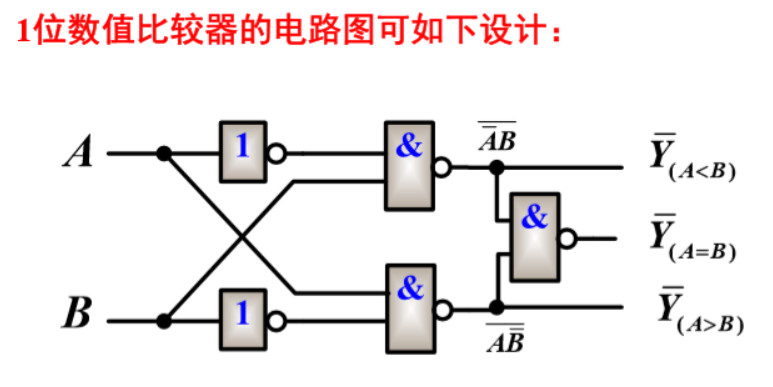

3.实验原理

在比较两个多位数的大小时,必须自高而低的逐位比较,而且只有在高位相等时,才需比较较低位。该设计命名为compare_16bit,a[15:0]和b[15:0]为比较数值,ibig (A>B)、iequal(A=B)、ismall(A<B)为级联信号,用来将高位的结果与低位级联,即接收来自高位比较器的输出结果。若级联信号ibig(A>B)==1或者ismall(A<B)==1,即高位不相等,则无需比较低位;若级联信号iequal(A=B)==1,最终结果取决于低位结果。

4. 设计实现

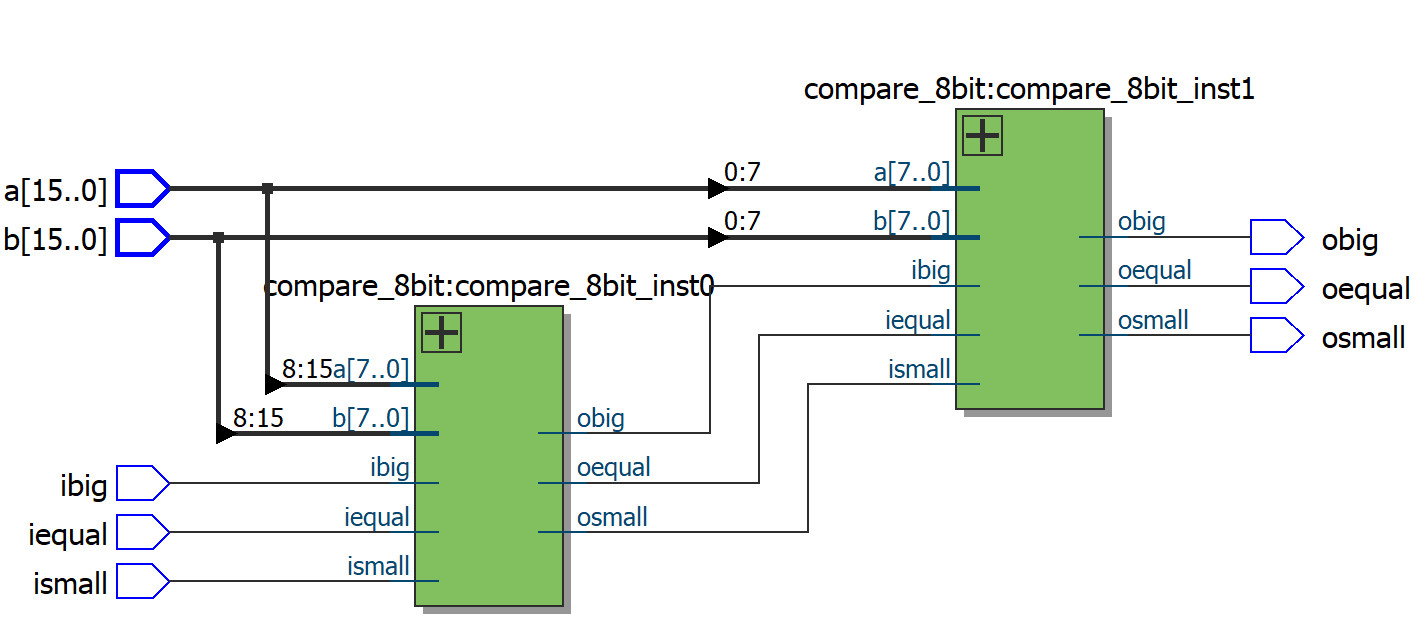

(1)16位数据比较器由2个8位数据比较器构成

1 module compare_16bit( 2 3 input wire [15:0] a, 4 input wire [15:0] b, 5 input wire ibig, 6 input wire iequal, 7 input wire ismall, 8 9 output wire obig, 10 output wire oequal, 11 output wire osmall 12 ); 13 14 wire obig8; 15 wire oequal8; 16 wire osmall8; 17 18 19 compare_8bit compare_8bit_inst0( 20 21 .a (a[15:8]), 22 .b (b[15:8]), 23 .ibig (ibig), 24 .iequal (iequal), 25 .ismall (ismall), 26 27 .obig (obig8), 28 .oequal (oequal8), 29 .osmall (osmall8) 30 ); 31 32 compare_8bit compare_8bit_inst1( 33 34 .a (a[7:0]), 35 .b (b[7:0]), 36 .ibig (obig8), 37 .iequal (oequal8), 38 .ismall (osmall8), 39 40 .obig (obig), 41 .oequal (oequal), 42 .osmall (osmall) 43 ); 44 45 endmodule

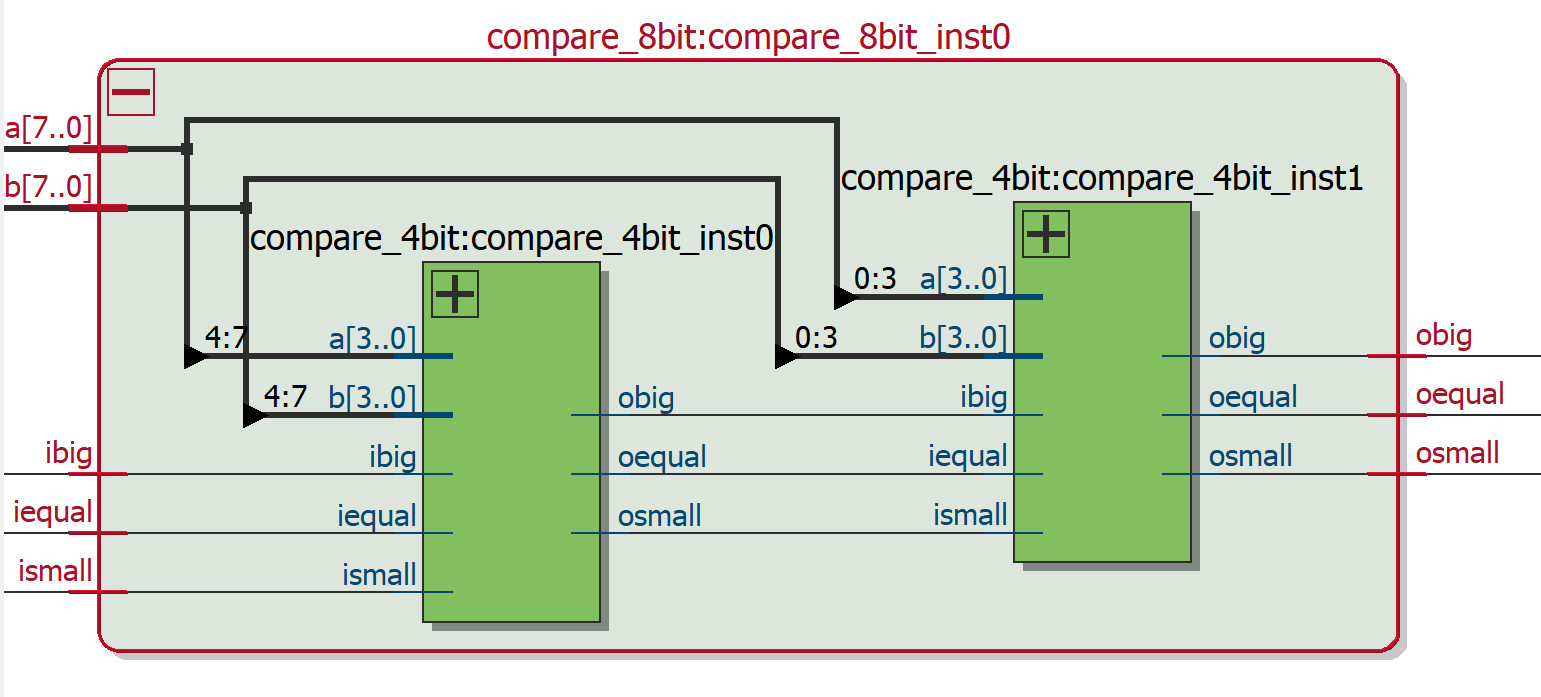

(2)8位数值比较器由2个4位数据比较器构成

1 module compare_8bit( 2 3 input wire [7:0] a, 4 input wire [7:0] b, 5 input wire ibig, 6 input wire iequal, 7 input wire ismall, 8 9 output wire obig, 10 output wire oequal, 11 output wire osmall 12 ); 13 14 wire obig4; 15 wire oequal4; 16 wire osmall4; 17 18 compare_4bit compare_4bit_inst0( 19 20 .a (a[7:4]), 21 .b (b[7:4]), 22 .ibig (ibig), 23 .iequal (iequal), 24 .ismall (ismall), 25 26 .obig (obig4), 27 .oequal (oequal4), 28 .osmall (osmall4) 29 ); 30 31 compare_4bit compare_4bit_inst1( 32 33 .a (a[3:0]), 34 .b (b[3:0]), 35 .ibig (obig4), 36 .iequal (oequal4), 37 .ismall (osmall4), 38 39 .obig (obig), 40 .oequal (oequal), 41 .osmall (osmall) 42 ); 43 44 endmodule

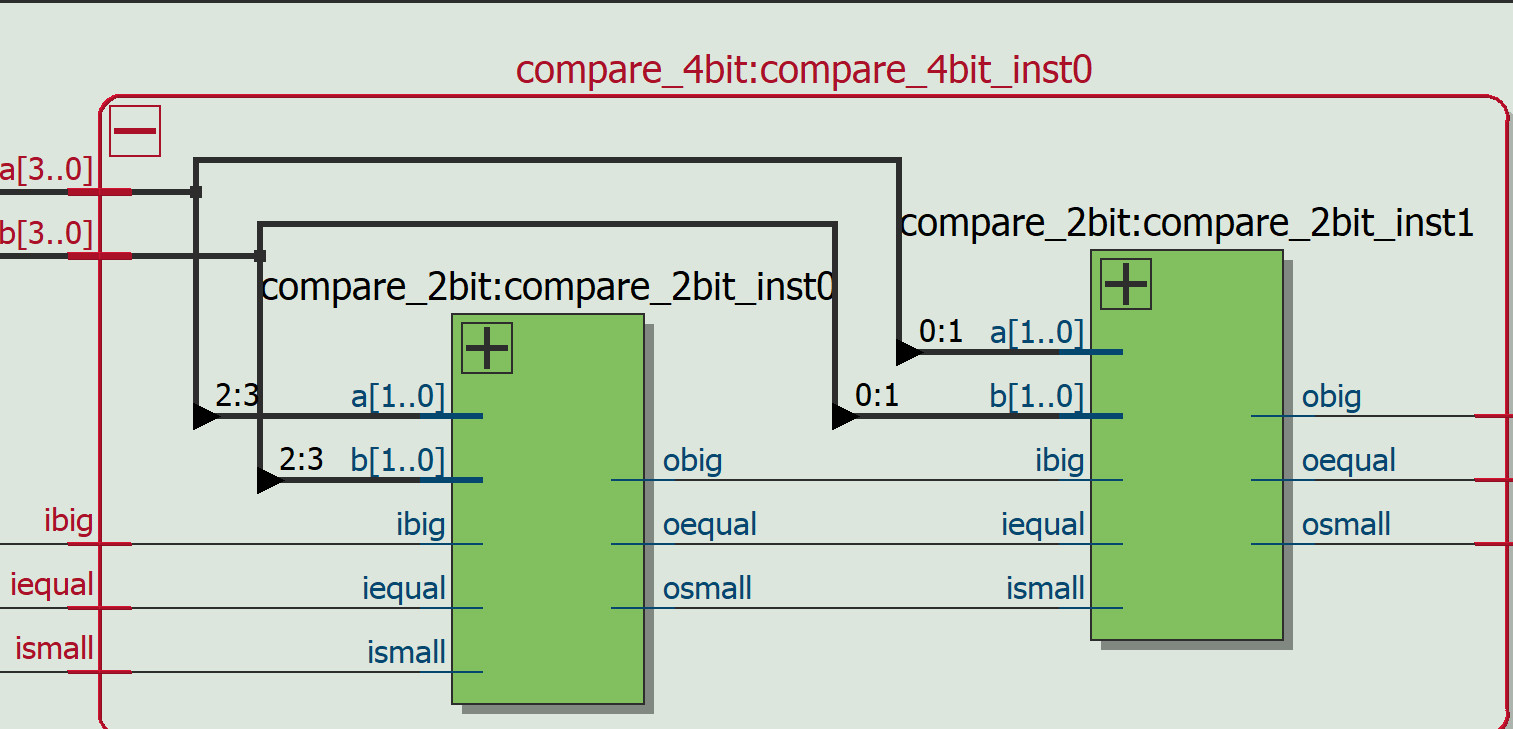

(3)4位数值比较器由2个2位数据比较器构成

1 module compare_4bit( 2 3 input wire [3:0] a, 4 input wire [3:0] b, 5 input wire ibig, 6 input wire iequal, 7 input wire ismall, 8 9 output wire obig, 10 output wire oequal, 11 output wire osmall 12 ); 13 14 wire obig2; 15 wire oequal2; 16 wire osmall2; 17 18 19 compare_2bit compare_2bit_inst0( 20 21 .a (a[3:2]), 22 .b (b[3:2]), 23 .ibig (ibig), 24 .iequal (iequal), 25 .ismall (ismall), 26 27 .obig (obig2), 28 .oequal (oequal2), 29 .osmall (osmall2) 30 ); 31 32 compare_2bit compare_2bit_inst1( 33 34 .a (a[1:0]), 35 .b (b[1:0]), 36 .ibig (obig2), 37 .iequal (oequal2), 38 .ismall (osmall2), 39 40 .obig (obig), 41 .oequal (oequal), 42 .osmall (osmall) 43 ); 44 45 endmodule

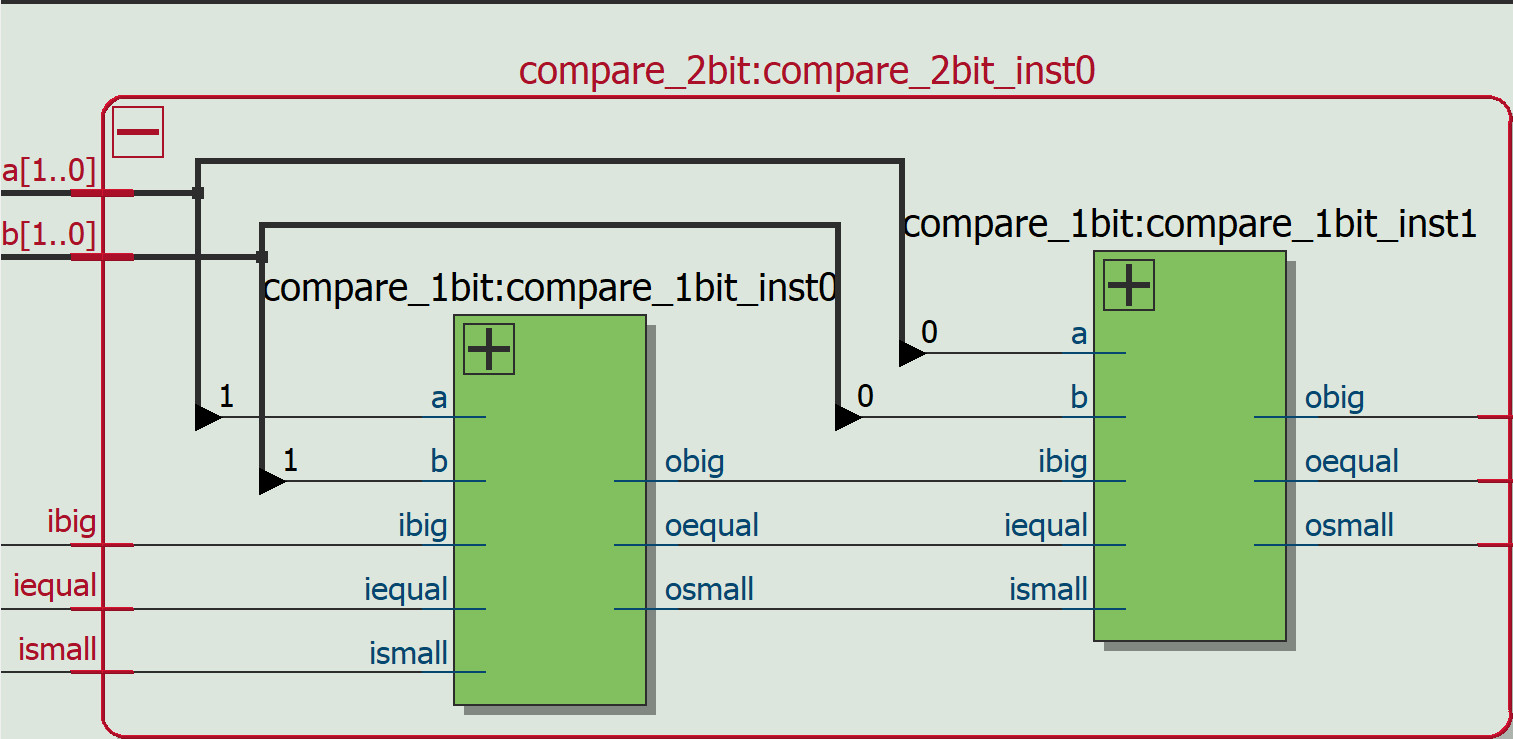

(4)2位数值比较器由2个1位数据比较器构成

1 module compare_2bit( 2 3 input wire [1:0] a, 4 input wire [1:0] b, 5 input wire ibig, 6 input wire iequal, 7 input wire ismall, 8 9 output wire obig, 10 output wire oequal, 11 output wire osmall 12 ); 13 14 wire obig_reg; 15 wire oequal_reg; 16 wire osmall_reg; 17 18 19 compare_1bit compare_1bit_inst0( 20 21 .a (a[1]), 22 .b (b[1]), 23 .ibig (ibig), 24 .iequal (iequal), 25 .ismall (ismall), 26 27 .obig (obig_reg), 28 .oequal (oequal_reg), 29 .osmall (osmall_reg) 30 ); 31 32 compare_1bit compare_1bit_inst1( 33 34 .a (a[0]), 35 .b (b[0]), 36 .ibig (obig_reg), 37 .iequal (oequal_reg), 38 .ismall (osmall_reg), 39 40 .obig (obig), 41 .oequal (oequal), 42 .osmall (osmall) 43 ); 44 45 endmodule

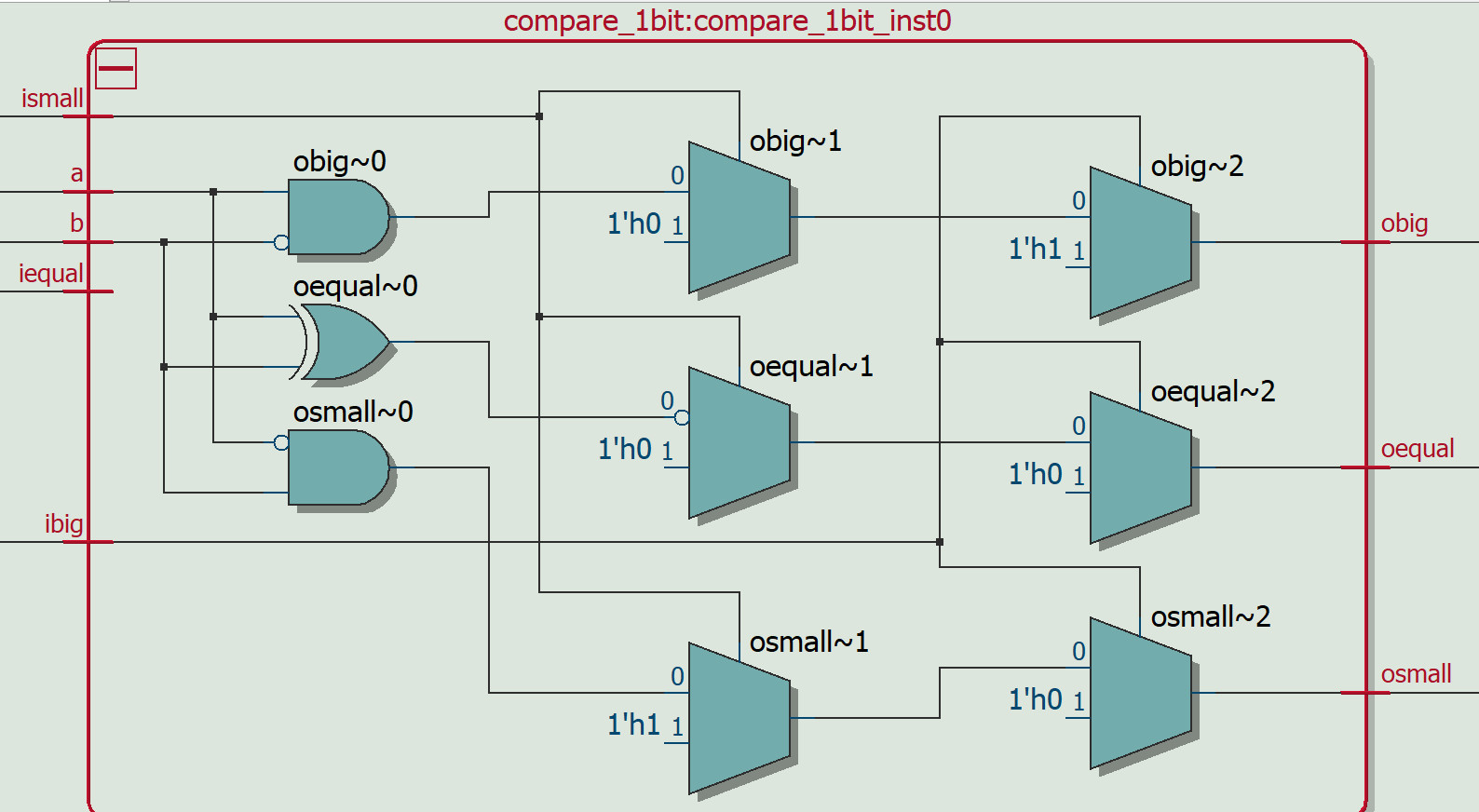

(5)1位带级联信号的数值比较器

1 module compare_1bit( 2 3 input wire a, 4 input wire b, 5 input wire ibig, 6 input wire iequal, 7 input wire ismall, 8 9 output reg obig, 10 output reg oequal, 11 output reg osmall 12 ); 13 14 always@(*)begin 15 if(ibig == 1'b1) 16 obig = 1'b1; 17 else 18 if(ismall == 1'b1) 19 obig = 1'b0; 20 else 21 obig = a & (~b); 22 end 23 24 always@(*)begin 25 if(ibig == 1'b1) 26 oequal = 1'b0; 27 else 28 if(ismall == 1'b1) 29 oequal = 1'b0; 30 else 31 oequal = ~(a ^ b); 32 end 33 34 always@(*)begin 35 if(ibig == 1'b1) 36 osmall = 1'b0; 37 else 38 if(ismall == 1'b1) 39 osmall = 1'b1; 40 else 41 osmall = (~a) & b; 42 end 43 44 endmodule

4. 验证仿真

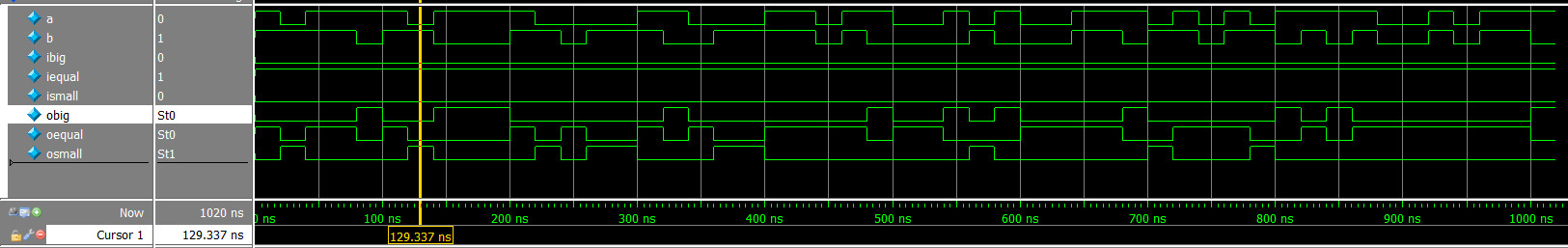

(1)1位带级联信号的数值比较器(不考虑高位影响,假设高位都相等)

1 `timescale 1ns/1ps 2 3 module compare_1bit_tb(); 4 5 reg a; 6 reg b; 7 reg ibig; 8 reg iequal; 9 reg ismall; 10 11 wire obig; 12 wire oequal; 13 wire osmall; 14 15 16 compare_1bit compare_1bit_inst( 17 18 .a (a), 19 .b (b), 20 .ibig (ibig), 21 .iequal (iequal), 22 .ismall (ismall), 23 24 .obig (obig), 25 .oequal (oequal), 26 .osmall (osmall) 27 ); 28 29 initial begin 30 a = 1'b1; b = 1'b1; 31 ibig = 1'b0; iequal = 1'b1; ismall = 1'b0; //不考虑高位的影响 32 #20; 33 repeat(50)begin 34 a = {$random}%2; b = {$random}%2; 35 ibig = 1'b0; iequal = 1'b1; ismall = 1'b0; 36 #20; 37 end 38 end 39 40 endmodule

(2)16位带级联信号的数值比较器

1 `timescale 1ns/1ps 2 3 module compare_16bit_tb(); 4 5 reg [15:0] a; 6 reg [15:0] b; 7 reg ibig; 8 reg iequal; 9 reg ismall; 10 11 wire obig; 12 wire oequal; 13 wire osmall; 14 15 wire tb_obig; 16 wire tb_oequal; 17 wire tb_osmall; 18 19 assign tb_obig = a > b; 20 assign tb_oequal = a == b; 21 assign tb_osmall = a < b; 22 23 compare_16bit compare_16bit_inst( 24 25 .a (a), 26 .b (b), 27 .ibig (ibig), 28 .iequal (iequal), 29 .ismall (ismall), 30 31 .obig (obig), 32 .oequal (oequal), 33 .osmall (osmall) 34 ); 35 36 initial begin 37 a = 16'd3548; b = 16'd4321; 38 ibig = 1'b0; iequal = 1'b1; ismall = 1'b0; //不考虑高位的影响 39 #20; 40 repeat(50)begin 41 a = {$random}%65536; b = {$random}%65536; 42 ibig = 1'b0; iequal = 1'b1; ismall = 1'b0; 43 #20; 44 end 45 end 46 47 endmodule

5. 参考资料

浙公网安备 33010602011771号

浙公网安备 33010602011771号