基于FPGA的4选1多路选择器设计

1. 设计要求:

设计一个4选1多路选择器,数据输入有四个,分别是dataa、datab、datac和datad,还需要一个选择端sel。因为输入有四路数据,选择端要求能够表现出四种状态,因而选择端位宽为2bit。

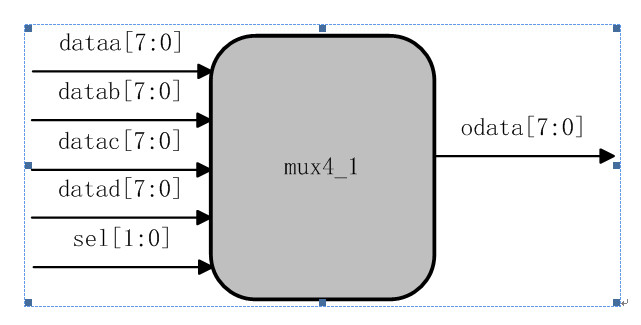

假设dataa、datab、datac和datad都是位宽为8bit的数据,当sel为00时,选择dataa通过;当sel为01时,选择datab通过;当sel为10时,选择datac通过;当sel为11时,选择datad通过。其系统框图如下所示:

根据组合逻辑设计规则,将所有的情况全部列出,得出真值表,进而得到布尔表达式。但是现在输入的组合排列太多了(2的34次幂),不能够直接得出真值表。

2. 设计实现

(1)将输入为8的四选一多路选择器,拆分为8个位宽为1的四选一多路选择器,首先列出位宽为1真值表,得出位宽为1的四选一多路选择器。然后并接八个即可。

1 module mux4_1_8bit( 2 3 input wire [7:0] dataa, 4 input wire [7:0] datab, 5 input wire [7:0] datac, 6 input wire [7:0] datad, 7 input wire [1:0] sel, 8 9 output wire [7:0] odata 10 ); 11 12 mux4_1_bit mux4_1_bit_inst0( 13 14 .dataa (dataa[0]), 15 .datab (datab[0]), 16 .datac (datac[0]), 17 .datad (datad[0]), 18 .sel (sel), 19 .odata (odata[0]) 20 21 ); 22 23 mux4_1_bit mux4_1_bit_inst1( 24 25 .dataa (dataa[1]), 26 .datab (datab[1]), 27 .datac (datac[1]), 28 .datad (datad[1]), 29 .sel (sel), 30 .odata (odata[1]) 31 32 ); 33 34 mux4_1_bit mux4_1_bit_inst2( 35 36 .dataa (dataa[2]), 37 .datab (datab[2]), 38 .datac (datac[2]), 39 .datad (datad[2]), 40 .sel (sel), 41 .odata (odata[2]) 42 43 ); 44 45 mux4_1_bit mux4_1_bit_inst3( 46 47 .dataa (dataa[3]), 48 .datab (datab[3]), 49 .datac (datac[3]), 50 .datad (datad[3]), 51 .sel (sel), 52 .odata (odata[3]) 53 54 ); 55 56 mux4_1_bit mux4_1_bit_inst4( 57 58 .dataa (dataa[4]), 59 .datab (datab[4]), 60 .datac (datac[4]), 61 .datad (datad[4]), 62 .sel (sel), 63 .odata (odata[4]) 64 65 ); 66 67 mux4_1_bit mux4_1_bit_inst5( 68 69 .dataa (dataa[5]), 70 .datab (datab[5]), 71 .datac (datac[5]), 72 .datad (datad[5]), 73 .sel (sel), 74 .odata (odata[5]) 75 76 ); 77 78 mux4_1_bit mux4_1_bit_inst6( 79 80 .dataa (dataa[6]), 81 .datab (datab[6]), 82 .datac (datac[6]), 83 .datad (datad[6]), 84 .sel (sel), 85 .odata (odata[6]) 86 87 ); 88 89 mux4_1_bit mux4_1_bit_inst7( 90 91 .dataa (dataa[7]), 92 .datab (datab[7]), 93 .datac (datac[7]), 94 .datad (datad[7]), 95 .sel (sel), 96 .odata (odata[7]) 97 98 ); 99 100 endmodule

1 module mux4_1_bit( 2 3 input wire dataa, 4 input wire datab, 5 input wire datac, 6 input wire datad, 7 input wire [1:0] sel, 8 9 output reg odata 10 ); 11 12 always@(*)begin 13 case(sel) 14 2'b00 : odata = dataa; 15 2'b01 : odata = datab; 16 2'b10 : odata = datac; 17 2'b11 : odata = datad; 18 default : odata = dataa; 19 endcase 20 end 21 22 endmodule

1 `timescale 1ns/1ps 2 3 module mux4_1_8bit_tb(); 4 5 reg [7:0] dataa; 6 reg [7:0] datab; 7 reg [7:0] datac; 8 reg [7:0] datad; 9 reg [1:0] sel; 10 11 wire [7:0] odata; 12 13 14 mux4_1_8bit mux4_1_8bit_inst( 15 .dataa (dataa), 16 .datab (datab), 17 .datac (datac), 18 .datad (datad), 19 .sel (sel), 20 .odata (odata) 21 ); 22 23 initial begin 24 repeat(10)begin 25 dataa = {$random} % 256; 26 datab = {$random} % 256; 27 datac = {$random} % 256; 28 datad = {$random} % 256; 29 sel = {$random} % 4; 30 #20; 31 end 32 end 33 34 endmodule

(2)根据verilog的设计规则,可以直接描述逻辑功能,而不用描述门电路。这种设计规则有利于将设计做的比较大。

1 module mux4_1( 2 3 input wire [7:0] dataa, 4 input wire [7:0] datab, 5 input wire [7:0] datac, 6 input wire [7:0] datad, 7 input wire [1:0] sel, 8 9 output reg [7:0] odata 10 ); 11 12 always@(*)begin 13 case(sel) 14 2'b00 : odata = dataa; 15 2'b01 : odata = datab; 16 2'b10 : odata = datac; 17 2'b11 : odata = datad; 18 default : odata = dataa; 19 endcase 20 end 21 22 endmodule

1 `timescale 1ns/1ps 2 3 module mux4_1_tb(); 4 5 reg [7:0] dataa; 6 reg [7:0] datab; 7 reg [7:0] datac; 8 reg [7:0] datad; 9 reg [1:0] sel; 10 11 wire [7:0] odata; 12 13 14 mux4_1 mux4_1_inst( 15 .dataa (dataa), 16 .datab (datab), 17 .datac (datac), 18 .datad (datad), 19 .sel (sel), 20 .odata (odata) 21 ); 22 23 initial begin 24 repeat(10)begin 25 dataa = {$random} % 256; 26 datab = {$random} % 256; 27 datac = {$random} % 256; 28 datad = {$random} % 256; 29 sel = {$random} % 4; 30 #20; 31 end 32 end 33 34 endmodule

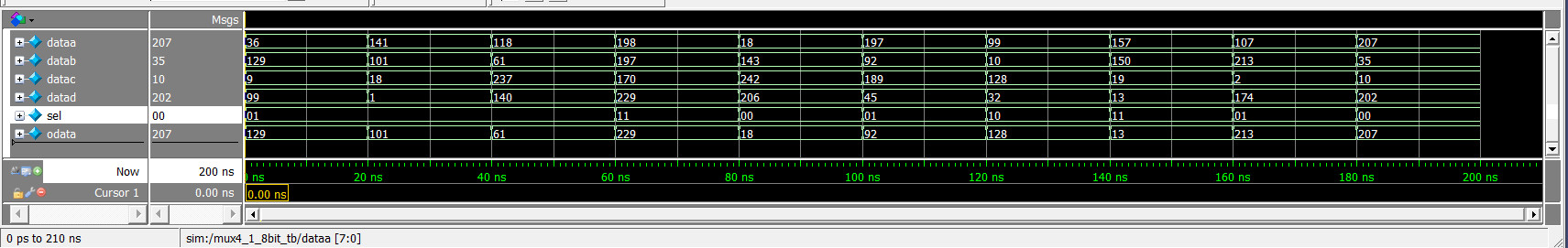

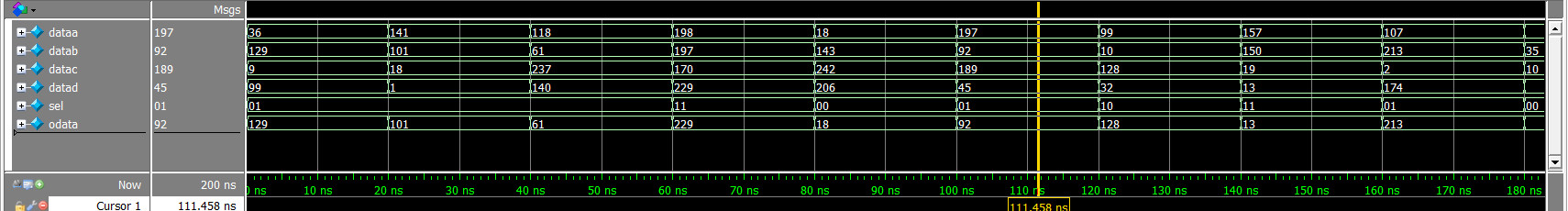

备注:由于本次输入的的组合太多,不能全覆盖测试。故采用随机数来进行测试。

浙公网安备 33010602011771号

浙公网安备 33010602011771号