基于FPGA的2选1多路选择器设计

1. 项目介绍

多路选择器,也叫数据选择器或多路开关,在多路数据传送过程中,能够根据需要将其中任意一路选出来的电路。数据选择器用于控制有效数据的输出,能够通过地址选择线来选定相应的通道作为输出,提高了数据的传输效率。(数据分配器用于数据的传输途径,在信号传输过程中能够通过地址选择线选择传输信道)。

2. 设计要求

设计一个2选1多路选择器,输入有两个单bit信号,和一个单bit的选择信号。当选择信号为低电平时,将第一路信号输出,当选择信号为高电平时,将第二路信号输出。

3. 设计原理

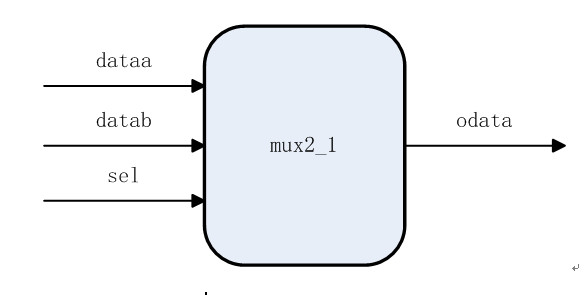

该设计命名为mux2_1,第一路信号命名为dataa,第二路信号命名为datab,选择信号命名为sel,输出信号命名为odata,系统框图如下图所示。

根据设计要求,得真值表:

| dataa | datab | sel | odata |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

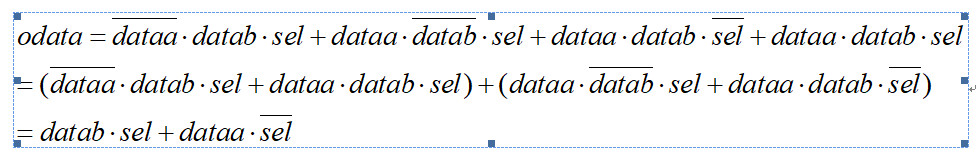

根据真值表,得到逻辑表达式:

转化为Verilog表达式为

Odata = datab&sel | dataa&(~sel);

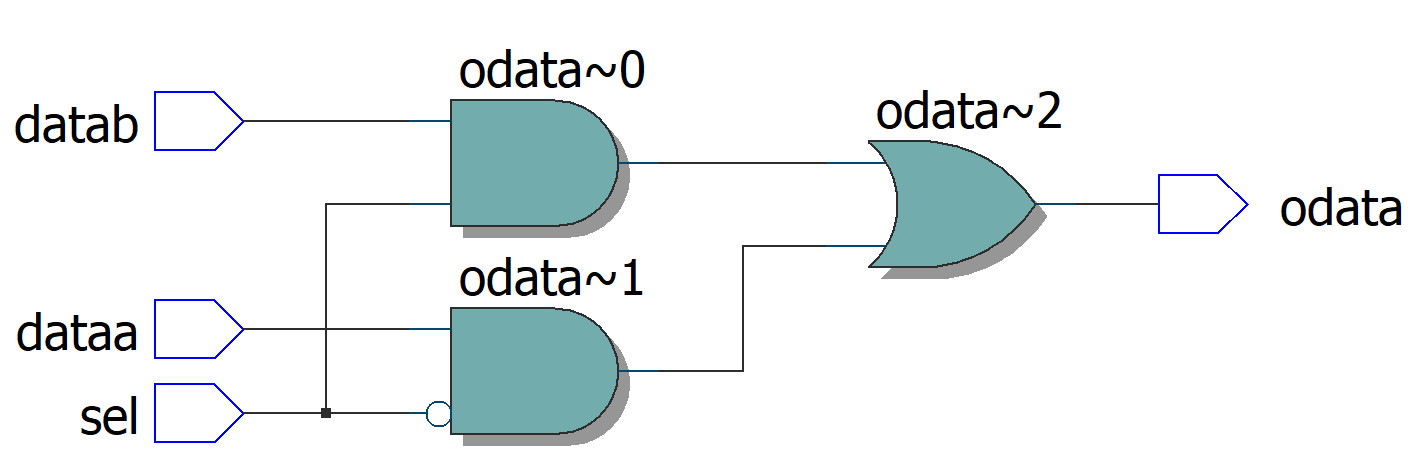

4. 设计实现

1 module mux2_1( 2 3 input wire dataa, 4 input wire datab, 5 input wire sel, 6 7 output wire odata 8 ); 9 10 assign odata = (datab & sel) | (dataa & (~sel)); 11 12 endmodule

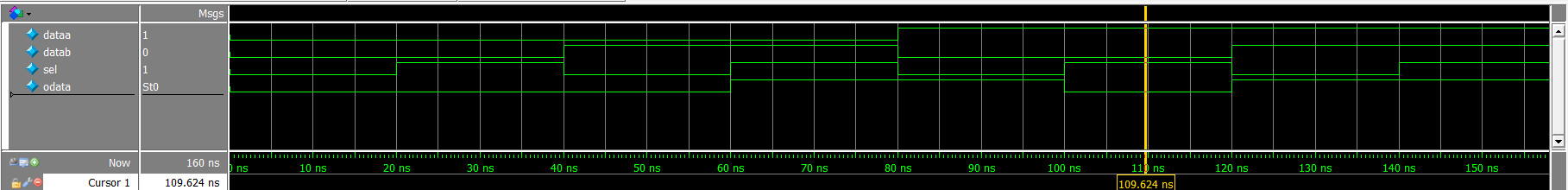

5. 仿真验证

1 `timescale 1ns/1ps 2 3 module mux2_1_tb(); 4 5 reg dataa; 6 reg datab; 7 reg sel; 8 9 wire odata; 10 11 mux2_1 mux2_1_inst( 12 .dataa (dataa), 13 .datab (datab), 14 .sel (sel), 15 .odata (odata) 16 ); 17 18 initial begin 19 dataa = 1'b0; datab = 1'b0; sel = 1'b0; #20; 20 dataa = 1'b0; datab = 1'b0; sel = 1'b1; #20; 21 dataa = 1'b0; datab = 1'b1; sel = 1'b0; #20; 22 dataa = 1'b0; datab = 1'b1; sel = 1'b1; #20; 23 dataa = 1'b1; datab = 1'b0; sel = 1'b0; #20; 24 dataa = 1'b1; datab = 1'b0; sel = 1'b1; #20; 25 dataa = 1'b1; datab = 1'b1; sel = 1'b0; #20; 26 dataa = 1'b1; datab = 1'b1; sel = 1'b1; #20; 27 end 28 29 endmodule

参考资料:

浙公网安备 33010602011771号

浙公网安备 33010602011771号